Fターム[5F083ZA14]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリと独立機能ブロック (1,941) | メモリ部+メモリ部(異種) (302)

Fターム[5F083ZA14]に分類される特許

61 - 80 / 302

半導体装置及びその試験方法

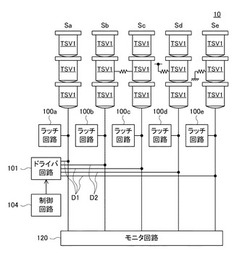

【課題】論理値の反転処理を行う回路をコアチップ側に設けることなく、TSVを含む電流パスラインのショート不良を検出する。

【解決手段】半導体装置10は、第1及び第2の電流パスSa,Sbと、これらとそれぞれ電気的に接続する第1及び第2のラッチ回路100a,100bと、第1のラッチ回路100aに第1のデータD1を供給するとともに、第2のラッチ回路100bに第1のデータとは逆の論理値を有する第2のデータD2を供給するドライバ回路101と、第1のデータD1が第1のラッチ回路100aに供給され、かつ第2のデータD2が第2のラッチ回路100bに供給されない第1の期間と、第2のデータD2が第2のラッチ回路100bに供給され、かつ第1のデータD1が第1のラッチ回路100aに供給されない第2の期間と、が交互に繰り返されるよう、ドライバ回路101を制御する制御回路104と、モニタ回路120とを備える。

(もっと読む)

不揮発性メモリ装置

【課題】一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供することによって、読出しマージン減少による信頼性の下落を防止できる不揮発性メモリ装置が提供される。

【解決手段】本発明の実施形態による不揮発性メモリ装置は、基板と直交する方向に積層された複数のメモリセルを含むメモリセルアレイと、ワードラインを通じて前記メモリセルアレイに連結された行選択回路と、前記ワードラインに提供される電圧を発生する電圧発生回路と、を含み、前記電圧発生回路は、目標電圧レベルまで段階的に増加させる方式に前記電圧を発生する。本発明の実施形態による不揮発性メモリ装置は、一定の上昇傾斜を有する駆動信号をメモリセルアレイに提供できる。したがって、読出しマージン減少による信頼性の下落が防止され得る。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】データ消失温度が高く、かつ生産性の高い不揮発性記憶装置およびその製造方法を提供することである。

【解決手段】実施形態に係る不揮発性記憶装置の製造方法は、第1の記憶部と、第1の記憶部が有するデータ消失温度よりも高いデータ消失温度を有する第2の記憶部と、を有する不揮発性記憶装置の製造方法であって、第2の記憶部のメモリセルを形成するための第2の積層体を形成する工程と、第1の記憶部が形成される領域に形成された第2の積層体を除去する工程と、第1の記憶部のメモリセルを形成するための第1の積層体を形成する工程と、第2の記憶部が形成される領域に形成された第1の積層体を除去する工程と、第1の記憶部が形成される領域に形成された第1の積層体と、第2の記憶部が形成される領域に形成された第2の積層体と、を同時に処理して、第1の積層体から第1の記憶部のメモリセルを形成するとともに、第2の積層体から第2の記憶部のメモリセルを形成する工程と、を備えている。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】ノイズによるデータ信号への影響を抑制する半導体記憶装置を提供する。

【解決手段】記憶回路を具備し、記憶回路は、それぞれが電界効果トランジスタであり、1個目の電界効果トランジスタ111a−1のソース及びドレインの一方にデジタルデータ信号が入力され、k個目(kは2以上n(nは2以上の自然数)以下の自然数)の電界効果トランジスタのソース及びドレインの一方がk−1個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続されるn個の電界効果トランジスタと、それぞれ一対の電極を有し、m個目(mはn以下の自然数)の容量素子の一対の電極の一方が、n個の電界効果トランジスタのうち、m個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続され、少なくとも2つの容量素子における容量値が異なるn個の容量素子112aー1〜112aーnとを備える。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、水素または希ガスのいずれかの元素が添加されている。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】高速動作可能な半導体装置を提供する。また、短チャネル効果による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】トランジスタの半導体層に結晶性を有する酸化物半導体を用い、該半導体層にチャネル形成領域とソース領域とドレイン領域を形成する。ソース領域及びドレイン領域は、ゲート電極をマスクとして、半導体層に第15族元素のうち一種類または複数種類の元素を添加する自己整合プロセスにより形成する。ソース領域及びドレイン領域に、ウルツ鉱型の結晶構造を付与することができる。

(もっと読む)

不揮発性記憶素子及びその製造方法

【課題】 信頼性を向上可能な不揮発性記憶素子及びその製造方法を提供する。

【解決手段】 不揮発性素子は、基板100、基板100の上に形成され、制御ベースゲート120a及び制御ベースゲート120aの上に形成される制御金属ゲート125anを有する制御ゲート電極137、制御ゲート電極137と基板100との間に形成される電荷格納領域110a、制御ゲート電極137の上に形成される制御ゲートマスクパターン130、及び制御ゲートマスクパターン130及び制御ベースゲート120aの間に形成された制御金属ゲート125aの側壁の上に形成される酸化防止スペーサ135aを備える。このとき、制御金属ゲート125anの幅は、制御ゲートマスクパターン130の幅より小さくなるように形成されている。これにより、制御金属ゲート125anが酸化工程又は酸化物等によって酸化されることを防止することができる。

(もっと読む)

3次元半導体記憶素子

【課題】優れた信頼性を有し、高集積化のために最適化された3次元半導体記憶素子が提供される。

【解決手段】本発明の素子によれば、積層構造体が基板上に配置されて第1の方向に延長される。積層構造体は交互に反復的に積層されたゲートパターン及び絶縁パターンを含む。垂直形活性パターンが積層構造体を貫通する。積層構造体は第1の部分及び第2の部分を含み、積層構造体の第2の部分は第1の方向と垂直である第2の方向に第1の部分より小さい幅を有する。積層構造体の第2の部分の横にストラッピングコンタクトプラグが配置されて、共通ソース領域と接触される。

(もっと読む)

不揮発性メモリー装置の製造方法

【課題】不揮発性メモリー装置の製造方法であって、特に半導体パターン厚さの均一性が向上される3次元半導体装置の製造方法、及び当該製造方法によって製造された3次元半導体装置を提供する。

【解決手段】この製造方法は、基板10の上に複数の第1の膜(鋳型膜)120及び複数の第2の膜(犠牲膜)が交互に積層された積層膜構造体を形成する段階、積層膜構造体を貫通する開口部、及び開口部周囲にアンダーカット領域を形成する段階、アンダーカット領域に局所的に配置される絶縁スペーサー155を形成する段階、絶縁スペーサー155が形成された開口部内に半導体パターン165を形成する段階を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物の偏析に起因する、ドレイン領域と空乏層との間のリーク電流の発生を抑制することが可能な半導体素子を含む半導体装置を提供する。

【解決手段】本半導体装置は、主表面を有する半導体基板SUBと、主表面上に形成された、論理回路を構成するコアトランジスタと、入出力回路を構成するI/Oトランジスタとを備える。主表面からI/On型トランジスタのn型不純物領域NRの最下部までの距離は、主表面からコアn型トランジスタのn型不純物領域NRの最下部までの距離より長い。主表面からI/Op型トランジスタのp型不純物領域PRの最下部までの距離は、主表面からコアp型トランジスタのp型不純物領域の最下部までの距離より長い。主表面からI/On型トランジスタのn型不純物領域の最下部までの距離は、主表面からI/Op型トランジスタのp型不純物領域の最下部までの距離より長い。

(もっと読む)

メモリ装置

【課題】空きソケットとなっている第2ソケットでの信号の反射を抑制可能なメモリ装置を提供する。

【解決手段】メモリモジュール2が接続されたソケット3と、空きソケットとなっているソケット4と、コントローラ5とは、接続配線6によって接続されている。接続配線6は、ソケット3とコントローラ5とを接続する配線6aと、配線6aから分岐点6bで分岐しソケット4と接続する配線6cと、を備える。配線6cには、ダミー配線7の一端7aが接続され、ダミー配線7の他端7bは、終端抵抗8に接続されている。

(もっと読む)

複合メモリ

【課題】 製造コストの上昇を招くことなくNANDフラッシュメモリにDRAMを混載することができ、且つチップ面積の増大を招くことなくシステム性能の向上をはかる。

【解決手段】 半導体基板10上に、NANDセルユニットからなる第1のメモリセルアレイとDRAMセルからなる第2のメモリセルアレイとを搭載した複合メモリであって、NANDセルユニットは、第1のゲート14と第2のゲート16を積層した2層ゲート構成の不揮発性メモリセル100と不揮発性メモリセル100の第1及び第2のゲート14,16間を接続した選択トランジスタ200で構成され、DRAMセルは、選択トランジスタ200と同じ構成のセルトランジスタ300と、不揮発性メモリセル100又は選択トランジスタ200と同じ構成のMOSキャパシタ400で構成されている。

(もっと読む)

半導体記憶装置、及び半導体記憶装置の製造方法

【課題】半導体記憶装置の面積を縮小する技術を提供する。

【解決手段】高抵抗付加型ラッチ回路(12)と、その高抵抗付加型ラッチ回路(12)に保持されるデータの読み出しと書込みとを制御する選択回路(13)とを具備する半導体記憶装置(11)を構成する。その高抵抗付加型ラッチ回路(12)は、第1駆動トランジスタ(22)と、第2駆動トランジスタ(24)と、第1抵抗(121)と、第2抵抗(123)とを備えることが好ましい。また、その選択回路(13)は、第1選択トランジスタ(31)と、第2選択トランジスタ(32)とを備えることが好ましい。ここにおいて、その第1抵抗(121)と第2抵抗(123)とは、サイドウォール状の導電性材料(21)(23)で形成されるものである。

(もっと読む)

不揮発性記憶装置

【課題】電源投入後、高速なセットアップが可能な不揮発性記憶装置を提供する。

【解決手段】不揮発性記憶装置は、データを不揮発的に記憶するメモリセルを有する第1および第2のメモリモジュール16−1、16−2と、第1および第2のメモリモジュールとそれぞれ接続されて、前記第1および第2のメモリモジュールを駆動するための外部電源を供給する第1および第2の外部電源線VL11、VL12とを備え、第1の外部電源線の電源容量C1は、前記第2の外部電源線の電源容量C2よりも小さい。

(もっと読む)

垂直的に集積された不揮発性記憶セルサブストリングを含む不揮発性記憶装置の形成方法、及び形成された不揮発性記憶装置

【課題】 セルの電気的特性の均一性を向上させ得る3次元不揮発性記憶装置及びその形成方法を提供する。

【解決手段】 本発明の不揮発性記憶装置の形成方法は不揮発性記憶セルが高集積化された垂直的積層を形成するための段階を含む。不揮発性記憶セルでは、直列に電気的に連結される複数の垂直サブストリングを使用して記憶セルが半導体基板上に垂直に積層される。このとき、記憶セルの垂直方向の積層は劣等に作用するメモリセルストリングが発生しないように、製造工程において補正するためにダミー記憶セルを利用する。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】基板上で第1方向に延在するラインパターンと、ラインパターンの端部から、第1方向と異なる方向に延在する分岐ラインパターンとをそれぞれ含む第1導電ライン;第2導電ライン;第3導電ラインとを含む半導体素子であり、中間に位置する導電ラインの分岐ラインパターンは、他の導電ラインの分岐ラインパターン間に位置し、長さもさらに短い。これにより、コンタクト・パッドが、導電ラインの分岐ラインパターンと一体に形成されうる。

(もっと読む)

半導体装置及びその製造方法

【課題】追加のマスクや追加のプロセスを必要とせず、トランジスタを含む半導体装置に搭載することが可能なメモリ素子を実現する。

【解決手段】半導体装置を、絶縁膜17と金属膜又は金属化合物膜19とを積層した構造を有するメモリ素子16と、メモリ素子16と同一の積層構造を有するゲート構造を持つトランジスタとを備えるものとする。

(もっと読む)

相変化メモリコーディング

【課題】取り付け工程に係る半田付け及び高温環境での熱事象を通じても、データを保持することができる相変化メモリデバイスの提供。

【解決手段】一部のセルとメモリに第一抵抗状態、及び他部のセルとメモリに第二抵抗状態を誘導することにより、データセットを表わすために、プレコーディング(pre−coded)することができる。前記データセットがコーディングされ、基板に取り付けられた後に、前記第一及び前記第二抵抗状態を感知することにより、前記データセットを読み取り、前記第一抵抗状態を第三抵抗状態に変化させ、前記第二抵抗状態を第四抵抗状態に変化させる。半田接合と他の熱サイクルプロセスの後、前記第一及び前記第二抵抗状態は、感知マージン(sensing margin)を維持する。より高速とより低い電力を使用すると、前記第三及び前記第四抵抗状態は、転移(transition)を引き起こす能力がある。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子の平面形状を大きくせずに、その容量を大きくすることができ、かつ容量素子のリーク電流が増大することを抑制する。

【解決手段】下部電極410は、表層に、厚さが2nm以下の金属含有酸化層414を有している。金属含有酸化層414は、下部電極410の表面を酸化することにより形成されている。そして誘電膜420は、バルク状態において常温で出現する第1相と、バルク状態において第1相より高温で出現する第2相と、を含んでいる。第2相は第1相より比誘電率が高い。

(もっと読む)

61 - 80 / 302

[ Back to top ]