Fターム[5F083ZA14]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリと独立機能ブロック (1,941) | メモリ部+メモリ部(異種) (302)

Fターム[5F083ZA14]に分類される特許

41 - 60 / 302

半導体装置および半導体装置の作製方法

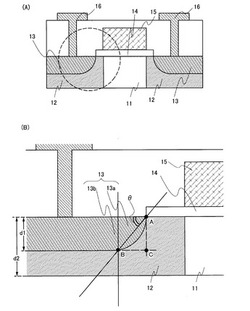

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体素子の製造方法

【課題】 製造コストの低減が可能な半導体素子の製造方法を提供する。

【解決手段】 第1再配線層400は、金属バンプ層320の一部分を露出するように形成される。第1再配線層400は、第1拡張パッド部410、第1延長部420及び第1連結部430を備える。第1拡張パッド部410は、金属パッド120と電気的に接続し、外部装置と接続する。第1延長部420は、金属バンプ層320上から第1拡張パッド部410上に延びるように形成される。第1連結部430は、スクライブレーン領域SRに形成され、複数の第1再配線層400を電気的に連結する。第1再配線層400は、銀、ニッケルまたは銅を含むペーストまたはインクを利用したプリンティング方法、または、ロールオフセットプリンティング方法によって形成される。これにより、金属パッドと再配線層との接触抵抗を小さくするとともに、製造コストを低減することができる。

(もっと読む)

半導体装置の作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供する。また、該トランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供する。

【解決手段】トランジスタに、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む酸化物半導体膜を用いる。該酸化物半導体膜は、基板加熱しつつ成膜する。また、トランジスタの作製工程において、近接の絶縁膜または/およびイオン注入により酸化物半導体膜へ酸素が供給され、キャリア発生源となる酸素欠損を限りなく低減する。また、トランジスタの作製工程において、酸化物半導体膜を高純度化し、水素濃度を極めて低くする。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

記憶素子、信号処理回路および記憶素子の駆動方法

【課題】消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路を提供する。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。例えば、容量素子の一方の電極を位相反転素子の入力あるいは出力に接続し、他方の電極をスイッチング素子に接続する。上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】FMONOSメモリセルとCMOSトランジスタが共存する半導体装置において、トランジスタの駆動電流を高めるとともにFMONOSメモリセルとしての機能を確保する半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、主表面上に形成された、チャネルを有するMONOS型メモリセルと、主表面上に形成されたnチャネル型トランジスタと、主表面上に形成されたpチャネル型トランジスタとを備える半導体装置である。上記MONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタの上面に接するように窒化膜CS1、CS2が形成されている。上記窒化膜CS1、CS2はMONOS型メモリセル、nチャネル型トランジスタおよびpチャネル型トランジスタのチャネルに応力を付加する。

(もっと読む)

バイト、ページおよびブロックに書き込むことができ、セルアレイ中で干渉を受けず分割が良好な特性を備え、新規のデコーダ設計とレイアウトの整合ユニットと技術を使用する単体式複合型不揮発メモリ

【課題】

バイト、ページおよびブロックで書き込むことができる新単体式複合型不揮発メモリを提供する。

【解決手段】

不揮発メモリアレイは、シングルトランジスタフラッシュメモリセルおよびダブルトランジスタEEPROMメモリセルを備え、同じ基板上に整合することができ、該不揮発メモリセルは低いカップリング係数の浮遊ゲートを備えて、メモリセル体積を減少でき、該浮遊ゲートをトンネル絶縁層の上に配置し、該浮遊ゲートは該ソース領域の辺縁および該ドレイン領域の辺縁に揃って、且つ該ソース領域辺縁および該ドレイン領域辺縁の幅に画定される幅を備え、該浮遊ゲートと該制御ゲートは50%より小さい相対的に小さなカップリング係数を備えて、該不揮発メモリセルを縮小できるようにし、該不揮発メモリセルのプログラムはチャネル熱電子方式で達成し、消去は高電圧でFNトンネル方式で達成する。

(もっと読む)

半導体記憶装置

【課題】不揮発性の記憶装置を有するCAMとする際に、メモリセルの低消費電力化を図ることのできる半導体記憶装置を提供することを課題の一とする。また、データの書き込みを繰り返し行う際の劣化をなくすことができる半導体記憶装置を提供することを課題の一とする。また、メモリセルの高密度化が可能な不揮発性の記憶装置を提供する。

【解決手段】酸化物半導体を半導体層に有する第1のトランジスタ及び当該第1のトランジスタをオフ状態とすることで書き込んだデータに対応する電位を保持できる容量素子を有するメモリ回路と、書き込んだ電位を参照するための参照回路を有し、参照回路を構成する第2のトランジスタの導通状態を検出することで、整合するデータのアドレスを取得し、高速な検索機能を可能にした半導体記憶装置である。

(もっと読む)

半導体装置

【課題】半導体集積回路の微細化に伴い非常に短くなったゲート長を有するトランジスタにおいて、ゲート絶縁膜におけるリーク電流の発生を抑制し、トランジスタとしての機能を高めることが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面に形成された1対のソース/ドレイン領域と、1対のソース/ドレイン領域に挟まれる領域上であって、主表面に接するように形成されたゲート絶縁膜AFEと、ゲート絶縁膜AFEの上面に接するように形成されたゲート電極POとを備える。上記1対のソース/ドレイン領域の一方から他方へ向かう方向のゲート電極POの長さは45nm未満である。ゲート絶縁膜AFEは反強誘電体膜を有する。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を提供する。また、不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】トレンチを有する絶縁層に接して、ソース領域またはドレイン領域として機能する領域の膜厚が、チャネル形成領域として機能する領域の膜厚よりも厚い酸化物半導体層を形成する。該酸化物半導体層を用いたトランジスタは、ソース抵抗またはドレイン抵抗を低減することができると共に、しきい値のバラツキ、電気特性の劣化、ノーマリーオン化を抑制することができ、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置において、安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタ(半導体装置)において、酸化物半導体膜を、絶縁層に設けられたトレンチ(溝)に設ける。トレンチは曲率半径が20nm以上60nm以下の曲面状の下端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも下端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細化及び高集積化を達成した酸化物半導体を用いた半導体装置、及び半導体装置の作製工程において、安定した電気的特性を付与し、高信頼性化する。また、上記半導体装置の作製工程において、不良を抑制し、歩留まりよく作製する技術を提供する。

【解決手段】酸化物半導体層を含むトランジスタを有する半導体装置において、酸化物半導体膜を、絶縁層に設けられたトレンチに設ける。トレンチは下端コーナ部及び曲率半径が20nm以上60nm以下の曲面状の上端コーナ部を含み、酸化物半導体膜は、トレンチの底面、下端コーナ部、上端コーナ部、及び内壁面に接して設けられる。酸化物半導体膜は、少なくとも上端コーナ部において表面に概略垂直なc軸を有している結晶を含む酸化物半導体膜である。

(もっと読む)

半導体装置及びその製造方法

【課題】セキュリティを高めるための半導体装置を提供する。

【解決手段】第1トランジスタ4a、および第1トランジスタ4aに接続される第1キャパシタ4bを有する第1メモリセル4を含む第1メモリセルアレイ2と、第1トランジスタ4aよりもオフ電流が高い第2トランジスタ5a、および第2トランジスタ5aに接続される第2キャパシタ5bを有する第2メモリセル5を含む第2メモリセルアレイ3と、を有する。

(もっと読む)

半導体装置、及び半導体装置の制御方法。

【課題】簡便な半導体装置の評価試験を実現する。

【解決手段】半導体装置10は、それぞれ内部信号MAを生成する第1及び第2のコアチップCC0,CC1を備え、第1及び第2のコアチップCC0,CC1のそれぞれに、貫通電極を介して他方のコアチップとスパイラル接続された第2及び第3のノードN2,N3を設け、この第2及び第3のノードN2,N3を介して、観測対象の内部信号MAを外部に出力することを技術思想とするものである。こうして出力される複数の内部信号MAを外部のテスター等によって観測することで、各コアチップの評価試験を並列に行える。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】電気的特性の安定した酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供すること。また、結晶性の高い酸化物半導体膜を用いることにより、移動度の向上した半導体装置を提供すること。

【解決手段】表面粗さの低減された絶縁膜上に接して、結晶性を有する酸化物半導体膜を形成することにより、電気的特性の安定した酸化物半導体膜を形成することができる。これにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することができる。さらに、移動度の向上した半導体装置を提供することができる。

(もっと読む)

半導体装置の製造方法

【課題】第1MISFETのゲート電極と第2MISFETのゲート電極とを別工程で形成する半導体装置の製造技術において、第1MISFETと第2MISFETの信頼性向上を図ることができる技術を提供する。

【解決手段】半導体基板20上にゲート絶縁膜26、電荷蓄積膜27、絶縁膜28、ポリシリコン膜29、酸化シリコン膜30、窒化シリコン膜31およびキャップ絶縁膜32からなる積層膜を形成する。そして、フォトリソグラフィ技術およびエッチング技術を使用して、低耐圧MISFET形成領域および高耐圧MISFET形成領域に形成されている積層膜を除去する。その後、半導体基板20上にゲート絶縁膜34、36、ポリシリコン膜37およびキャップ絶縁膜38を形成する。そして、低耐圧MISFET形成領域および高耐圧MISFET形成領域にゲート電極を形成した後、メモリセル形成領域にゲート電極を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を用いた半導体装置であるトランジスタにおいて、酸化物半導体膜から水素を捕縛する膜(水素捕縛膜)、および水素を拡散する膜(水素透過膜)を有し、加熱処理によって酸化物半導体膜から水素透過膜を介して水素捕縛膜へ水素を移動させる。具体的には、酸化物半導体膜を用いたトランジスタのゲート絶縁膜を、水素捕縛膜と水素透過膜との積層構造とする。このとき、水素透過膜を酸化物半導体膜と接する側に、水素捕縛膜をゲート電極と接する側に、それぞれ形成する。その後、加熱処理を行うことで酸化物半導体膜から脱離した水素を、水素透過膜を介して水素捕縛膜へ移動させることができる。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体記憶装置

【課題】総工程数を低減することができ、コストを低廉なものにする半導体記憶装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体記憶装置10は、半導体基板13と、第1不純物領域17と、第2不純物領域15と、第1不純物領域17と第2不純物領域15との間に形成されたチャネル領域75と、チャネル領域75が位置する半導体基板13の主表面上のうち、第1不純物領域17側の主表面上に形成された第1ゲート42と、チャネル領域75が位置する半導体基板13の主表面上にうち、第2不純物領域側15の主表面上に第2絶縁膜44を介して形成された第2ゲート45と、第1ゲート45に対して第2ゲート42と反対側に位置する半導体基板の主表面上に位置し、第1ゲート42の側面上に形成された第3絶縁膜46と、第3絶縁膜46とその直下に位置する半導体基板13との界面が、第2絶縁膜44とその直下に位置する半導体基板の主表面との界面より上方に位置する。

(もっと読む)

41 - 60 / 302

[ Back to top ]