Fターム[5F083ZA14]の内容

半導体メモリ (164,393) | その他 (6,553) | メモリと独立機能ブロック (1,941) | メモリ部+メモリ部(異種) (302)

Fターム[5F083ZA14]に分類される特許

201 - 220 / 302

半導体記憶装置管理システム、半導体記憶装置、半導体記憶装置管理システムの制御方法およびプログラム

【課題】用途に応じて装置寿命と記憶容量との優先度を変更可能な半導体記憶装置管理システム、半導体記憶装置、半導体記憶装置管理システムの制御方法およびプログラムを提供すること。

【解決手段】データを記憶する半導体メモリ領域21と、当該半導体メモリ領域21内の不良ブロックを代替する不良ブロック代替領域22と、を有する半導体記憶装置2を管理する半導体記憶装置管理システム1であって、半導体メモリ領域21の総ブロック数と不良ブロック代替領域22の総ブロック数との割合を変更する割合変更手段と、割合変更手段による変更に基づいて、半導体メモリ領域21または不良ブロック代替領域22の内、消費されていない一部の未消費ブロックを他方の領域に割り当てる割当手段と、を備えた。

(もっと読む)

半導体装置

【課題】CPU搭載無線タグのメモリ内のデータの書き換えを可能にした上で、CPUシステムを高速化し、無線タグの通信性能の向上を行う。

【解決手段】CPUが搭載されている無線タグにRFバッテリー付きのSRAMを搭載することで、CPUシステムの高速化による通信性能を向上させる。また、CPU搭載無線タグのメモリ内のデータの書き換えを可能にした。RFバッテリーは、アンテナ回路と、電源部と、蓄電装置と、を有する。SRAMとRFバッテリーとを組み合わせることで、SRAMに不揮発性メモリとしての機能を持たせる。

(もっと読む)

記憶装置及び半導体装置並びにそれらの作製方法

【課題】有機化合物を含む層を有する素子が設けられたフレキシブルな記憶装置及び半導体装置を歩留まり高く作製する。また、信頼性の高いフレキシブルな記憶装置及び半導体装置を歩留まり高く作製する。

【解決手段】剥離層を有する基板上に素子層及び素子層を封止する絶縁層を有する積層体を形成し、剥離層から積層体を剥離してフレキシブルな記憶装置及び半導体装置を作製する方法であって、素子層において第1の電極層及び第2の電極層からなる一対の電極間に有機化合物を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金層で形成する。また、第1の電極層及び第2の電極層からなる一対の電極間に有機化合物を含む層を有する記憶素子を含み、少なくとも一方の電極層はスズを含む合金層で形成されるフレキシブルな記憶装置及び半導体装置である。

(もっと読む)

半導体装置

【課題】低消費電力化を図ると共に、量産性を向上させることができる半導体装置を提供する。

【解決手段】半導体装置は、SRAM部とDRAM部を有している。SRAM部は、データを記憶するラッチ回路(図示せず)を有するセルCELL1を複数有している。DRAM部は、データを記憶するキャパシタ(図示せず)を有するセルCELL2と、このセルCELL2のデータを読み出して出力するセンスアンプSAを複数有している。このような半導体装置において、SRAMセルの書き込み又は読み出し動作マージンを拡大するようSRAMの回路設計を行う。このSRAMセルの回路設計に応じて、DRAMのセンスアンプを略同一構成となるよう設計する。設計手段として、例えば、データを保護するためにSRAMセルCELL1に設けた読み出し用トランジスタ37をDRAMのセンスアンプSAにも設ける。

(もっと読む)

電気光学装置の製造方法、電気光学装置、及び電子機器

【課題】電気光学装置を構成する基板上に直接不揮発性メモリを形成することができ、しかも良好に動作する高信頼性のものを得る、電気光学装置の製造方法、電気光学装置、及び電子機器を提供する。

【解決手段】不揮発性メモリ110a,110bを構成する半導体層を形成するとともに、画素部及び駆動回路の少なくとも一方のスイッチング素子を構成する半導体層を形成する。半導体層を覆って第1の絶縁膜35とフローティングゲート電極36とを順に形成し、フローティングゲート電極36を覆って第2の絶縁膜37を形成する。第2の絶縁膜37上にゲート電極38を形成する。ゲート電極38及びフローティングゲート電極36をマスクにして絶縁膜18をエッチングした後、第3の絶縁膜40を形成する。そして、第3の絶縁膜40を介し、フローティングゲート電極36上にコントロールゲート電極60を形成し、電気光学装置を製造する。

(もっと読む)

マスクプログラム可能なアンチヒューズ構造

ワードライン及びビットラインに接続されると共に、マスクプログラムが可能で、かつワンタイムプログラムが可能なメモリセルを有するメモリアレイを提供する。メモリアレイの全てのメモリセルは、ワンタイムプログラム可能なメモリセルとして構成される。あらゆる数のこれらのワンタイムプログラム可能なメモリセルは、拡散マスクプログラミングもしくは接点/ビアマスクプログラミングのようなマスクプログラミングによって、マスクプログラム可能なメモリセルに変換できる。両方のタイプのメモリセルが、同じ材料で構成されるので、そのようなハイブリッドメモリアレイの製造は単純化され、従って、わずか1つの共通の製造工程のステップが必要とされる。マスクプログラム可能なメモリセルの不注意なユーザプログラミングは、プログラミングロック回路によって抑制されている。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】基板表面と基板上に形成された配線とで形成される段差部分にシリコン膜を形成した場合においても、メモリ素子の書き込み特性を低下させない半導体装置および当該半導体装置の作製方法を提供する。

【解決手段】絶縁表面を有する基板10上に形成された第1の電極11と、第1の電極11の側壁部に形成されたサイドウォール絶縁層12と、第1の電極11上及びサイドウォール絶縁層12を覆って形成されたシリコン膜13と、シリコン膜13上に形成された第2の電極14と、を有し、第1の電極11又は第2の電極14は、シリコン膜13と合金化する材料で形成されているメモリ素子を複数有している。

(もっと読む)

半導体記憶装置

【課題】 埋め込みビット線構造の半導体記憶装置において、当該ビット線構造に起因する諸々の問題を解決し、確実なシリサイド形成を行なうことを可能とし、低抵抗で更なる微細化・高速動作化を実現する。

【解決手段】 ビット線11と不純物拡散層14は、各々の一端が重畳されて接続されており、周辺回路領域3における選択トランジスタのソース/ドレイン17の表層及び重畳部位14aを含む不純物拡散層14の表層に高融点金属、ここではTiとSiとのシリサイド化が施され、チタンシリサイド層18が形成されている。

(もっと読む)

半導体記憶装置および半導体集積回路装置

【課題】SRAMセルのダイナミックスタビリティを考慮して、メモリセルの安定性をさらに増大させる。

【解決手段】フラッシュメモリセルのフローティングゲート(FG)およびコントロールゲート(CG)を製造する工程を利用して、容量素子(C1,C2)を、記憶ノード(SN,/SN)に接続する。すなわち、SRAMセルの負荷トランジスタ(PT1,PT2)およびドライバトランジスタ(NT1,NT2)のゲート電極を、フローティングゲートと同一層の配線で形成し、コントロールゲートと同一の配線層の配線を、負荷およびドライバトランジスタのゲート電極と整列して配置するキャパシタ電極として形成する。

(もっと読む)

半導体装置

【課題】SRAMセルに必要な配線層を減らすことができる半導体装置及びその設計方法を提供すること。

【解決手段】半導体装置は、ビットライン22が容量素子31より下方にあるスタック型の構成を有するDRAMとSRAMとが混載されてなる。そして、SRAMのノード間接続24は、DRAMの容量下部電極32が形成される層以下であって、ビットライン22が形成される層以上の層の、例えば容量コンタクト23と同じ層に形成されている。

(もっと読む)

半導体素子及びその形成方法

【課題】下部領域にコンタクトを通じて電気的に連結される配線を形成する方法を提供する。

【解決手段】本発明の配線の形成方法は、複数の第1領域と、前記第1領域の間に各々配置された複数の第2領域とを有する基板上に絶縁膜を形成し、前記絶縁膜上に前記絶縁膜を貫通する第1コンタクトを通じて各々対応する前記第1領域に電気的に連結される複数の第1配線を形成し、前記第1配線の側面にスペーサを形成し、隣り合う前記スペーサの間の前記絶縁膜を除去して隣り合う前記第1コンタクトの間に対応する前記第2領域を露出する複数のコンタクトホールを形成し、対応する前記コンタクトホールを埋める複数の第2コンタクトを形成して対応する前記第2コンタクトに電気的に連結される複数の第2配線を形成することを特徴とする。

(もっと読む)

半導体装置

【課題】複数のスタックコンタクトが近接して設けられる場合にも、これを安定的に形成する。

【解決手段】半導体装置100中の一対の隣接するスタックコンタクト141およびスタックコンタクト143において、第一層間絶縁膜109より厚い第二層間絶縁膜114を貫通するプラグ139の中心間距離が、第一層間絶縁膜109を貫通するプラグ135の中心間距離よりも大きくなるように、プラグ135およびプラグ139を配置する。

(もっと読む)

複数の分離されたウェル領域上のローカルコントロールゲートを含む不揮発性メモリ装置及び関連する方法とシステム

【課題】不揮発性集積回路メモリ装置を提供する。

【解決手段】本発明の不揮発性集積回路メモリ装置は、同一な伝導性を有する電気的に分離された第1及び第2ウェルを含む半導体基板と、前記第1ウェル上の複数の第1不揮発性メモリセルトランジスタと、前記第2ウェル上の複数の第2不揮発性メモリセルトランジスタと、前記複数の第1及び第2不揮発性メモリセルトランジスタに電気的に連結されるローカルコントロールゲートラインと、前記ローカルゲートラインとグローバルコントロールゲートラインの間に電気的に連結されるグループ選択トランジスタと、を含む。より詳細には、前記グループ選択トランジスタは、前記グループ選択トランジスタのゲートに印加されたグループ選択ゲート信号に応じて、前記ローカルコントロールゲートライン及び前記グローバルコントロールゲートラインを電気的に断続するように設定される。

(もっと読む)

互いに異なる相変化物質を備えたメモリセルを有する相変化メモリ素子、それに関連した方法及びシステム

【課題】互いに異なる相変化物質を有するメモリセルを備える相変化メモリ素子、それに関連した方法及びシステムを開示する。

【解決手段】相変化メモリ素子は集積回路基板及び前記集積回路基板上に配置された第1及び第2相変化メモリ要素を備える。前記1相変化メモリ要素は第1結晶化温度を有する第1相変化物質を備える。前記2相変化メモリ要素は第2結晶化温度を有する第2相変化物質を備える。前記第1及び第2相変化メモリ要素を互いに異なる温度においてプログラムできるように前記第1及び第2結晶化温度は互いに異なる。それに関連した方法及びシステムも提供する。

(もっと読む)

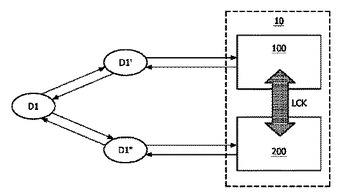

安全な不揮発性メモリ装置およびその内部データを保護する方法

本発明は、不揮発性メモリ装置に関し、この不揮発性メモリ装置は、格納すべき外部データ(D1)を不揮発性メモリ装置に供給する入力と、第1不揮発性メモリブロック(100)および第2不揮発性メモリブロック(200)と、を備え、第1不揮発性メモリブロック(100)および第2不揮発性メモリブロック(200)を、単独のチップ(10)上に設け、第1不揮発性メモリブロック(100)および第2不揮発性メモリブロック(200)は異なるタイプの構成とし、これにより第1不揮発性メモリブロック(100)および第2不揮発性メモリブロック(200)の双方に分散して(D1′、D1″)格納した外部データ(D1)から、データを取得するためには、第1不揮発性メモリブロックおよび第2不揮発性メモリブロックは互換性のない外部攻撃技術を必要とする。本発明は、さらに不揮発性メモリ装置内のデータを保護する方法に関する。  (もっと読む)

(もっと読む)

抵抗変化型素子、不揮発性記憶素子、抵抗変化型記憶装置、およびこれらに対するデータ書き込み方法

【課題】新規な構成を有するライトワンス型の抵抗変化型記憶装置を提供する。

【解決手段】第1の電極と、第2の電極と、前記第1の電極と前記第2の電極との間に形成された薄膜とを備え、前記薄膜は遷移金属を含む酸化物を含有し、第1のレベル以上の電気パルスを前記第1の電極および前記第2の電極を介して前記薄膜に加えると前記第1の電極および前記第2の電極の間の電気抵抗が不可逆的に変化する。

(もっと読む)

半導体装置、メモリ回路及び機械語プログラム生成装置、並びに半導体装置及びメモリ回路の動作方法

【課題】消費電力の低下が可能な半導体装置及びメモリ回路、並びにこれらの動作方法を提案することを課題とする。

【解決手段】演算回路102と制御回路103とを具備する演算処理回路101と、ROM105とRAM106とを具備するメモリ回路104とを有し、演算処理回路101とメモリ回路104は、アドレスバス107及びデータバス108を介して接続され、ROM105は、演算処理回路101を用いて実行される機械語プログラムのデータが格納されており、RAM106は、複数のバンクを有し、機械語プログラムが実行した際の処理データが、複数のスタックに分割されて複数のバンクに格納され、複数のバンクに格納される複数のスタックにおいて、機械語プログラム終了まで使用されないスタックが省かれ、連続したスタックが同一のバンクに書き込まれるように、機械語プログラムに基づいて演算処理回路が動作する。

(もっと読む)

半導体装置

【課題】 不揮発性記憶素子を有する半導体装置の高集積化及び書換回数向上を図る。

【解決手段】 第1のMONOS型不揮発性記憶素子と、前記第1のMONOS型不揮発性記憶素子よりもゲート幅が広い第2のMONOS型不揮発性記憶素子とを同一基板に混載し、前記第1のMONOS型不揮発性記憶素子を書換回数が少ないプログラムのデータ記憶用として用い、前記第2のMONOS型不揮発性記憶素子を書換回数が多い処理データ記憶用として用いる。

(もっと読む)

メモリセル及び不揮発性記憶装置

【課題】DRAM装置と同等の動作速度を維持しかつ電源切断時にデータを記憶する。

【解決手段】第1の制御用信号線に第1制御端子が接続され、第1の端子がビット線に接続された第1の電界効果トランジスタと、一端が上記第1の電界効果トランジスタの第2の端子に接続され、他端が第1の基準電位に接続されたキャパシタと、第1の電界効果トランジスタの第2の端子と上記キャパシタの一端が接続された記憶ノードに第3の端子が接続され、第2の制御端子が第2の制御用信号線に接続された第2の電界効果トランジスタと、一端が第2の電界効果トランジスタの第4の端子に接続され、他端が第2の基準電位に接続された不揮発性記憶素子とを有し、リフレッシュ動作の一分を代替すると共に電源オフ時に情報を記憶する。

(もっと読む)

半導体装置及び電子機器

【課題】メモリにおけるデータの読み出しに関し、低消費電力なメモリを搭載した半導体装置を提供することを課題とする。

【解決手段】ワード線と、ビット線と、ワード線及びビット線に電気的に接続されたメモリセルを有する半導体装置において、ビット線に接続され、ビット線の電位をメモリセルに保持されたデータを読み出すための電位にするプリチャージ回路を有し、プリチャージ回路はビット線毎に設けられており、ビット線毎にメモリセルに保持されたデータを読み出すための電位にする構成とする。

(もっと読む)

201 - 220 / 302

[ Back to top ]