Fターム[5F092BC04]の内容

ホール/MR素子 (37,442) | MR素子の構造形状 (5,946) | 積層構造 (4,801) | MR素子を形成する層の積層順 (1,654) | 自由層が固定層より上にあるもの (1,135)

Fターム[5F092BC04]に分類される特許

1,121 - 1,135 / 1,135

膜面垂直通電方式スピンバルブ磁気抵抗センサ

磁気抵抗読み取りヘッドは、スペーサにより少なくとも一つのピン層から離間させた少なくとも一つのフリー層を有するスピンバルブを含む。ピン層は高抵抗性であり、ピン層の少なくとも一部に使用するCo100−xFex層を含む。随意選択的には、この材料は少なくともフリー層の一部に使用することもできる。xの値は、10〜75%±約10%の各種値とすることができる。ピン層は単層或いは副層間にスペーサを有する合成多層構造である。抵抗率を増大させるべく、ピン層とフリー層のいずれか或いは両方の成膜期間中に酸素を導入する。  (もっと読む)

(もっと読む)

安定化スピンバルブヘッドとその製造方法

磁気抵抗読み取りヘッドは、多層積層バイアス(107)と、記録媒体自体からの横断磁界からだけでなく隣接するビット及びトラックからの不要磁束も実質的に低減する側部シールド(113)を有するスピンバルブを含む。少なくとも一つのフリー層(100)が、スペーサ(101)により少なくとも一つのピン層(102)から離間させてある。フリー層の上方にキャップ層(106)を配設し、これに非磁性導電層(111)と反強磁性層(109)により固定された磁化を有する強磁性層(110)と安定化強磁性層とを含む積層バイアス(107)が続く。加えて、薄肉絶縁体(114)と軟質バッファ層(115)と軟質側部シールド層(116)とを含む多層側部シールド(113)を配設する。その結果、フリー層(100)は不要磁束から遮蔽され、記録媒体は実質的により小さなトラックとビット寸法を有する。  (もっと読む)

(もっと読む)

磁気抵抗ヘッドを安定化させる合成フリー層

磁気抵抗読取りヘッドは、スペーサにより少なくとも一つのピン層から離間させた少なくとも一つのフリー層を有するスピンバルブを含む。フリー層はCo−XとCoFe−XとCoNi−Xのうちの少なくとも一つを含む薄膜としてのコバルト成分を含み、ここでXはランタノイド族(4f電子軌道元素)からの元素である。Co成分は80パーセントを上回り、ランタノイド元素成分は10%未満である。薄膜はフリー層全体で構成するか、或いは1以上の従来のフリー層薄膜に隣接配置することができる。ピン層は、従来の単層か又は副層間にスペーサを有する合成多層構造である。スピンバルブ構造が高い交換スティフネスと減衰率を有するため、スピン転移効果は減り、高速動的応答がもたらされる。  (もっと読む)

(もっと読む)

低磁歪を有する磁気抵抗ヘッドを安定化させる積層フリー層

磁気抵読み取りヘッドは、スペーサにより少なくとも一つのピン層から離間させた少なくとも一つのフリー層を有するスピンバルブを含む。フリー層は、CoFe内の薄いCoFeOx積層と随意選択的なCu層を含む。酸素の量は、ガス全体の10%未満である。ピン層は単層か又は副層間にスペーサを有する合成多層構造であり、前述の低磁歪材料を用いることができる。その結果、低磁歪を得て読み取り品質を改善し、かつ/又はピン層のピンニング磁界を増加する。他パラメータが悪影響を受けることはない。  (もっと読む)

(もっと読む)

低飽和磁化自由層を有するスピン転移磁気素子

磁気メモリに用い得る磁気素子を提供するための方法及びシステムを提供する。磁気素子は、固定層と、非磁性スペーサ層と、自由層と、を含む。スペーサ層は、固定層と自由層との間に存在する。自由層は、書き込み電流が磁気素子を通過する時、スピン転移を用いて切換え得る。磁気素子は、更に、障壁層と、第2固定層とを含み得る。他の選択肢として、第2固定層と、第2スペーサ層と、自由層に静磁気的に結合された第2自由層とを含む。一つの態様において、自由層(1つ又は複数)は、非磁性材料(1つ又は複数)で希釈された強磁性材料(1つ又は複数)か、フェリ磁性的にドープされた強磁性材料(1つ又は複数)か、又は、非磁性材料(1つ又は複数)で希釈され且つフェリ磁性的にドープされた強磁性材料(1つ又は複数)を含み、低飽和磁化(1つ又は複数)を提供する。 (もっと読む)

スピン転移を利用する磁気素子の熱支援スイッチングを提供するための方法及びシステム

磁気メモリに用い得る磁気素子を提供するための方法及びシステム。磁気素子は、固定層、非磁性スペーサ層、自由層、及び熱支援スイッチング層を含む。スペーサ層は、固定層と自由層との間に存在する。自由層は、スペーサ層と熱支援スイッチング層との間に存在する。熱支援スイッチング層は、自由層が切り替えられていない時に、好適には自由層との交換結合によって、自由層の熱的な安定性を改善する。自由層は、書き込み電流が磁気素子を通過する時、スピン転移を用いて切り替えられる。書き込み電流は、好適には、磁気素子を加熱して、熱支援スイッチング層によって提供された自由層の安定化を低減する。他の態様において、磁気素子は、第2自由層、第2非磁性スペーサ層、及び第2固定層を含む。熱支援スイッチング層は、静磁気的に結合された2つの自由層間に存在する。第2スペーサ層は、第2自由層と第2固定層との間に存在する。 (もっと読む)

MRAM技術のMTJに使用される合成反強磁性体構造

磁気トンネル接合(MTJ)(10)は、磁気抵抗ランダムアクセスメモリ(MRAM)において有用なものであるが、合成反強磁性体(SAF)構造である自由層(14)を有している。このSAF(14)は、カップリング層(28)によって分離される2つの強磁性層(26,30)から構成される。カップリング層(28)は、非磁性のベース材料と、さらにはSAF(14)の耐熱性、カップリング強度の制御性、および磁気抵抗比(MR)を改善する別の材料も有している。好ましいベース材料はルテニウムであり、好ましい別の材料はタンタルである。これらの利点を高めるために、タンタルと強磁性層のうちの1つとの間の界面にコバルト鉄が加えられる。また、カップリング層(28)はより多く層をさらに(38,40)有してもよく、使用される材料は種々に異なり得る。また、カップリング層(28)は、それ自体が合金であってもよい。  (もっと読む)

(もっと読む)

高感度磁気内蔵電流センサ

電流を非接触検出するためのセンサは、磁気トンネル接合(MTJ)を有するセンサ素子と検出回路とを有しており、センサ素子は磁場に伴って変化する抵抗を有し、また、検出回路は、トンネル接合を通じて流れるトンネル電流を検出するようになっている。センサ素子は、MTJ積層体をメモリ素子と共有していても良い。また、センサ素子は、MRAM技術を含む次世代のCMOSプロセスと容易に統合することができ、よりコンパクトであるとともに、電力消費が少ない。磁束集結体を設けるなどのセンサの感度を高めるための解決策、および、L形状導体素子を形成するなどの同じ電流を用いて高い磁場を生成するための解決策が与えられる。感度が高いため、後処理をあまり使用せずに済み、モバイル機器等の用途においては電力を節約することができる。用途としては、電流センサ、内蔵電流センサ、IDDQおよびIDDT試験を挙げることができ、次世代CMOSプロセスにおいても使用できる。  (もっと読む)

(もっと読む)

磁気メモリ用のデータ保持インジケータ

本発明は、少なくとも1つのデータ保持インジケータデバイス(50)が設けられた磁気抵抗メモリ素子(10)のアレイ(20)を提供する。少なくとも1つのデータ保持インジケータデバイス(50)は、それぞれプリセットされた磁化方向を有する第1の磁気素子(51)と、第2の磁気素子(52)とを備え、第1および第2の磁気素子(51,52)のプリセットされた磁化方向は、互いに異なっている。第1および第2の磁気素子(51,52)は、これらの磁化方向を、検出しきい値を超える外部から印加された磁界の磁界線と向きを揃えるのに適している。本発明によれば、少なくとも1つのデータ保持インジケータデバイス(50)のパラメータが、検出されるべき外部から印加された磁界の検出しきい値を設定するように選択される。少なくとも1つのデータ保持インジケータデバイス(50)は、アレイ(20)の磁気抵抗メモリ素子(10)の前記外部から印加された磁界への暴露を示す状態または出力を有する。  (もっと読む)

(もっと読む)

磁気メモリ用途のための応力支援による電流駆動式スイッチング

磁気メモリを提供するための方法及びシステム。本方法及びシステムは、複数の磁気素子を設けること、少なくとも1つの応力支援層を設けること、を含む。複数の磁気素子の各々は、スピン転移を用いて書き込まれるように構成されている。少なくとも1つの応力支援層は、書き込み時、複数の磁気素子の少なくとも1つの磁気素子に少なくとも1つの応力を及ぼすように構成されている。書き込み時、応力支援層によって磁気素子に及ぼされる応力により、スピン転移スイッチング電流が低減される。スイッチング電流が一旦オフになると、2つの磁化状態間のエネルギ障壁が変化しないことから、熱変動に対する磁気メモリの安定性が損なわれることはない。  (もっと読む)

(もっと読む)

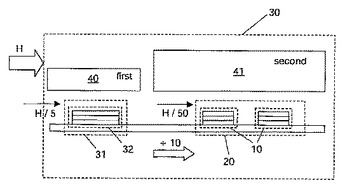

磁界センサを有するMRAMチップの不均一シールド

本発明は、磁気抵抗メモリ素子のアレイと少なくとも一つの磁界センサ素子とを備える磁気抵抗メモリデバイスであって、前記磁気抵抗メモリ素子の前記アレイを、少なくとも一つの前記磁界センサ素子とは異なるように外部磁界からシールドするための部分シールド手段又は不均一シールド手段を備える磁気抵抗メモリデバイスを提供する。「異なるように」とは、5%の最小シールド差、好ましくは10%の最小シールド差が存在することを意味している。また、本発明は対応するシールド方法も提供する。  (もっと読む)

(もっと読む)

磁気抵抗メモリデバイスの書き込みの間の活性フィールド補償を実行するためのデバイス及び方法

本発明は、磁気抵抗メモリ素子(10)のアレイ(20)を提供する。アレイ(20)は、選択磁気抵抗メモリ素子(10)において書き込み磁場を生成するための電流又は電圧をもたらすための手段と、選択磁気抵抗メモリ素子(10)の近くにおける外部磁場を測定するための磁場センサユニット(50)と、書き込み動作の間に、測定された外部磁場を局部的に補償するための電流又は電圧を調整するための手段(52)とを有する。本発明は、対応する方法も提供する。

(もっと読む)

(もっと読む)

スピン転移スイッチングを利用し且つ複数のビットを記憶する磁気メモリ素子

複数のビットを記憶可能な磁気素子を提供するための方法及びシステムを開示する。本方法及びシステムには、第1固定層、第1非磁性層、第1自由層、接続層、第2固定層、第2非磁性層及び第2自由層を設ける段階が含まれる。第1固定層は、強磁性体であり、第1方向に固定された第1固定層磁化を有する。第1非磁性層は、第1固定層と第1自由層との間にある。第1自由層は、強磁性体であり、第1自由層磁化を有する。第2固定層は、強磁性体であり、第2方向に固定された第2固定層磁化を有する。接続層は、第2固定層と第1自由層との間にある。第2非磁性層は、第2固定層と第2自由層との間にある。第2自由層は、強磁性体であり、第2自由層磁化を有する。磁気素子は、書き込み電流が磁気素子を通過する際のスピン転移により第1自由層磁化及び第2自由層磁化が方向を変更可能となるように構成される。  (もっと読む)

(もっと読む)

複合磁気フリー層を有する磁気エレクトロニクス情報デバイス

磁気エレクトロニクス情報デバイス(12)は、2つの多層構造(24,26)及び該2つの多層構造の間に配置されたスペーサ層(28)を備えている。各多層構造は、2つの磁気副層(38,40及び44,46)と、該2つの磁気副層の間に配置されたスペーサ層(42,48)とを有している。2つの磁気副層の間に配置されたスペーサ層は、飽和領域によって定量化される反強磁性交換結合を提供する。2つの多層構造の間に配置されたスペーサ層は、前記第1飽和領域よりも小さい他の飽和領域によって定量化される第2反強磁性交換結合を提供する。  (もっと読む)

(もっと読む)

1T‐nメモリセル積層構造体

本発明は、クロスポイントと1T‐1セルとの双方の設計に基づくある種の利点を導入するためのメモリ技術及びメモリアレイに関する新規な変更に関する。これらの設計のある特徴を組み合わせることにより、1T‐1セル設計における読出し時間の高速化及び信号対雑音比の増大と、クロスポイント設計における高記録密度化との双方が達成される。そのために、単一のアクセストランジスタ16を用いて、“Z”軸方向に配置された複数のメモリアレイ層で垂直方向に互いに上下に積み重ねうる多重メモリセルを読出すようにする。  (もっと読む)

(もっと読む)

1,121 - 1,135 / 1,135

[ Back to top ]