Fターム[5F102FA04]の内容

接合型電界効果トランジスタ (42,929) | 目的、効果 (2,241) | 温度特性改善 (18)

Fターム[5F102FA04]に分類される特許

1 - 18 / 18

半導体装置および半導体装置の製造方法

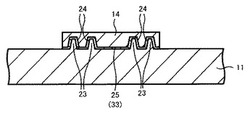

【課題】半導体パッケージ内における半導体素子の位置ずれを抑制することができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、凸部23が形成されたパッケージ基板11、導電性の接着剤25、およびパッケージ基板11上に実装された半導体素子14、を具備する。パッケージ基板11は、少なくとも2箇所に凸部23が形成された基板である。導電性の接着剤25は、凸部23を含むパッケージ基板11上に形成される。パッケージ基板11上に実装される半導体素子14は、各凸部23に係合する複数のバイアホール24を有している。さらに、半導体素子14は、少なくとも2箇所のバイアホール24が、各凸部23に接着剤25を介して係合するようにパッケージ基板11上に実装される。

(もっと読む)

ダイアモンド基板上炭化珪素並びに関連するデバイス及び方法

【課題】ワイドバンドギャップ材料内に、接合温度低下、動作中の高電力密度化、及び定格電力密度における信頼性向上を達成する高電力デバイスを形成する。

【解決手段】SiC層10にSiO2層を形成し、次いで、熱伝導率を高めるためにダイアモンド層11を形成する。そして、SiC層10の厚さを低減し、ダイアモンド層11及びSiC層10の向きを逆にしてダイアモンド11を基板とする。次いで、SiC層10上に、バッファ層16、ヘテロ構造層14及び15を形成する。

(もっと読む)

半導体装置

【課題】素子温度の上昇を抑制する半導体装置を提供する。

【解決手段】動作周波数fで動作可能な半導体装置であって、熱拡散率Dの基板と、基板上に形成され、ワイドギャップ半導体素子で横型素子の第1のトランジスタで構成される第1の素子ユニット12と、基板上に第1の素子ユニット12に隣接して形成され、第1のトランジスタと異なるタイミングで動作するワイドギャップ半導体素子で横型素子の第2のトランジスタで構成される第2の素子ユニット14とを備え、第1の素子ユニット12の重心と、第2の素子ユニット14の重心との距離が熱拡散長(D/πf)1/2の2倍以下であることを特徴とする半導体装置。

(もっと読む)

アイランドマトリックス化窒化ガリウムマイクロ波トランジスタおよびパワースイッチングトランジスタ

単位面積あたりの電流処理能力が従来の窒化ガリウム(GaN)デバイスよりも非常に優れたGaNデバイスを開示する。当該改良は、レイアウトトポロジの改良によるものである。フィンガー電極ではなくアイランド電極を使用する当該レイアウトスキームは、従来のインターデジタル構造よりも活性面密度を増加させることを示す。当該アイランドトポロジを用いて超低オン抵抗トランジスタを構築することができる。具体的には、本発明は、従来通りのGaN水平方向技術および電極間隔を用いており、すべての水平方向GaN構造のコストパフォーマンス/実効性能を高める手段を提供する。

(もっと読む)

(もっと読む)

半導体装置

【課題】電力密度の集中を抑制して発熱の分散を図り、かつ電気位相差を低減した高性能な半導体装置を提供する。

【解決手段】基板上に配置された窒化物系化合物半導体層と、窒化物系化合物半導体層上に配置され、アルミニウム窒化ガリウム層(AlxGa1-xN)(0.1≦x≦1)からなる活性領域と、活性領域を互いに素子分離する素子分離領域と、素子分離領域によって囲まれた活性領域上に配置されたゲート電極24、ソース電極20およびドレイン電極22と、素子分離領域14上に配置され、それぞれゲート電極24,ソース電極20およびドレイン電極22に接続されたゲート端子電極240,ソース端子電極200およびドレイン端子電極220とを備え、ゲート電極24の分岐を再帰的な自己相似のフラクタル図形で構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半絶縁性SiC基板を用いずとも良好な高周波数特性を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】導電性SiC基板1上に化合物半導体領域2が形成されている。化合物半導体領域2には、順次積層されたバッファ層2a、電子走行層2b、電子供給層2c及び表面層2dが含まれている。化合物半導体領域2には、活性領域を画定する素子分離領域3が設けられている。そして、活性領域と整合するようにして、導電性SiC基板1に開口部1aが形成されている。表面層2dには、電子供給層2cを露出する2個の開口部が形成されており、開口部の各々に、オーミック電極がソース電極4又はドレイン電極5として形成されている。更に、開口部10aを介して表面層2dと接するゲート電極6がシリコン窒化膜10上に形成されている。

(もっと読む)

接合型電界効果トランジスタの駆動装置および駆動方法

【課題】簡単な構成によって、一時的な過電流による接合型電界効果トランジスタの発熱を抑制するとともに、接合型電界効果トランジスタの過熱状態を検知することができる接合型電界効果トランジスタの駆動装置および駆動方法を提供する。

【解決手段】電流検知部90でモニタする電流が閾値電流を超えた場合、接合型電界効果トランジスタ(JFET)32をターンオンするときのゲート電圧をPN接合のビルトイン電圧より大きくする。これにより、JFET32のオン抵抗を低減させてJFET32の発熱を抑制する。さらに、オン状態のJFET32に流れるゲート電流IGの温度依存性を利用することによって、JFET32の温度の値を簡単に求めることができる。

(もっと読む)

スイッチング回路

【課題】、接合型電界効果トランジスタ(JFET)の高温動作時のオン抵抗を低減して、高温時の動作特性を改善すること。

【解決手段】出力切替回路34は、温度検出装置33によって検出された温度が所定の閾値温度以上であるとき、第2の駆動回路32に出力切替指示を与える。これにより、第2の駆動回路は、MOSFET35を駆動して、JFET10に立ち上がり電圧(順方向降下電圧)VF以上のゲート電圧VGSが印加され、JFETはバイポーラ動作される。これにより、高温時のJFET10のオン抵抗の増加を抑制できる。

(もっと読む)

半導体装置

【課題】電力密度が高く、発熱密度が高い半導体装置の熱分散を容易にする電極配置を提供する。

【解決手段】基板10の第1表面に配置され,それぞれ複数のフィンガーを有するゲート電極24、ソース電極20およびドレイン電極22と、第1表面に配置され,ゲート電極24、ソース電極20およびドレイン電極22ごとに複数のフィンガーをそれぞれ束ねたゲート端子電極G1,G2,…,G4、ソース端子電極S1,S2,…,S5およびドレイン端子電極Dと、ゲート電極24、ソース電極20およびドレイン電極22の下部の基板10上に配置された活性領域AA1,AA2,…,AA5と、基板10上に活性領域に隣接して配置された非活性領域(BA)と、ソース端子電極に接続されたヴィアホールSC1,SC2,…,SC5とを備え、活性領域がストライプ状に複数に分割され、かつゲート電極24がフィッシュボーン配置されている半導体装置。

(もっと読む)

高温動作可能窒化ガリウムトランジスタ

【課題】高温において高性能なトランジスタデバイスを提供する。

【解決手段】トランジスタは、活性領域に接触するコンタクト層を有するゲートを備える。ゲートコンタクト層は、特定の半導体系(例えば、III属窒化物)と共に使用される場合に、高ショットキー障壁を有し、かつ高温で動作しているときに、低減された劣化を呈する材料で製作される。デバイスは、デバイスの動作寿命をさらに増大させるために、フィールドプレートを組み込むこともできる。

(もっと読む)

半導体装置のセル配置方法

【課題】発熱領域が集中して配置されていることによって熱抵抗が増大することを防止し、チップ面積を大きくすることなく発熱領域を分散させる、半導体装置のセル配置方法を提供する。

【解決手段】単位FETをゲートフィンガー電極複数本をまとめて一個のセル11とし、チップの長手方向にフィンガー電極を平行にして配置する。各セル11間の隙間に、ソースフィンガー電極13aを接続したバイアホール12付ソース電極配線13と、ゲートフィンガー電極14aを接続したゲート電極配線14と、ドレインフィンガー電極15aを接続したドレイン電極配線15を対称性を鑑みて配置し、ドレインバスライン16に接続され、同様に各ゲート電極配線はゲートバスライン17に接続されている。従来十分できなかった長手方向の放熱が、そのセル間隔を基板厚程度としているので、熱は長手横方向にも拡散しながら下部のヒートシンクへと有効に放熱される。

(もっと読む)

半導体装置

【課題】窒化物半導体デバイスにおいて、パワートランジスタへの応用に不可欠な大電力消費時のデバイス内部の熱の不均一化を解消する。

【解決手段】基板11上に形成されたGaNからなる動作層12の上に、AlxGa(1-x)N(0<x≦1)からなる障壁層13が積層されており、動作層12と障壁層13とからヘテロ接合界面が形成されている。ソース電極14およびドレイン電極15が互いに間隔をおいて形成され、ソース電極およびドレイン電極間にはゲート電極16が形成されている。表面には絶縁性と密着性の高いカーボン化合物20を施す。カーボン化合物膜20の上に、放熱膜として放熱性に優れた熱伝導率の高いダイヤモンド膜19を施す。これらの膜は前記動作層および前記障壁層および前記基板を貫通する溝21ごと表面を被覆している。

(もっと読む)

電界効果トランジスタ

【課題】櫛形電極構造を有する電界効果トランジスタにおいて、ゲート電極に平行な方向および異なる単位電界効果トランジスタ間の温度分布を低減することで動作の均一性を向上し、高周波特性や信頼性に優れた電界効果トランジスタ(FET)を提供する。

【解決手段】本発明の電界効果トランジスタ(FET)は、基板上の一領域内に並列配置された複数のゲート電極と、前記一領域内に設けられた導電性を有する能動領域と、前記能動領域のゲート電極の延在方向中央部に設けられる非導電領域とを含み、各ゲート電極に対するゲート電極の延在方向における前記非導電領域が占める割合が、ゲート電極の配列方向における端部よりも中央部分において大きいことを特徴とする。

(もっと読む)

半導体装置

【課題】半導体チップの温度分布を極力均一にする半導体装置を提供する。

【解決手段】半導体チップの中心電力密度を小さく、チップ周辺に向かうに従って電力密度を大きくし、チップ内の温度分布を小さくしたことを特徴とする半導体装置。半導体チップ内に素子のセルを形成しない領域を作成し、その面積密度を調整することにより、半導体チップ内のセル密度を小さく、チップ周辺に向かうに従ってセル密度を大きくし、チップ内の温度分布を小さくしたことを特徴とする半導体装置。半導体チップ内に一様に素子を形成するが、素子の一部については動作しないように配線することにより、半導体チップ内の動作する素子セル密度を小さく、チップ周辺に向かうに従って動作しないセル密度を大きくして、チップ内の温度分布を小さくしたことを特徴とする半導体装置。

(もっと読む)

高出力半導体デバイスのための半導体構造体の作成方法

高出力半導体デバイスのための基材配置物は、SiCウエハの表面上に付着させたSi層を有するSiCウエハを包含する。Si第1層、SiO2中間層およびSi第3層を有するSOI構造体が、そのSi第3層を、SiCウエハ上に付着させたSiに接着して、単一構造体を形成する。SOIのSi第1層およびSiO2中間層を除去して、純粋なSi第3層を残し、この上にさまざまな半導体デバイスを製作することができる。Si第3層および付着Si層を、1種以上の半導体デバイスをSiCウエハ上に製作することができるように基材配置物の一部にわたり除去してもよい一方、他の半導体デバイスを純粋なSi第3層上に対応させてもよい。 (もっと読む)

半導体装置

【課題】 入力端子にインピーダンス素子が接続されている半導体装置において、温度上昇によっノイズが増加してしまうといった問題を解決した半導体装置を提供する。

【解決手段】 入力トランジスタのゲート端子若しくはベース端子を半導体装置の入力端子とし、ソース端子若しくはエミッタ端子と入力端子との間に、インピーダンス素子を接続することで入力インピーダンスをコントロールする半導体装置において、インピーダンス素子は、正の温度係数を有するインピーダンス素子と負の温度係数を有するインピーダンス素子を直列に接続し、温度変化に伴う入力インピーダンスの変化を緩和する。

(もっと読む)

ハイブリッドエピタキシー用支持体およびその製造方法

絶縁性単結晶炭化ケイ素または絶縁性単結晶窒化ガリウムの層を、導電性単結晶炭化ケイ素または窒化ガリウムの第一の基板中に形成することを含む、エピタキシー用支持体の製造方法である。本発明はまた、前記炭化ケイ素または窒化ガリウムの単結晶層の、1.5W・cm-1・K-1以上の熱伝導度を有する多結晶セラミック材料から形成される第二の基板上への転写を含む。当該方法によれば、特に高周波数電源用途に用いる、高性能電子部品を安価に製造することができる。 (もっと読む)

窒化物系III―V族化合物半導体装置の電極構造

【課題】 半導体上の膜付着力が強く、かつ温度特性が優れたショットキー電極を備えた窒化物系III−V族化合物半導体装置の電極構造を提供する。

【解決手段】 この窒化物系III−V族化合物半導体装置の電極構造は、電極4の材料として金属窒化物(窒化タングステン)を用いたので、半導体GaN層3への膜付着力が強く、かつ、加熱によってショットキー特性が劣化することがないショットキー電極4を得ることができた。

(もっと読む)

1 - 18 / 18

[ Back to top ]