Fターム[5F102GC03]の内容

接合型電界効果トランジスタ (42,929) | ゲート配置 (2,808) | 横型FETの側部ゲート(側面からの空乏層制御) (17)

Fターム[5F102GC03]に分類される特許

1 - 17 / 17

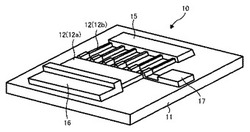

半導体装置

【課題】耐圧を向上させることができる半導体装置を提供する。

【解決手段】半導体装置10は、ソース領域12a、複数の帯状のドレイン領域12b、チャネル領域、ソース電極16、ドレイン電極15、およびゲート電極17を具備する。ソース領域12aは、化合物半導体層11上に形成された平面状の領域である。複数の帯状のドレイン領域12bは、化合物半導体層11上に、互いに電気的に分離されるように形成される。チャネル領域は、ソース領域12aの一辺に接し、かつソース領域12aと複数のドレイン領域12bとの間に、互いに電気的に分離されるように形成される。ソース電極16は、ソース領域12a上の少なくとも一部に形成される。ドレイン電極15は、複数のドレイン領域12bに電気的に接続されるように形成される。ゲート電極17は、複数のチャネル領域に電気的に接続されるように形成される。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】チャネルとなるナノワイアの周囲をゲート電極が取り巻いて形成されているFETが、より容易に高い精度で製造できるようにする。

【解決手段】被覆ナノワイア103を配置した基板121のゲート電極形成領域の上に、被覆ナノワイア103に交差して下部ゲート電極122に重なる上部ゲート電極124を形成する。上部ゲート電極124の形成は、公知のリソグラフィー技術とリフトオフとにより行えばよい。例えば、被覆ナノワイア103が下部ゲート電極122と交差して配置されている基板121の上に、電子ビーム露光により電極形成部に開口を備えるレジストパターンを形成し、この上に、電極材料を堆積する。この後、先に形成してあるレジストパターンを除去すれば、上部ゲート電極124が形成できる。

(もっと読む)

半導体装置

【課題】オフ特性が優れ、ゲート順方向電圧の範囲が広く、かつ、逆方向ブレークダウン電圧を高くすることができる構造の接合型FETを有する半導体装置を提供する。

【解決手段】第一のアンドープ層3上に、第一のアンドープ層3と接して、第一のアンドープ層3のバンドギャップより小さいバンドギャップを有するバンドギャップの小さい半導体層4が設けられ、その両端部と電気的に接続して一対の第一導電型コンタクト層6が設けられ、第一のアンドープ層3の下側に第二導電型コンタクト層2が設けられている。そして、一対の第一導電型コンタクト層6のそれぞれにオーミックコンタクトしてソース電極/ドレイン電極7が、また、第二導電型コンタクト層2にオーミックコンタクトしてゲート電極8がそれぞれ設けられることにより、接合型FETが構成されている。

(もっと読む)

電気回路中にて静電気放電保護素子として用いるためのゲート制御されたフィン型抵抗素子、および、電気回路内部を静電気放電から保護するための保護装置

【課題】電気回路中にて静電気放電保護を確実化しながら小型化を実現する。

【解決手段】電気回路において静電気放電保護素子として使用するためのゲート制御されたフィン型抵抗素子は、第1端子領域、第2端子領域、および、第1端子領域と第2端子領域との間に形成されたチャネル領域を有するフィン構造体を備えている。さらに、フィン型抵抗素子は、チャネル領域の上面の一部上に少なくとも形成されたゲート領域を備えている。ゲート領域は、ゲート制御部に電気的に結合されており、ゲート制御部は、ゲート領域に印加される電気的な電位を制御することにより、電気回路が第1動作状態である間は、ゲート制御されたフィン型抵抗素子の電気抵抗を高くし、静電気放電現象の開始によって特徴付けられている第2動作状態では、電気抵抗をより低くする。

(もっと読む)

半導体装置およびその製造方法

【課題】 炭化珪素の半導体装置において、電極材料と、内部配線の材料とが異なるとき、これら異種金属の接触界面における不具合のおそれを無くして、長期間使用後にも高い信頼性を得ることができる、半導体装置等を提供する。

【解決手段】 炭化珪素14,18に接触する接触電極16と、該接触電極と導通する配線19とを備え、接触電極16が、チタン、アルミニウム、および珪素を含有する合金で形成され、配線19は、アルミニウムまたはアルミニウム合金で形成され、該配線は接触電極と接触することで該接触電極と導通をとることを特徴とする。

(もっと読む)

半導体装置

【課題】優れた特性を有し、IC化に適した起動回路を提供する。

【解決手段】N型エピタキシャル層12に形成され、ドレイン領域121を規定するP型素子分離領域13が形成される。ドレイン領域121内にボディ領域15が形成され、ボディ領域15内にN型ソース領域16が形成される。ドレイン領域121とソース領域16間のチャネル領域上にゲート電極20が配置され、LDMOSが形成される。ドレイン領域121と、ゲートとして機能するP型分離領域13とドレイン領域121に印加される電圧により、P型素子分離領域13が逆バイアスされて空乏層が延びるチャネル領域を介して、JFETのソース引出層23が配置され、JFETが形成される。

(もっと読む)

半導体装置

【課題】起動回路と周辺回路とを併せて集積化し得る半導体装置を提供する。

【解決手段】領域411においては、素子分離領域により規定されるドレイン領域121にボディ領域が形成され、ボディ領域にN型のソース領域が形成される。ドレイン領域121とN型のソース領域との間に第1のゲート電極20が配置される。素子分離領域は開口部133が形成されたループ状部と、開口部133を介してドレイン領域121に接続された延在領域122を規定する部分とを備える。延在領域122に、N型のソース引出領域が形成される。内部回路412においては、ドレイン領域121にP型のボディ領域が形成され、P型のボディ領域にN型のソース領域が形成され、ドレイン領域121とN型のソース領域との間に第2のゲート電極331が形成される。

(もっと読む)

半導体装置の製造方法

【課題】デバイスの性能や信頼性を低下させることなく、注入した不純物を熱処理することができる半導体装置の製造方法を提供する。

【解決手段】下地層であるpGaN層103に形成された注入領域104’上に、GaNのバンドギャップエネルギーよりも小さいバンドギャップエネルギーを有する物質よりなる光吸収膜T1を形成し、この状態で基板101上面から赤外光や赤色光など、pGaN層103のバンドギャップエネルギーよりも小さいエネルギーの所定光を用いてアニールを行う。pGaN層103と比較して光吸収膜T1の方がアニールで使用される光の吸収係数が大きいため、光吸収膜T1直下もしくは近傍の領域(注入領域104’)を選択的に熱処理することが可能となる。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】RFデュアルバンドデバイスとして用いられ、微細化と高性能化をともに実現することが可能な電界効果型トランジスタを提供する。

【解決手段】基板w上に形成され、ソース領域12、ドレイン領域13およびこれらの間に形成されるフィン状領域14を有する化合物半導体層11と、フィン状領域14の第1の側面に形成され、第1の信号が入力される第1のゲート電極16と、フィン状領域14の第2の側面に形成され、第2の信号が入力される第2のゲート電極17を備える。

(もっと読む)

電界効果型トランジスタおよびその製造方法

【課題】本発明は、RFデバイスの高耐圧化、高効率化を実現することが可能な電界効果型トランジスタおよびその製造方法を提供する。

【解決手段】基板w上に形成され、ソース領域12、ドレイン領域13およびこれらの間に形成されるフィン状領域14を有する化合物半導体層11と、フィン状領域14表面に形成されるゲート電極17と、フィン状領域14側面に形成される2段以上のリセス18、19を備える。

(もっと読む)

接合型電界効果トランジスタおよびその製造方法

【課題】チャネル領域を一定の厚さに形成することができる、接合型電界効果トランジスタおよびその製造方法を提供する。

【解決手段】接合型電界効果トランジスタ1では、半導体基板2上に、p型下エピタキシャル層3、n型エピタキシャル層4およびp型上エピタキシャル層5が、半導体基板2側からこの順に積層されている。p型上エピタキシャル層5には、ソース領域7およびドレイン領域9がp型上エピタキシャル層5を層厚方向に貫通して形成されている。ソース領域7およびドレイン領域9は、n型エピタキシャル層4に接続されている。そして、ゲート電極11が、p型下エピタキシャル層3およびp+型領域6を介して、p型上エピタキシャル層5と電気的に接続されることにより、ソース領域7とドレイン領域9との間のp型上エピタキシャル層5は、ゲート領域となっている。

(もっと読む)

高耐圧縦型MOSトランジスタ及び高耐圧縦型MOSトランジスタを用いたスイッチング電源装置

【課題】 電圧制御回路へ電力を供給するための高耐圧で高電力型の抵抗を用いずに、交流電源の投入時に必要な起動用のバイアス電圧を供給することを目的とする。

【解決手段】 第1の導電型の半導体基板10を介して第1の導電型のドリフト領域20と接続する第1のドレイン領域110と第2の導電型の半導体領域に挟まれた第1の導電型のドリフト領域20に形成された第2のドレイン領域331とを備える高耐圧接合型FET284を介して高耐圧縦型MOSトランジスタと電圧制御回路とを接続することにより、高耐圧縦型MOSトランジスタから電圧制御回路に印加される電圧を高耐圧接合型FET284のピンチオフ電圧以下に制御することができるため、電圧制御回路へ電力を供給するための高耐圧で高電力型の抵抗を用いずに、交流電源の投入時に必要な起動用のバイアス電圧を供給することができる。

(もっと読む)

電子デバイス

電子デバイスは、移動電荷キャリアを支持する基板と、該基板面上に形成されてその両側に第1および第2の基板領域を定義し、該第1および第2の基板領域は該絶縁体によって定義される細長いチャネルによって接続され、該チャネルは該第1の領域から該第2の領域への基板内の電荷キャリア流路を提供し、該第1および該第2の基板領域間の伝導度は、この2つの領域間の電位差に依存する。移動電荷キャリアは、基板内の該3つの領域のそれぞれで、少なくとも2つのモード内に存在できる。該基板は有機材料とすることができる。移動電荷キャリアは、0.01cm2/Vs〜100cm2/Vsの範囲の移動度を有することができ、該電子デバイスはRFデバイスであってもよい。それぞれのデバイスの製造方法も開示される。 (もっと読む)

T型構造のナノチューブおよび電界効果トランジスタ並びにそれらの製造方法

【課題】 ナノチューブとナノチューブとがSP3結合で接合されるようにして、チャネルとゲートの双方をナノチューブとするトランジスタを実現できるようにする。

【解決手段】 一対のソース・ドレイン電極27とゲート端子28が形成された基板を用意し〔(a)図〕、ソース・ドレイン電極27の一方に触媒層20を形成する〔(b)図〕。触媒層20を書くとしてCNTを成長させ〔(c)図〕、一対のソース・ドレイン電極27間に第1のCNT23を形成する〔(d)図〕。把持手段25により第2のCNT24を採取し、必要に応じて電子ビームなどを用いてキャップを除去し開口部を清浄化した後、その開口部を第1のCNT23の側面に接触させ、二つのCNTを結合する〔(e)図〕。第2のCNT24の他端をゲート端子28上に位置づける〔(f)図〕。金属イオンを選択的に照射して、CNTの端部を電極、端子上に固定する。

(もっと読む)

半導体装置

【課題】 ノーマリオフで動作するヘテロ接合半導体装置を得ること。

【解決手段】 p型の窒化ガリウムの半導体下層26と、その半導体下層26の表面にヘテロ接合されており、半導体下層26のバンドギャップより大きなバンドギャップを有するn型のAlGaNの半導体上層28と、半導体上層28の表面の一部に形成されているドレイン電極32と、半導体上層28の表面の他の一部に形成されているソース電極34と、半導体下層26に電気的に接しているゲート電極36を備えている。

(もっと読む)

BiCMOSと互換性を有するJFET装置及びその製造方法

エミッタ・アウト拡散、又は縦型バイポーラ装置を形成するために用いられるのと同じ工程で形成されるソース領域及びドレイン領域(17、18)を備えたBiCMOSと互換性があるJFET装置であって、バイポーラ装置内にエミッタ・キャップを形成する半導体層がJFET装置のチャネル(16)を形成し、バイポーラ装置の真性ベース領域を形成する材料層(すなわちベース・エピ・スタック)がJFET装置の真性ゲート領域(14)を形成するJFET装置。その結果、如何なる更なるマスキング又は他の処理ステップの必要なしに、JFET装置の標準的なBiCMOSプロセスへの組み込みが達成される。  (もっと読む)

(もっと読む)

電界効果トランジスタ

【課題】 従来よりもオン電流値を上昇させ、精度の高い回路動作を行なえるようにした、優れた電界効果トランジスタを提供する。

【解決手段】 ゲート絶縁部2に、強誘電体物質を含有するコア部と、常誘電体物質を含有するシェル部とからなるコア・シェル構造粒子を含有させる。

(もっと読む)

1 - 17 / 17

[ Back to top ]