Fターム[5F102GJ01]の内容

接合型電界効果トランジスタ (42,929) | 基板 (5,097) | 半導体材料(半絶縁性材料も含む) (3,925)

Fターム[5F102GJ01]の下位に属するFターム

Fターム[5F102GJ01]に分類される特許

41 - 49 / 49

窒化物半導体素子およびその製法

【課題】 加工性のよい酸化亜鉛系化合物を基板として用いることにより、成長する窒化物半導体の結晶性をよくし、しかも基板の剥離やチップ化を非常に簡単に行うことができる構造の窒化物半導体素子およびその製法を提供する。

【解決手段】 基板1上に窒化物半導体層が積層されて窒化物半導体素子を形成する場合に、基板1がMgxZn1-xO(0<x≦0.5)からなっており、その基板1に接してInyGa1-yN(0≦y≦0.5)からなる第1の窒化物半導体層2が設けられ、その第1の窒化物半導体層2上に半導体素子を形成するように窒化物半導体層3〜7が積層されている。

(もっと読む)

無アルミニウムIII族窒化物ベースの高電子移動度トランジスタおよびその製造方法

無アルミニウム高電子移動度トランジスタ(HEMT)および無アルミニウムHEMTの製造方法が提供される。いくつかの実施形態では、無アルミニウムHEMTが、無アルミニウムIII族窒化物障壁層と、この障壁層上の無アルミニウムIII族窒化物チャネル層と、このチャネル層上の無アルミニウムIII族窒化物キャップ層とを含む。  (もっと読む)

(もっと読む)

半導体装置及び該半導体装置を動作させる方法

本発明は、ドレイン延長部(8)を備えるラテラルDMOSTに特に関する。既知のトランジスタにおいて、更なる金属ストリップ(20)は、ゲート電極コンタクトストリップと、ソース領域コンタクト(15)に電気的に接続されているドレインコンタクト(16)との間に位置される。本特許出願において提案される装置において、更なる金属ストリップ(20)とソースコンタクト(15,12)との間の接続部は、コンデンサ(30)を有し、更なる金属ストリップ(20)は更なる金属ストリップ(20)に電圧を供給するための更なるコンタクト領域(35)を備えている。このようにして、改善された線形性が実現可能であり、当該装置の実用性が、特に、高電力及び高周波数において改善される。好ましくは、コンデンサ(30)は、単一の半導体基体(1)内にトランジスタと一体化されている。本発明は、更に、本発明による装置(10)を動作させる方法を有する。  (もっと読む)

(もっと読む)

縦型有機FET及びその製造方法

有機半導体から成る活性層の分子配向を抑制し、キャリア移動度を向上した縦型有機FETを提供する。本発明は、基板上に少なくともソース電極層、ドレイン電極層、ゲート電極及び活性層が設けられており、ソース電極層、活性層及びドレイン電極層が順に積層した構造を有する縦型有機FETであって、(1)前記ソース電極層及びドレイン電極層が実質的に基板面に対して平行に配置されており、(2)前記ソース電極層及びドレイン電極層が、導電性部材からなり、(3)前記活性層が、中心原子として4価又は6価の元素をもち、かつ、分子面の上下方向からそれぞれ配位子X1及びX2が配位したフタロシアニン系化合物から実質的に構成され、(4)前記化合物の各分子の分子面がソース電極層及びドレイン電極層の少なくとも一方に対して平行状態となるように、前記化合物が積層されている、縦型有機FETに係る。  (もっと読む)

(もっと読む)

窒化物ベースの集積音波デバイスおよび窒化物ベースの集積音波デバイスを製造する方法

モノリシック電子デバイスは、基板と、基板上に形成された半絶縁圧電III族窒化物エピタキシャル層と、エピタキシャル層上に表面弾性波デバイスを形成する一対の入力および出力インターディジタル変換器と、基板上に形成された少なくとも1つの電子デバイス(HEMT、MESFET、JFET、MOSFET、フォトダイオード、LEDなど)とを含む。電子デバイスをSAWデバイスから、反対にSAWデバイスを電子デバイスから電気的かつ音響的に分離するための分離手段が開示される。いくつかの実施形態ではSAWデバイスと電子デバイスとの間にトレンチが形成される。さらに、その上にSAWデバイスを製造することができる半絶縁III族窒化物エピタキシャル層を形成するためのイオン注入が開示される。インターディジタル変換器に隣接した吸収および/または反射部品が、SAWデバイスの動作を妨害する可能性がある不要な反射を低減させる。  (もっと読む)

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】P型領域と、N型領域とを備え、電子キャリア濃度が1018/cm3未満である非晶質酸化物、又は電子キャリア濃度が増加すると共に、電子移動度が増加する傾向を示す非晶質酸化物をN型領域に用いている。電子キャリア濃度が1018/cm3未満である非晶質酸化物又は電子キャリア濃度が増加すると共に、電子移動度が増加する傾向を示す非晶質酸化物からなる第1領域と、第1領域に対してヘテロ接合を形成する第2領域と、を具備する。

(もっと読む)

半導体装置とその製造方法

【課題】 結晶欠陥が存在する半導体層を備える半導体装置において、低耐圧化の抑制あるいはリーク電流の発生の抑制を実現する。

【解決手段】 電源の一方の極性に接続するドレイン電極22及び半導体基板32と、非被覆領域55を残して半導体基板32の表面を被覆している電流規制層42と、その電流規制層42の表面を被覆している半導体層(ドリフト層56、チャネル層54、ソース層52)と、ソース層52の表面に形成されており、電源の他方の極性に接続するソース電極62を備えている。

(もっと読む)

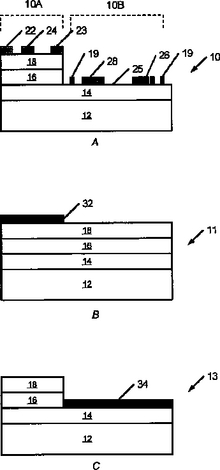

アンチモンベースの化合物半導体構造物におけるメサ分離をエッチングする方法

アンチモンベースのバッファ層(24)とアンチモンベースのバッファキャップ(26)を含む基板構造物(10)上にアンチモンベースの半導体装置を形成する。この基板構造物(10)の上に形成された多層エピタキシャル層(30〜42)をドライエッチングしてデバイスメサ(12)を形成し、バッファキャップ(26)はメサの周りに所望の平滑なメサフロアと電気素子分離を提供する。 (もっと読む)

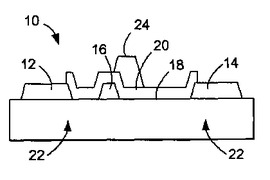

シングルゲートまたはマルチゲートフィールドプレート製造

電界効果型トランジスタの表面に、誘電性材料の堆積/成長させ、誘電性材料をエッチングし、および、メタルを蒸着させる、連続的なステップを用いる、シングルゲートまたはマルチゲートプレートの製造プロセス。本製造プロセスのは、誘電性材料の堆積/成長が、典型的には、非常によく制御できるプロセスなので、フィールドプレート動作を厳しく制御できる。さらに、デバイス表面に堆積された誘電性材料は、デバイスの真性領域から除去される必要はない。このため、乾式または湿式のエッチングプロセスで受けるダメージの少ない材料を用いることなく、フィールドプレートされたデバイスを、実現することができる。マルチゲートフィールドプレートを使うと、マルチ接続を使用するので、ゲート抵抗を減らすこともでき、こうして、大周辺デバイスおよび/またはサブミクロンゲートデバイスの性能を向上することができる。  (もっと読む)

(もっと読む)

41 - 49 / 49

[ Back to top ]