Fターム[5F102GM01]の内容

接合型電界効果トランジスタ (42,929) | ゲート下介在層(ゲートメタル電極底面とチャネル層表面間に介在する層) (3,125) | 単一半導体層 (2,140)

Fターム[5F102GM01]の下位に属するFターム

Fターム[5F102GM01]に分類される特許

21 - 26 / 26

III族酸化物半導体を含む半導体素子

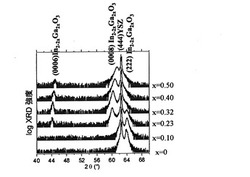

【課題】 禁制帯幅の制御が可能な六方晶構造を有するIII族酸化物半導体を見出し、これを含む半導体素子、光電変換素子、紫外線検出素子、酸化物発光素子、発光素子を提供することにある。

【解決手段】 A2O3なる構成を有するIII族酸化物を含む半導体素子において、薄膜技術を用いてAの元素がIn、Ga、アルミニウムAl、ボロンBの少なくとも二つを固溶させた混晶半導体薄膜を有するようにした。バルクでの熱力学的固溶限界域を超えた組成での固溶体薄膜、熱力学的に不安定な六方晶構造を有する混晶薄膜を得ることが出来る。

(もっと読む)

半導体デバイス

【課題】通常の気体または液体センサの動作環境に耐えることができる半導体デバイスを提供する。

【解決手段】本発明の半導体デバイスは、基板12上に、第1の半導体酸化物材料層14と、前記第1の半導体酸化物材料層上に形成された第2の半導体酸化物材料層16であって、二次元電子ガスが前記第1および第2の材料間の界面に生成されるように形成された第2の半導体酸化物材料層16と、外面上の保護層18と、を含む構造を有し、さらに、ソース接点20とドレイン接点22とを含む。

(もっと読む)

3つの電界効果トランジスタを有するモノリシック集積回路

半導体構造であって:III-V基板構造;構造の第一の領域に配置されたエンハンスメント型トランジスタデバイス;構造の横に転置された第二の領域に配置されたデプリーション型トランジスタデバイス;および、それの横に転置された第三の領域に形成されたRF/マイクロ波/ミリ波トランジスタデバイス;を有する前記半導体構造。  (もっと読む)

(もっと読む)

高性能FETデバイス及び方法

【課題】半導体FETデバイスの機能及び高周波性能を改善するために用いることができる、ゲート電圧バイアス供給回路素子を備えたエピタキシャル積層構造を提供する。

【解決手段】半導体電界効果トランジスタ(FET)デバイスの性能を改善するためのゲート電圧バイアス供給回路素子を備えたエピタキシャル積層構造は、基板と、該基板上にエピタキシャルに成長したn型またはp型の第1の層の半導体膜であって、基板と第1の層膜との間にバッファ層が存在する可能性がある第1の層の半導体膜と、第1の半導体層上にエピタキシャルに成長した活性半導体層であって、活性層の導電型が第1の半導体層の導電型と反対であり、またFETを形成するのに十分なゲート、ドレイン、ソースへの電気コンタクトを備えたゲート領域及びドレイン領域及びソース領域を有する活性半導体層と、基板または第1の半導体層上の電気コンタクトと、デバイス性能を向上させるのに十分な電圧極性及び大きさで、ゲートコンタクト及び基板または第1の半導体層に電気的に接続されたゲート電圧バイアス供給回路素子と、からなる構造を利用する。  (もっと読む)

(もっと読む)

電界効果トランジスタ

【課題】 従来よりもオン電流値を上昇させ、精度の高い回路動作を行なえるようにした、優れた電界効果トランジスタを提供する。

【解決手段】 ゲート絶縁部2に、強誘電体物質を含有するコア部と、常誘電体物質を含有するシェル部とからなるコア・シェル構造粒子を含有させる。

(もっと読む)

電界効果トランジスタ

【課題】 電界効果トランジスタのキャリアの移動度を向上させる。

【解決手段】 電界効果トランジスタに、強誘電性及び強磁性をともに有する物質を含有する絶縁部16と絶縁部16に対向して設けられ強磁性を少なくとも有する物質を含有する強磁性部14とを設ける。

(もっと読む)

21 - 26 / 26

[ Back to top ]