Fターム[5F102GM02]の内容

接合型電界効果トランジスタ (42,929) | ゲート下介在層(ゲートメタル電極底面とチャネル層表面間に介在する層) (3,125) | 単一半導体層 (2,140) | 4族 (57)

Fターム[5F102GM02]に分類される特許

1 - 20 / 57

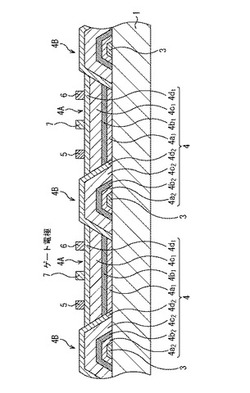

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

炭化ケイ素金属半導体電界効果トランジスタ及び炭化ケイ素の金属半導体電界効果トランジスタを製造する方法

【課題】深いレベルのドーパントがほとんど存在しない半絶縁性のSiC基板上にMESFETを形成することにより、バックゲート効果が減少された、SiCのMESFETを提供する。

【解決手段】半絶縁性の基板上10に選択的にドープされたP型の炭化珪素の層13、及びN型のエピタキシャル層14を積層し、背面ゲート効果を減少させる。また2つの凹部を有するゲート構造体も備える。これにより、出力コンダクタンスを1/3に減少することができ、また電力のゲインを3db増加することができる。クロム42をショットキーゲート接点として利用することもでき、酸化物−窒化物−酸化物(ONO)の保護層60を利用して、MESFET内の表面効果を減少させる。また、ソース及びドレインのオーム接点をn型チャネル層上に直接形成して、これにより、n+領域を製造する必要がなくなる。

(もっと読む)

ブール成長された炭化ケイ素ドリフト層を使用してパワー半導体デバイスを形成する方法、およびそれによって形成されるパワー半導体デバイス

【課題】炭化ケイ素の好ましい電気特性にもかかわらず、その中においてより厚い電圧サポート領域を有する炭化ケイ素パワーデバイスの必要性が引き続き存在している。

【解決手段】高電圧炭化ケイ素パワーデバイスを形成する方法は、法外に高いコストのエピタキシャル成長された炭化ケイ素層の代わりに、高純度炭化ケイ素ウエハ材料から得られる高純度炭化ケイ素ドリフト層を利用している。本方法は、約100μmより厚い厚みを有するドリフト層を使用して10kVを超えるブロッキング電圧をサポートすることができる少数キャリアパワーデバイスと多数キャリアパワーデバイスの両方を形成することを含んでいる。これらのドリフト層は、その中に約2×1015cm−3未満である正味n型ドーパント濃度を有するブール成長炭化ケイ素ドリフト層として形成される。このn型ドーパント濃度は、中性子変換ドーピング(NTD)技法を使用して実現することができる。

(もっと読む)

炭化珪素半導体装置

【課題】従来よりオン抵抗が低くかつ高い耐圧を有する炭化珪素半導体装置を提供する。

【解決手段】この発明に従ったJFET10は、n型基板11と、p型層2、12と、n型層13と、ソース領域15と、ドレイン領域17と、ゲート領域16とを備える。n型基板11は、{0001}面に対するオフ角が32°以上である主表面11Aを有し、炭化珪素(SiC)からなる。p型層2、12は、n型基板11の主表面11A上に形成され、導電型がp型である。n型層13は、p型層2、12上に形成され、導電型がn型である。ソース領域15およびドレイン領域17は、n型層13において、互いに間隔を隔てて形成され、導電型がn型である。ゲート領域16は、n型層13において、ソース領域15とドレイン領域17との間の領域に形成され、導電型がp型である。

(もっと読む)

半導体素子および半導体デバイス

【課題】オン抵抗が比較的低く大電流にも対応可能という特性を持ちながら、光照射強度に応じて電流を変化させることができる半導体素子および半導体デバイスを提供する。

【解決手段】電子走行層14における電子供給層15との界面には動作時にチャネルとなる2次元電子ガス領域16が形成される。2次元電子ガス領域16におけるドレイン電極11とソース電極12との間の一部には、空乏化部18により空乏化された空乏領域17が形成されている。半導体素子1は、空乏領域17に光を照射しない状態で、2次元電子ガス領域16の空乏領域17が空乏化しているため、ドレイン電極11・ソース電極12間が非導通となる。一方、半導体素子1は、電子走行層14のバンドギャップよりも大きなエネルギを持つ光を空乏領域17に受けた状態で、空乏領域17に電子20と正孔とが生成されることでドレイン電極11・ソース電極12間が導通する。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】凹部4c内に形成されたi型(イントリンシック半導体)側壁層5を介してp+型ゲート領域6を形成する。このような構成とすれば、n+型層4とp+型ゲート領域6との間にさらにp+型ゲート領域6よりも低濃度のp-型層が必要とされない。このため、n-型チャネル層3に直接接触している高濃度のp+型ゲート領域6によって、n-型チャネル層3内に伸びる空乏層幅を制御できる。したがって、n+型層4とp+型ゲート領域6との間にさらにp-型層が備えられる場合と比較して、ゲート印加電圧が高電圧になることを抑制できる。また、p+型ゲート領域6の側面がi型側壁層5によってn+型層4と分離されるため、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスを低減できる。

(もっと読む)

半導体装置およびその製造方法

【課題】DモードとEモードの素子を組み合わせた半導体装置およびその製造方法を提供する。

【解決手段】DモードとEモードのJFETにおけるチャネル領域を設定する場所にそれぞれ凹部2aと凸部2bを備えることで、同一基板上に厚みが異なるn型チャネル層3を形成する。そして、このような厚みが異なるn型チャネル層3によってDモードとEモードで作動するJFETを同一基板上に備えることができるため、SiCでもDモードとEモードのJFETを組み合わせたSiC半導体装置を実現することが可能となる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ると共に、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】p+型ゲート領域2をSiC基板1の内部に埋め込んだ構造とする。これにより、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減を図ることが可能となる。また、p+型ゲート領域2がn-型チャネル層3に直接接触させられる構造であるため、p+型ゲート領域2から広がる空乏層によって容易にn-型チャネル層3をピンチオフさせることができ、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制できる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部の周辺を含めてn+型SiC基板1の外縁部においてn+型ソース領域4が除去されると共に、トレンチ6の先端部においてn-型チャネル層7および第2ゲート領域8が除去された凹形状とする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル層の厚みのバラツキを抑制できるJFET、MOSFETもしくはMESFETを備えた半導体装置およびその製造方法を提供する。

【解決手段】n+型層3に対して異方性エッチングを行うことによって凹部4を形成したのち、この凹部4内にエピタキシャル成長させることによってn型チャネル層5を形成する。これにより、n型チャネル層5を一定の膜厚かつ一定の濃度で形成することが可能となる。このため、従来の構造と異なり、n型チャネル層5の膜厚が一定なバラツキのない構造とすることが可能となる。したがって、JFETの特性も一定とすることが可能となる。

(もっと読む)

量子井戸デバイスにおける平行伝導を改善する装置及び方法

平行伝導を改善する量子井戸デバイスを提供する方法及び装置の実施形態が主に記載される。その他の実施形態についても、記載及び特許請求される。 (もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ショットキー接触を発生させることなく、炭素の析出を抑制することにより配線の密着性を向上したオーミック電極を有する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】

SiC半導体装置においてオーミック電極を形成する際に、SiC層11の一方の主表面上には、1種の第1の金属元素からなる、第1の金属層12を形成する。また、第1の金属層の、SiC層11と対向する表面とは反対側の表面上(図1における上側)に、SiからなるSi層13を形成する。このようにして形成した積層構造10Aに対して熱処理を行なう。以上により、電極の表面層への炭素原子の析出や、SiとSiCとによるショットキー接触の形成が抑制された、配線との良好な密着性を示すオーミック電極を有する炭化珪素半導体装置を得ることができる。

(もっと読む)

炭化ケイ素半導体装置および炭化ケイ素半導体装置の製造方法

【課題】チャネルの低い抵抗を維持するとともに、ドリフト層の高い耐圧を維持するSiC半導体装置およびSiC半導体装置の製造方法を提供する。

【解決手段】SiC半導体装置は、SiC基板101、第1半導体層、ベース領域105、第2半導体層、ゲート領域109およびソース領域113を備えている。SiC基板101は、{0001}面に対して30°以上60°以下傾斜した主面101aを有する。第1半導体層は、主面101a上に形成される。ベース領域105は、表面103aの一部に形成される。第2半導体層は、表面103a上に形成される。ゲート領域109は、表面107aの一部に形成され、第2半導体層を挟んでベース領域105と対向する位置に形成される。ソース領域113は、表面107aの一部に形成され、ゲート領域109と隣り合い、かつベース領域105と対向する位置に形成される。

(もっと読む)

接合型電界効果トランジスタの駆動装置および駆動方法

【課題】簡単な構成によって、一時的な過電流による接合型電界効果トランジスタの発熱を抑制するとともに、接合型電界効果トランジスタの過熱状態を検知することができる接合型電界効果トランジスタの駆動装置および駆動方法を提供する。

【解決手段】電流検知部90でモニタする電流が閾値電流を超えた場合、接合型電界効果トランジスタ(JFET)32をターンオンするときのゲート電圧をPN接合のビルトイン電圧より大きくする。これにより、JFET32のオン抵抗を低減させてJFET32の発熱を抑制する。さらに、オン状態のJFET32に流れるゲート電流IGの温度依存性を利用することによって、JFET32の温度の値を簡単に求めることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 二次元電子ガスを発生させるワイドギャップ半導体層をその下の半導体層の構成元素の化合物半導体により形成することにより、非常に立上り電圧が低く、かつ、逆方向耐圧が高いダイオードまたはHEMT構造のMIS型トランジスタを有する半導体装置およびその製造方法を提供する。

【解決手段】 GaAs基板1上に、GaAs基板1よりもバンドギャップおよびキャリア濃度が共に大きく、GaAs基板1の表面に二次元電子ガスを生じさせることが可能で、かつ、その二次元電子ガスの電子をトンネル可能な厚さに形成されるN型のGaN層2が設けられ、そのGaN層2と電気的に接続して第1電極3が、GaAs基板1に電気的に接続して第2電極4が設けられている。

(もっと読む)

伝導を高めた非パンチスルー半導体チャネルを有する半導体デバイス及びその製法

デバイスにおける電流フローが整流接合(例えば、p−n接合又は金属半導体接合)の間で制限される、半導体デバイスが記載される。デバイスは、非パンチスルー挙動と高められた電流伝導能力を提供する。デバイスは、接合型電界効果トランジスタ(JFETs)、静電誘導トランジスタ(SITs)接合型電界効果サイリスタ、又はJFET電流制限器などのような電力半導体デバイスである。デバイスは、炭化ケイ素(SiC)等の広バンドギャップでできている。いくつかの実施形態において、デバイスは、常時オフ型SiC垂直接合型電界効果トランジスタである。デバイス及びデバイスを備える回路を製造する方法もまた記載される。 (もっと読む)

半導体装置

【課題】基板の結晶面方位を規定して表面の微細な凹凸を抑制した炭化珪素基板上のエピタキシャル相に半導体装置を形成することによって、その電気的特性を改善する。

【解決手段】炭化珪素半導体基板上に形成する半導体装置として、基板の(000−1)面から0°超で以上1°未満傾斜した面上に成長したエピタキシャル層に、P型あるいはN型領域をイオン注入により選択的に形成して製造したダイオード、トランジスターなどとする。

(もっと読む)

接合型電界効果トランジスタ

【課題】 基板が低濃度の半導体基板のみからなるJ−FETは、静電破壊耐量は高いが、ノイズ電圧が大きく、ノイズ特性のばらつきも大きい問題があった。一方、ノイズ対策として、高濃度の半導体基板に低濃度の半導体層を積層した基板構造のJ−FETでは、ゲート抵抗の低減によりノイズ電圧を小さくできノイズ特性も安定する反面、静電破壊耐量が劣化する問題があった。

【解決手段】 高濃度半導体基板の条件を、所望の静電破壊耐量が得られる比抵抗及び厚みとし、これに低濃度の半導体層を積層した基板構造とする。これにより静電破壊耐量を劣化させない範囲でノイズ特性のばらつきを抑え、ノイズ電圧を小さくすることができる。また同時にノイズ特性に影響を与えない範囲で静電破壊耐量を向上させることができる。従って、従来構造と比較して市場要求に比較的柔軟に対応できるJ−FETを提供できる。

(もっと読む)

接合型電界効果トランジスタ

【課題】 基板が低濃度の半導体基板のみからなるJ−FETは、静電破壊耐量は高いが、ノイズ電圧が大きく、ノイズ特性のばらつきも大きい問題があった。一方、ノイズ対策として、高濃度の半導体基板に低濃度の半導体層を積層した基板構造のJ−FETでは、ゲート抵抗の低減によりノイズ電圧を小さくできノイズ特性も安定する反面、静電破壊耐量が劣化する問題があった。

【解決手段】 高濃度半導体基板に低濃度の第1半導体層と、第1半導体層より高濃度の第2半導体層を積層する基板構造とする。これにより静電破壊耐量を劣化させない範囲でノイズ特性のばらつきを抑え、ノイズ電圧を小さくすることができる。また同時にノイズ特性に影響を与えない範囲で静電破壊耐量を向上させることができる。従って、従来構造と比較して市場要求に比較的柔軟に対応できるJ−FETを提供できる。

(もっと読む)

選択エピタキシャル成長を用いた横型接合型電界効果トランジスタの製造方法

接合型電界効果トランジスタ(JFET)などの半導体素子を製造する方法が記載される。方法は、自己整合であり、素子のゲート又はソース/ドレイン領域を形成するために、再成長マスク物質を用いた、選択的エピタキシャル成長に関する。方法は、イオン注入の必要性を除去する。素子は、SiCなどのワイドギャップ半導体物質から形成される。再成長マスク物質は、TaCである。素子は、放射線及び/または高温にさらされることを含む過酷な環境において使用される。 (もっと読む)

1 - 20 / 57

[ Back to top ]