Fターム[5F102GQ05]の内容

接合型電界効果トランジスタ (42,929) | ヘテロ接合近傍の2次元キャリア層を導電路に利用するもの(H) (2,045) | 多層ヘテロ構造 (11)

Fターム[5F102GQ05]の下位に属するFターム

Fターム[5F102GQ05]に分類される特許

1 - 8 / 8

半導体装置

【課題】ノーマリオフで動作するとともに、高い耐圧と低いオン抵抗を具備した半導体装置を提供すること。

【解決手段】 半導体装置1では、ドレイン電極21が第1ヘテロ接合面32に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ソース電極29が第1ヘテロ接合面32に形成される2次元電子ガス層から電気的に絶縁可能に構成されているとともに第2ヘテロ接合面34に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ゲート部28が第2ヘテロ接合面34に対向しており、導通電極25が第1ヘテロ接合面32及び第2ヘテロ接合面34に形成される2次元電子ガス層の双方に対して電気的に接続可能に構成されている。第1ヘテロ接合面32に形成される2次元電子ガス層の電子濃度は、第2ヘテロ接合面34に形成される2次元電子ガス層の電子濃度よりも濃い。

(もっと読む)

半導体装置

【課題】複数のチャネルを有する窒化物半導体装置において、ノーマリオフかつ低オン抵抗を実現する技術を提供する。

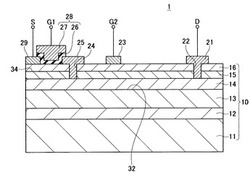

【解決手段】第1の窒化物半導体層3,5,7と、第1の窒化物半導体層よりも禁制帯幅が大きい第2の窒化物半導体層5,6,8とが積層されたヘテロ接合体を少なくとも2つ以上有する窒化物半導体積層体10を備え、窒化物半導体積層体10に設けられたドレイン電極14と、ソース電極13と、ドレイン電極14とソース電極13の両者に対向して設けられたゲート電極15,16とを有し、ドレイン電極14とソース電極13は、窒化物半導体積層体10の表面または側面に配置され、ゲート電極15,16は、窒化物半導体積層体10の深さ方向に設けられた第1ゲート電極15と、該第1ゲート電極15と窒化物半導体積層体10の深さ方向の配置深さが異なる第2ゲート電極16とを有する。

(もっと読む)

半導体装置

【課題】電子が第1励起準位に存在する割合が増えても、量子井戸層の中の電子の有効質量が軽くなる井戸層にできるだけ多くの電子が存在するようにして、より一層の高速化を実現する。

【解決手段】半導体装置を、基板10の上方に設けられた第1半導体層11と、第1半導体層11の上側に接する電子走行層24と、電子走行層24の上側に接する第2半導体層17(25)とを備えるものとし、電子走行層を24、第1井戸層13、中間障壁層14、第2井戸層15を順に積層させた構造を含む2重量子井戸層とし、中間障壁層14の伝導帯のエネルギーが、第1半導体層11及び第2半導体層17(25)の伝導帯のエネルギーよりも低くなり、第1井戸層13及び第2井戸層15の中に基底準位が形成され、2重量子井戸層の中に第1励起準位が形成されるようにする。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗の上昇を抑制しつつ閾値電圧を大きくできる電界効果トランジスタを提供する。

【解決手段】キャリア走行層13である第1窒化物半導体層13と、第1窒化物半導体層13の上に設けられた、第1窒化物半導体層よりもバンドギャップエネルギーの大きい第2窒化物半導体層14と、第2窒化物半導体層14の上に順に設けられた、InGaN16層と、p型窒化物半導体層18と、ゲート電極22とを備える電界効果トランジスタであって、InGaN層16は、ゲート電極22直下の表面に第1の凹部19を有する。これにより、オン抵抗を一定に抑えつつ、閾値電圧を大きくすることができ、ノーマリオフ型のトランジスタが実現できる。

(もっと読む)

量子井戸デバイスにおける平行伝導を改善する装置及び方法

平行伝導を改善する量子井戸デバイスを提供する方法及び装置の実施形態が主に記載される。その他の実施形態についても、記載及び特許請求される。 (もっと読む)

電界効果トランジスタ

【課題】低オン抵抗のFETを提供する。

【解決手段】本発明のFETは、第1の窒化物半導体層103と、第1の窒化物半導体層103の上に形成され、第1の窒化物半導体層103よりもバンドギャップエネルギーが大きい第2の窒化物半導体層104と、第2の窒化物半導体層104の上に形成された第3の窒化物半導体層105と、第3の窒化物半導体層105の上に形成され、第3の窒化物半導体層105よりもバンドギャップエネルギーが大きい第4の窒化物半導体層106とを備え、第1の窒化物半導体層103及び第2の窒化物半導体層104のヘテロ接合界面には、チャネルが形成される。

(もっと読む)

III−V族化合物半導体装置

【課題】 バッファ構造を適切にすることにより、低電圧印加時のリーク電流の低減(1×10-9A以下)を図り、高耐圧化と高性能化を実現した電界効果トランジスタを提供することにある。

【解決手段】 半絶縁性基板1上に、下層から順にバッファ層2、活性層、コンタクト層を有する電界効果トランジスタ用エピタキシャルウエハにおいて、バッファ層2が複数層から成り、その複数層のうちの最下層2aとしてp型のAlxGa1-xAs(0.3≦x≦1)からなるp型バッファ層を設け、このp型バッファ層の膜厚とp型バッファ層のp型キャリア濃度との積が、1×1010〜1×1012/cm2の範囲にあるようにする。

(もっと読む)

シリコン−ゲルマニウム合金及びシリコン−カーボン合金を用いるヘテロ接合電界効果トランジスタ

シリコン−ゲルマニウムバッファ層及びシリコン−カーボンチャネル層構造を用いて製造された半導体素子、例えばヘテロ接合電界効果トランジスタ。本発明は、例えば合金のSi格子中に実質的に組み入れられた約1.5原子%よりも少ないCを含むシリコン−カーボン合金の歪シリコンチャネル層を形成することによって、上部に歪シリコンチャネル層が形成されたSiGe緩和バッファ層における減少されたゲルマニウム含有量を介して貫通欠陥密度を減少させる方法を提供する。  (もっと読む)

(もっと読む)

1 - 8 / 8

[ Back to top ]