Fターム[5F102GR16]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | ソース、ドレインの不純物プロファイル又は形状 (109) | LDD構造(チャネルとの間に中間濃度領域形成) (12)

Fターム[5F102GR16]に分類される特許

1 - 12 / 12

半導体装置、半導体基板、半導体装置の製造方法、及び半導体基板の製造方法

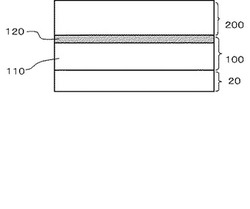

【課題】エピタキシャル層に残存する転位の数を少なくする。

【解決手段】第2エピタキシャル層200は、第1エピタキシャル層100上にエピタキシャル成長している。第1エピタキシャル層100は、エピタキシャル成長層110及び欠陥層120を有している。欠陥層120は、エピタキシャル成長層110の上、かつ、第1エピタキシャル層100の表層に位置している。欠陥層120の欠陥密度は、5×1017cm−2以上である。欠陥層120を突き抜けた欠陥は、第2エピタキシャル層200の内部でループを形成している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置について、小型化を図りつつ、ドレイン耐圧を向上する。

【解決手段】ゲート電極20と、ゲート電極20と離間するソース電極24と、平面視でゲート電極20からみてソース電極24の反対側に位置し、かつゲート電極20と離間するドレイン電極22と、平面視でゲート電極20とドレイン電極22の間に位置し、絶縁膜26を介して半導体基板10上に設けられ、かつゲート電極20、ソース電極24およびドレイン電極22と離間する少なくとも一つのフィールドプレート電極30と、絶縁膜26中に設けられ、かつフィールドプレート電極30と半導体基板10を接続する少なくとも一つのフィールドプレートコンタクト40と、を備え、平面視でフィールドプレート電極30は、フィールドプレートコンタクト40からソース電極24側またはドレイン電極22側の少なくとも一方に延伸している。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】基板と、基板上に形成されたHEMT積層物と、を備え、HEMT積層物は、2DEGを含む化合物半導体層と、化合物半導体層より分極率の大きい上部化合物半導体層と、上部化合物半導体層上に備えられたソース電極、ドレイン電極及びゲートと、を備え、基板は、シリコン基板より誘電率及び熱伝導度の高い窒化物基板であるHEMT。該基板は、シリコン基板より誘電率及び熱伝導度の高い絶縁層、この絶縁層に蒸着された金属層及びこの金属層に付着されたプレートを備える。

(もっと読む)

伝導帯電子チャネルと単一端子応答を有する電界効果トランジスタ

【課題】伝導帯電子チャネルと単一端子応答を有する電界効果トランジスタを提供する。

【解決手段】本発明は、単一端子トランジスタ装置に関する。一具体例において、nチャネルトランジスタは、離散正孔準位H0を有する第一半導体層と、伝導帯底EC2を有する第二半導体層と、第一半導体層と第二半導体層の間に配置される広バンドギャップ半導体バリア層と、第一半導体層の上方のゲート誘電層と、ゲート誘電層の上方にあり、ゼロバイアスを加え、n端子特徴を得るために、離散正孔準位H0が伝導帯底Ec2の下方に位置するように選択された有効仕事関数を有するゲート金属層と、からなる。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタは、基板1、チャネル層3及びバリア層4と、バリア層4上にこの順で離間して設けられたソース電極6、ゲート電極7およびドレイン電極8とを備え、ソース電極6の直下に第1のn型不純物拡散領域12が設けられ、ドレイン電極8の直下に第2のn型不純物拡散領域13が設けられ、第2のn型不純物拡散領域の下側の前記チャネル層3および第2のn型不純物拡散領域の前記ゲート電極側の前記チャネル層3および前記バリア層4に第3のn型不純物拡散領域15が設けられる。第3のn型不純物拡散領域15は第2のn型不純物拡散領域13よりも低いn型不純物濃度を有し、ゲート電極とドレイン電極との間に電圧が印加されたときバリア層4およびチャネル層3においてその絶縁破壊強度を超える電界集中が生じることを抑制する。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタ製造方法

【課題】ゲート電極材料の耐熱上の問題を克服し、ソース抵抗の低減が可能な電界効果トランジスタを提供する。

【解決手段】ゲート電極9を挟んでソース電極8、ドレイン電極10をそれぞれ形成するソース領域3、ドレイン領域6のいずれか一方または双方の領域にイオンを注入し活性化した第1の高濃度キャリア領域6と、ゲート電極9の直下に形成したチャネル領域4と第1の高濃度キャリア領域6との間の領域に、熱処理によりキャリアを拡散させた熱拡散領域7の第2の高濃度キャリア領域とを形成し、第1の高濃度キャリア領域6は、チャネル領域4と互いに隣接して形成される第2の高濃度キャリア領域7と隣接および/または一部重複し、かつ、チャネル領域4以上に深く形成した第2の高濃度キャリア領域7よりも深く形成する。第1の高濃度キャリア領域6のキャリア濃度を、チャネル領域4よりも高濃度の第2の高濃度キャリア領域7よりさらに高くする。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性及びチャネル移動度が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化化合物半導体からなる電界効果トランジスタであって、基板上に形成されたi型または所定の導電型を有する半導体層と、エピタキシャル成長によって半導体層とソース電極およびドレイン電極のそれぞれとの間に形成された、所定の導電型とは反対の導電型を有するコンタクト層と、エピタキシャル成長によってドレイン電極側のコンタクト層と半導体層との間にゲート電極と重畳するように形成された、所定の導電型とは反対の導電型を有するとともに該コンタクト層よりもキャリア濃度が低い電界緩和層と、エピタキシャル成長によって半導体層上の電界緩和層に隣接する領域に形成された、i型または所定の導電型を有する媒介層と、媒介層上に形成したゲート絶縁膜と、を備える。

(もっと読む)

パワー電界効果トランジスタ

寄生NPNなしでバルクシリコンからの電流フローを許容する、非常に短いチャネルを有するハイブリッドパワー電界効果トランジスタ(FET)装置。装置は、JFETコンポーネント、JFETコンポーネントに近接して配置された第1の蓄積型MOSFET、およびトレンチ端の底部のJFETコンポーネントに近接して配置された第2の蓄積型MOSFETまたはソースに接続する絶縁ゲートを有するMOSFETを含む。 (もっと読む)

半導体装置の製造方法

【課題】寸法制御が容易で特性の安定したLDD構造を有するFETなどの半導体装置の製造方法及びその製造方法によって得られる半導体装置を提供する。

【解決手段】この発明におけるLDD構造を有する半導体装置の製造方法は、レジスト寸法の増大にパターンシュリンク剤を用いる。そして、レジスト3とパターンシュリンク剤6との架橋反応を制御することでLDD構造形成部分の寸法の制御を容易にし、特性の安定した半導体装置を得るものである。

(もっと読む)

ドレインおよび/またはソース変形注入物を有するJFET

本発明は、製作中に追加の注入物を受け取るJFETを提供する。この注入物は、JFETのドレイン領域をそのソース領域の方へ延ばし、かつ/またはそのソース領域をそのドレイン領域の方へ延ばす。注入物は、ドレイン/チャネル(および/またはソース/チャネル)接合部で所与のドレイン電圧および/またはソース電圧に対して普通なら生じるはずの電界の大きさを低減させ、それによって電界に関連するゲート電流および降伏の問題の重大度を軽減する。JFETのゲート層は、各注入物に対して、ゲート層の横方向の境界とドレイン領域および/またはソース領域との間にそれぞれ間隙を設ける幅を有するように寸法設定され、各注入物がそれぞれの間隙内に注入されることが好ましい。 (もっと読む)

電界効果トランジスタ及びその製造方法

【課題】十分に大きな電流密度を得ることができるノーマリオフ型の窒化物半導体からなる電界効果トランジスタ及びその製造方法を提供する。

【解決手段】基板101上にAlNバッファ層102、アンドープGaN層103、アンドープAlGaN層104、p型GaN層105、高濃度p型GaN層106が順に形成され、ゲート電極111が高濃度p型GaN層106とオーミック接合する。アンドープAlGaN層104の上にはソース電極109及びドレイン電極110が設けられる。アンドープAlGaN層104とアンドープGaN層との界面で発生する2次元電子ガスとp型GaN層105とによって生じるpn接合がゲート領域に形成されるのでゲート電圧を大きくすることができる。

(もっと読む)

化合物半導体装置

【課題】 移動体通信端末のパワーアンプ等に用いる化合物半導体装置に関し、しきい値電圧が高く、また利得も大きい化合物半導体装置を提供する。

【解決手段】 半絶縁性GaAs基板10と、前記半絶縁性GaAs基板10上に形成されたバッファ層12と、前記バッファ層12上に形成され、InGaAs層である電子走行層14と、前記電子走行層14上に形成され、厚さが10nm程度に薄いAlGaInAs層である緩和層16と、前記緩和層16上に形成され、厚さが20nm程度に薄く、Alの組成比が前記緩和層16より大きいAlGaAs層である障壁層18とを有している。

(もっと読む)

1 - 12 / 12

[ Back to top ]