Fターム[5F110EE24]の内容

Fターム[5F110EE24]に分類される特許

401 - 404 / 404

極薄SOI/SGOI基板上の超高速SI/SIGE変調ドープ電界効果トランジスタ

【課題】 MODFETデバイス構造体の製作における横及び垂直方向の縮小に伴う困難を克服するMODFETデバイス構造体の縮小技術を提供する。

【解決手段】 シリコン及びシリコンゲルマニウム・ベースの半導体MODFETトランジスタ・デバイスの設計と製造方法が示される。MODFETの設計は、RF、マイクロ波、サブミリ波及びミリ波を含むさまざまな通信用途のための、超高速、低ノイズの性能を持った、成長型エピタキシャル電界効果トランジスタ構造を有する。エピタキシャル電界効果トランジスタ構造は、大幅に改善されたRF性能の達成を可能にする、極薄SOI又はSGOI基板上に最適な変調ドープ・ヘテロ構造を形成するシリコン及びシリコンゲルマニウム層を組込んだ高移動度ひずみn−チャネル及びp−チャネル・トランジスタのための、極限的な(垂直及び横方向の)デバイス小型化及び層構造設計を含む。

(もっと読む)

電界効果型半導体装置における容量素子の動的制御

電界効果型装置はキャパシタのプレートをそれぞれ形成する複数のセグメントを有する少なくとも1つのセグメント化されたフィールド・プレートを含んでおり、選択されたセグメントを動的に接続してゲート−ドレイン間容量及びドレイン−ソース間容量を選択的に設定する電子素子に電界効果型装置が接続されている。トランスデューサを送信モードスイッチング装置と、受信モードスイッチング装置との間でスイッチングするスイッチング装置に結合されたトランスデューサを超音波装置が含んでおり、このスイッチング装置は電界効果型装置を含んでいる。  (もっと読む)

(もっと読む)

縦型ナノトランジスタおよび該トランジスタの製造方法ならびにメモリ装置

本発明の課題は、機械的応力に対し良好な耐性をもち、その製造が公知の従来技術よりも煩雑でない縦型ナノトランジスタを提供することである。本発明によればこの課題は、以下の特徴を備えた縦型ナノトランジスタによって解決される。すなわちソースコンタクトと、ドレインコンタクトと、ゲート領域と、ソースコンタクトとドレインコンタクトの間に配置され半導体特性をもつ円筒状のチャネル領域が設けられており、この円筒状チャネル領域は絶縁性フレキシブル基板に埋め込まれており、この領域は、ゲート領域とチャネル領域上部が同軸構造を成すよう、フレキシブル基板上およびチャネル領域上部の金属層により形成されたゲート領域により取り囲まれている。さらにソースコンタクトと半導体特性をもつチャネル領域とドレインコンタクトは縦方向に配置されていて、ソースコンタクトとドレインコンタクトと半導体特性をもつチャネル領域に対向するゲート領域と、基板の上側および下側は電気的に絶縁性の部材を有している。メモリ装置は多数のこの種の縦型ナノトランジスタから成る。本発明はこの種のトランジスタの製造方法にも関する。  (もっと読む)

(もっと読む)

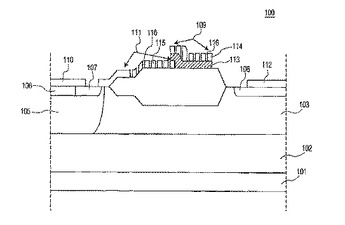

薄膜トランジスタの製造方法

【課題】 薄膜トランジスタの製造方法に関し、LDD領域の抵抗を許容レベルにまで下げるとともにTFTしきい値電圧のシフトを防ぐことを目的とする。

【解決手段】 絶縁性基板上に多結晶Siを形成する工程と、該多結晶Si上にゲート絶縁膜を形成する工程と、該ゲート絶縁膜上に下層ゲート電極と該下層ゲート電極より幅の狭い上層ゲート電極から成る2層ゲート電極を形成する工程と、該2層ゲート電極をマスクにして3属あるいは5属元素から成る不純物をイオン注入する工程と、熱処理する工程と、該2層ゲート電極をマスクにして水素をイオン注入する工程を含むように構成する。

(もっと読む)

401 - 404 / 404

[ Back to top ]