Fターム[5F110FF28]の内容

Fターム[5F110FF28]に分類される特許

3,041 - 3,049 / 3,049

複合酸化物を含むチャネルを有する半導体デバイス

例示的な実施形態には半導体デバイスが含まれる。当該半導体デバイスは、亜鉛−ゲルマニウム、亜鉛−鉛、カドミウム−ゲルマニウム、カドミウム−スズ、カドミウム−鉛を含む金属酸化物のうちの1つ又は複数を含むチャネルを具備し得る。 (もっと読む)

有機半導体材料、有機トランジスタ、電界効果トランジスタ、スイッチング素子及びチアゾール化合物

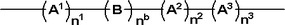

下記一般式で表される部分構造を持つ化合物を含有することを特徴とする有機半導体材料、それを用いた有機トランジスタ及び電界効果トランジスタ、及び該有機トランジスタまたは該電界効果トランジスタを用いるスイッチング素子。

(式中、Bはチアゾール環をもつユニットを表し、A1,A2はそれぞれ独立にアルキルを置換基として持つユニットを表し、A3は二価の連結基を表し、nbは1〜20の整数を表し、n1、n2はそれぞれ独立に0〜20の整数を表し、n3は0〜10の整数を表す。)

(もっと読む)

有機薄膜トランジスタの製造方法及び該製造方法により作製される有機薄膜トランジスタとそのシート

熱可塑性半導体材料を含む層及び、該層に接合する金属微粒子を含む層を形成して、押圧後加熱するか押圧と加熱を同時に行い、半導体層、ソース電極、ドレイン電極とする有機薄膜トランジスタの製造方法、および、支持体シート上に、ゲートバスライン及びソースバスラインを介して連結された複数の有機薄膜トランジスタが形成され、該薄膜トランジスタのソース電極及びドレイン電極が、当該電極を構成する金属相の少なくとも1部が熱可塑性半導体材料を含む半導体層に混入して、該半導体層に接合することを特徴とする有機薄膜トランジスタシート。 (もっと読む)

乱数生成素子

【課題】 増幅回路を用いなくても1Mbit/s以上の乱数生成レートが可能となるような物理現象中のランダムノイズを利用した乱数生成素子を提供することを目的とする。

【解決手段】 半導体表面との間で非常に薄いトンネル絶縁膜を介して電子の充放電が可能な導電性微粒子をチャネル上に設け、チャネル幅Wを狭く、かつ導電性微粒子の面密度Ddotを多く、かつチャネル〜導電性微粒子間のトンネル抵抗を小さくする。例えば、膜厚0.8nmのシリコン窒化膜をトンネル絶縁膜とするバルク基盤上の素子の場合、チャネル幅W=0.1μm、平均粒径d=8nm程度のSi微結晶粒子群を1.7×1012cm−2程度の面密度で形成すると、1MHzのノイズ成分を0.1%にできる。

(もっと読む)

ナノワイヤ複合体およびこれらに由来する電子基板を作製するためのシステムおよび方法

本発明は、ナノワイヤ−材料複合体を生成するシステムおよび処理に関わる。ナノワイヤ(606)が少なくとも一つの表面の一部分(604)に取り付けられた基板が提供される。ナノワイヤ−材料複合体を生成するよう、当該部分上に材料が堆積される。処理は、独立したナノワイヤ−材料複合体を生成するよう基板からナノワイヤ−材料複合体を分離することを必要に応じて含む。独立したナノワイヤ−材料複合体は、必要に応じて、電子基板に更に処理される。様々な電子基板は本明細書記載の方法を用いて形成される。例えば、多色発光ダイオードは、それぞれの複合体層が異なる波長で光を発するナノワイヤ−材料複合体の多数の積層された層から形成され得る。  (もっと読む)

(もっと読む)

薄膜電子部品の製造方法および製造装置ならびに薄膜電子部品

本発明は、薄膜電子部品の製造方法およびこの方法を実施する装置に関する。また、本発明は、この方法に従って製造された薄膜電子部品に関する。まず、実質的に誘電性を有する基板上に、導電性材料から成るガルヴァニックに均一な最下段の導電層が形成され、この最下段の導電層から導電領域がガルヴァニックに相互に分離して、電極パターンが形成される。この電極パターン上には、薄膜部品に必要とされる上部の不活性層または活性層を1層または数層形成することが可能である。本発明によれば、この最下段の導電層が分離することによる電極パターンの形成は、ダイカットエンボス加工に基づく切断作業を最下段の導電層に行うことによる。すなわち、切断作業に使用する切断部材の浮彫りが、基板上に永久変形が生じさせ、同時に、導電層から、ガルヴァニックに相互に分離した導電領域に至る領域をエンボス加工する。本発明は、ロールツーロール方式における薄膜部品の製造に適している。

(もっと読む)

(もっと読む)

有機薄膜トランジスタ

【課題】特殊な技術を要せず、簡単な製造方法でキャリア移動度が高い有機薄膜トランジスタを提供すること。

【解決手段】有機半導体層に重量平均分子量2000以上のπ共役系ポリマー及び分子量2000以下のπ共役系オリゴマーを含有することを特徴とする有機薄膜トランジスタ。

(もっと読む)

発光装置およびその作製方法

【課題】アクティブマトリクス型の発光装置における光の取り出し効率を向上させる手段を提供する。

【解決手段】アクティブマトリクス型の発光装置において、第1の凹部101a〜第3の凹部101cを有する第1の基板100に金属膜102a〜第3の金属膜102cを形成することや、画素電極145、有機層148、凸部149aの表面を有する陰極149からなる発光素子150を形成することにより、光の損失や隣の画素への光漏れを防ぐことができる。

(もっと読む)

液晶表示装置およびその作製方法

【課題】 IPS方式の液晶表示装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現する。

【解決手段】 本発明では、チャネル・エッチ型のボトムゲートTFT構造を採用し、ソース領域119及びドレイン領域120のパターニングとソース配線121及び画素電極122のパターニングを同じフォトマスクで行うことを特徴とする。

(もっと読む)

3,041 - 3,049 / 3,049

[ Back to top ]