Fターム[5F110HM11]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 配置 (4,297)

Fターム[5F110HM11]の下位に属するFターム

Fターム[5F110HM11]に分類される特許

1 - 13 / 13

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

有機トランジスタ及びその製造方法

【課題】ソース、ドレイン電極と有機半導体層の間の接触抵抗を低減して、短チャネル化により高速応答性能を向上させ、かつ、短チャネル化に伴うソース、ドレイン電極とゲート電極間の短絡の発生を回避可能とする。

【解決手段】絶縁性の基板と、基板上に相互間に間隔を設けて配置され、各々台状平面を形成する一対の絶縁性の台座2、3と、一方の台座が形成する台状平面上に設けられたソース電極4と、他方の台座が形成する台状平面上に設けられたドレイン電極5と、一対の台座の間の基板上に設けられたゲート電極6と、ソース電極及びドレイン電極の上面に接触させて配置された有機半導体層7とを備える。ゲート電極と有機半導体層の下面とはギャップ領域8を介在させて上下方向に対向し、ギャップ領域に面する台座の側面は、上側端縁に対して下側端縁がゲート電極から遠ざかる側に後退した形状を有する。

(もっと読む)

半導体装置

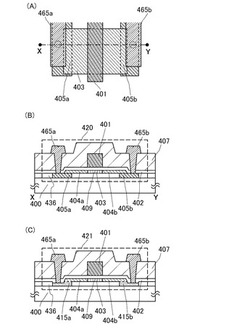

【課題】半導体装置において、少なくとも容量素子とトランジスタとを有する回路要素が占める面積を小さくする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを有する半導体装置において、第2のトランジスタよりも上方に第1のトランジスタ及び容量素子を配置する。そして、第1のトランジスタのソース又はドレインの一方と、容量素子の一方の電極とを兼ねる共通電極を設ける。さらに、容量素子の他方の電極を共通電極よりも上方に配置する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】下地絶縁膜上に形成される酸化物半導体膜と、当該酸化物半導体膜とゲート絶縁膜を介して重畳するゲート電極と、酸化物半導体膜に接し、ソース電極及びドレイン電極として機能する一対の電極とを備えるトランジスタであり、下地絶縁膜は、酸化物半導体膜と一部接する第1の酸化絶縁膜と、当該第1の酸化絶縁膜の周囲に設けられる第2の酸化絶縁膜とを有し、トランジスタのチャネル幅方向と交差する酸化物半導体膜の端部は、第2の酸化絶縁膜上に位置するものである。

(もっと読む)

半導体装置及びその作製方法、ならびに電子機器

【課題】リーク電流が低減された半導体装置を提供すること。また、高い電界効果移動度と低いリーク電流が両立された半導体装置を提供すること。また、低消費電力化された電子機器を提供すること。また、マスク枚数を増やすことなくリーク電流を低減可能な、半導体装置の作製方法を提供すること。

【解決手段】高いキャリア移動度を有する半導体膜からなる半導体層の側面が、ソース電極及びドレイン電極と接しない構造とすればよい。また、フォトマスク数を増やすことなく、このような構成を有するトランジスタ構造を形成し、電子機器に適用すればよい。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法及び発光装置

【課題】薄膜トランジスタのオン電流の安定を図ること。

【解決手段】ELパネル1の駆動トランジスタ6において、ソース電極6iとゲート電極6aおよびドレイン電極6hとゲート電極6aの間にバックゲート効果を発現させないように、ソース電極6iとドレイン電極6hをゲート電極6aから離間させることに十分な膜厚(例えば、2000Å以上4000Å以下の膜厚)を有する保護絶縁膜6dを形成することによって、駆動トランジスタ6のチャネルが乱されることを低減して、オン電流を安定させるようにした。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、および電子機器

【課題】基板やゲート絶縁膜の露出表面と、ソース電極およびドレイン電極の露出表面とに、良好で均一な膜質の半導体薄膜を設けることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ1aは、有機材料または酸化物材料またはシリコン系材料からなるゲート絶縁膜(絶縁層)15上に、導電性酸化物材料からなる酸化物材料層17-aとこの上部の金属材料層17-bとからなるソース電極およびドレイン電極が設けられたものである。そしてゲート絶縁膜(絶縁層)15とソース電極17sおよびドレイン電極17dとにおける酸化物材料層17-aとの露出面が、自己組織化膜19で覆われており、この自己組織化膜19で覆われた上部のソース電極17s−ドレイン電極17d間にわたって半導体薄膜21が設けられている。

(もっと読む)

薄膜トランジスタ及びこれを用いた表示装置、並びに、薄膜トランジスタの製造方法

【課題】オフ電流を抑制するとともにオン電流を確保することができる薄膜トランジスタを提供する。

【解決手段】基板10と、基板の上方に形成されたゲート電極11及びゲート絶縁膜12と、ゲート絶縁膜を介して配置されたチャネル層13と、チャネル層に接続されたバッファ層14と、バッファ層に接続され、不純物が添加された第1コンタクト層15a(15b)と、第1コンタクト層に接続され、第1コンタクト層よりも不純物濃度が高い第2コンタクト層16a(16b)と、第2コンタクト層に接続されたソース電極17S及びドレイン電極17Dとを備える。ソース電極とドレイン電極との間におけるキャリアの移動経路は、チャネル層、バッファ層、第1コンタクト層及び第2コンタクト層を経由してキャリアが移動する第1経路と、チャネル層及び第2コンタクト層を経由してキャリアが移動する第2経路とを含む。

(もっと読む)

pチャネル型薄膜トランジスタ、pチャネル型薄膜トランジスタの製造方法および表示装置

【課題】より高い電子(又は正孔)の移動度を有するTFTを製造することができる薄膜トランジスタ、薄膜トランジスタの製造方法、表示装置を提供すること。

【解決手段】横方向に結晶成長された半導体薄膜4aにソース領域S、チャネル領域C、およびドレイン領域Dを有し、前記チャネル領域C上部にゲート絶縁膜11およびゲート電極12を有する薄膜トランジスタ1であって、前記ドレイン領域Dの前記チャネル領域C側のドレイン端10は前記結晶成長の終了位置8付近に位置するように形成する。

(もっと読む)

nチャネル型薄膜トランジスタ、nチャネル型薄膜トランジスタの製造方法および表示装置

【課題】より高い電子(又は正孔)の移動度を有するTFTを製造することができる薄膜トランジスタ、薄膜トランジスタの製造方法、表示装置を提供すること。

【解決手段】横方向に結晶成長された半導体薄膜4aにソース領域S、チャネル領域C、およびドレイン領域Dを有し、前記チャネル領域C上部にゲート絶縁膜11およびゲート電極12を有する薄膜トランジスタ1であって、前記ドレイン領域Dの前記チャネル領域C側のドレイン端10は前記結晶成長の終了位置8付近に位置するように形成する。

(もっと読む)

nチャネル型薄膜トランジスタ、nチャネル型薄膜トランジスタの製造方法および表示装置

【課題】より高い電子(又は正孔)の移動度を有するTFTを製造することができる薄膜トランジスタ、薄膜トランジスタの製造方法、表示装置を提供すること。

【解決手段】横方向に結晶成長された半導体薄膜4aにソース領域S、チャネル領域C、およびドレイン領域Dを有し、前記チャネル領域C上部にゲート絶縁膜11およびゲート電極12を有する薄膜トランジスタ1であって、前記ドレイン領域Dの前記チャネル領域C側のドレイン端10は前記結晶成長の終了位置8付近に位置するように形成する。

(もっと読む)

pチャネル型薄膜トランジスタ、pチャネル型薄膜トランジスタの製造方法および表示装置

【課題】より高い電子(又は正孔)の移動度を有するTFTを製造することができる薄膜トランジスタ、薄膜トランジスタの製造方法、表示装置を提供すること。

【解決手段】横方向に結晶成長された半導体薄膜4aにソース領域S、チャネル領域C、およびドレイン領域Dを有し、前記チャネル領域C上部にゲート絶縁膜11およびゲート電極12を有する薄膜トランジスタ1であって、前記ドレイン領域Dの前記チャネル領域C側のドレイン端10は前記結晶成長の終了位置8付近に位置するように形成する。

(もっと読む)

nチャネル型薄膜トランジスタ、nチャネル型薄膜トランジスタの製造方法および表示装置

【課題】より高い電子(又は正孔)の移動度を有するTFTを製造することができる薄膜トランジスタ、薄膜トランジスタの製造方法、表示装置を提供すること。

【解決手段】横方向に結晶成長された半導体薄膜4aにソース領域S、チャネル領域C、およびドレイン領域Dを有し、前記チャネル領域C上部にゲート絶縁膜11およびゲート電極12を有する薄膜トランジスタ1であって、前記ドレイン領域Dの前記チャネル領域C側のドレイン端10は前記結晶成長の終了位置8付近に位置するように形成する。

(もっと読む)

1 - 13 / 13

[ Back to top ]