Fターム[5F110NN42]の内容

Fターム[5F110NN42]に分類される特許

1 - 20 / 106

薄膜トランジスタ回路基板、及びその製造方法

【課題】厚いゲート絶縁層を有する薄膜トランジスタと、薄いゲート絶縁層を有する薄膜トランジスタとを備えた回路基板を提供する。

【解決手段】ポリシリコン半導体層の上下に、ボトムゲート型薄膜トランジスタのゲート絶縁層とトップゲート型薄膜トランジスタのゲート絶縁膜とを各々設け、トップゲート型薄膜トランジスタのゲート絶縁膜の厚さをボトムゲート型薄膜トランジスタのゲート絶縁層の厚さと異ならせる。

(もっと読む)

電界効果型トランジスタ、その製造方法及びスパッタリングターゲット

【課題】トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供すること。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】本発明は、低温かつ簡便で安価な製造工程により作製可能であり、トランジスタ特性に優れる、ダブルゲート構造を有する薄膜トランジスタおよびその製造方法を提供することを主目的とする。

【解決手段】本発明は、基板と、上記基板上に形成された第1ゲート電極と、上記第1ゲート電極を覆うように形成された第1ゲート絶縁層と、上記第1ゲート絶縁層上に形成され、低抵抗領域であるソースコンタクト領域およびドレインコンタクト領域ならびに高抵抗領域であるチャネル領域を有する酸化物半導体層と、上記ソースコンタクト領域に接して形成されたソース電極と、上記ドレインコンタクト領域に接して形成されたドレイン電極と、上記酸化物半導体層上に形成され、絶縁性有機材料を含む第2ゲート絶縁層と、上記第2ゲート絶縁層上に形成された第2ゲート電極とを有することを特徴とする薄膜トランジスタを提供する。

(もっと読む)

半導体装置

【課題】ブラックマトリックス層を設計値以上に拡張しなくても、位置合わせずれによる光漏れが生じることを抑制できる半導体装置を提供する。

【解決手段】ボトムゲート電極12aとトップゲート電極17aで半導体層14を挟むデュアルゲート型の薄膜トランジスタを有する半導体装置において、前記トップゲート電極は、第1のブラックマトリックス層によって形成され、前記半導体層は、前記トップゲート電極によって覆われている半導体装置である。

(もっと読む)

半導体装置

【課題】ブラックマトリックス層の幅を設計値以上に拡張しなくても、位置合わせずれによる光漏れが生じることを抑制する。

【解決手段】ボトムゲート電極12aと第1のブラックマトリックス層17aで第1の半導体層14を挟むシングルゲート型の薄膜トランジスタを有する半導体装置であって、前記第1の半導体層と前記第1のブラックマトリックス層は重畳している半導体装置である。

(もっと読む)

半導体装置の製造方法、及び電気光学装置の製造方法

【課題】信頼性の高いLDD構造のTFTを形成することが可能な半導体装置の製造方法、及び電気光学装置の製造方法を提供する。

【解決手段】第1領域155のPMOSTFTと、第2領域156のLDDを備えるNMOSTFTと、第3領域157のLDDを備えるNMOSTFTとを製造する製造方法は、厚みの異なる2種類の多階調レジスト211,212を形成し、多階調レジスト211,212をマスクとして不純物の注入とアッシングとを繰り返し、セルフアラインでLDDを形成する工程を有する。

(もっと読む)

アクティブマトリックス基板及びアクティブマトリックス基板の製造方法、液晶表示装置

【課題】画素電極の電圧が保持され、画質が悪化することがないアクティブマトリックス基板を提供する。

【解決手段】本発明のアクティブマトリクス基板は、基材110上で半導体層150と接触するように設けられ、互いに対向しチャネル領域を形成するソース電極120及びドレイン電極130と、前記チャネル領域を制御するゲート電極140と、前記ドレイン電極130と接続され液晶材料を駆動する画素電極190と、を複数有するアクティブマトリクス基板において、複数の前記画素電極190の間の空間に配された無機絶縁膜195と、前記画素電極190とは接触せずに、前記無機絶縁膜195と接触するようにして配された遮光膜200と、を有することを特徴とする。

(もっと読む)

表示装置、液晶表示装置及びプロジェクター

【課題】高開口率な半導体装置を提供する。

【解決手段】絶縁表面上に第1配線と、第1配線上に第1絶縁膜と、第1絶縁膜上に半導体膜と、半導体膜上に第2絶縁膜と、第2絶縁膜上に第2配線と、第1配線と接続するゲート電極と、第2配線及びゲート電極上に第3絶縁膜と、第3絶縁膜上に半導体膜と接続する第3の配線とを有する半導体装置。

(もっと読む)

液晶表示装置

【課題】動作性能および信頼性の高い液晶表示装置を提供する。

【解決手段】第1のチャネル形成領域713と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域714と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜664と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線668と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線672と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

薄膜トランジスタ、アクティブマトリクス基板、およびそれらの製造方法

【課題】高い表示品質を実現することができるTFT、アクティブマトリクス基板及びそれらの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、ゲート電極2aと、ゲート電極2aを覆うように設けられたゲート絶縁膜3と、ゲート絶縁膜3の上に設けられ、ゲート電極の上方に配置された半導体膜5と、半導体膜5の上に設けられ、半導体膜5と電気的に接続されたソース電極7と、半導体膜5の上に設けられ、半導体膜5と電気的に接続されたドレイン電極9と、ソース電極7又はドレイン電極9の少なくとも一方とゲート絶縁膜3との間に設けられ、半導体膜5と分離して配置された低反射膜6と、を備え、低反射膜6が、平面視におけるゲート電極2aの外側において、ソース電極7、ドレイン電極9のパターンと略同一形状、又は、はみ出しているものである。

(もっと読む)

薄膜トランジスターの製造方法、及び電気光学装置

【課題】所期の特性が得られ高品位な表示を得ることができる薄膜トランジスターの製造方法、及び電気光学装置を提供する。

【解決手段】薄膜トランジスターとしてのTFT素子の製造方法は、第1基板12上に半導体膜38を形成する工程と、半導体膜38上にゲート絶縁膜53を形成する工程と、ゲート絶縁膜53上にゲート電極35aを形成する工程と、ゲート絶縁膜53及びゲート電極35aを覆って、半導体膜38に注入する不純物72の量を調整するための、ゲート絶縁膜53とエッチングの選択比が異なる調整膜73を形成する工程と、調整膜73を介して半導体膜38に不純物72を注入する工程と、半導体膜38にアニール処理を施す工程と、を有する。

(もっと読む)

電気光学装置、電気光学装置の製造方法、電子機器

【課題】入射光が確実に遮光され安定した動作が得られるトランジスターを備えた電気光学装置、電気光学装置の製造方法、この電気光学装置を備えた電子機器を提供すること。

【解決手段】電気光学装置は、ソース領域30sと、ドレイン領域30dと、チャネル領域30cと、チャネル領域30cとドレイン領域30dの間に形成された接合領域30fとを有する半導体層30aと、半導体層30aを覆う第1絶縁膜を介してチャネル領域30cに対向するゲート電極部30gと、平面的に接合領域30fに沿って第1絶縁膜および第2絶縁膜に設けられた溝としてのコンタクトホールCNT5,CNT6と、コンタクトホールCNT5,CNT6内に、ゲート電極部30gから延在して設けられる第1導電膜と、データ線6aを構成する第2導電膜とを含む少なくとも2層の導電膜を有する遮光性の側壁部と、を備えた。

(もっと読む)

トランジスタ、発光装置、及び、電子機器

【課題】トランジスタ外部からの光による悪影響を軽減又は防止したトランジスタ、発光装置、及び、電子機器を提供する。

【解決手段】トランジスタTrは、ゲート電極12と、透光性を有する絶縁層を介してゲート電極12と対向配置される、ゲート電極12側の面に光の反射面を有する導電体層22と、ゲート電極12と導電体層22との間に位置し、チャネルが形成される半導体層14と、を備える。光を吸収する光吸収層21は、導電体層22と半導体層14との間、並びにゲート電極12と半導体層14との間の少なくともいずれか一方に位置する。

(もっと読む)

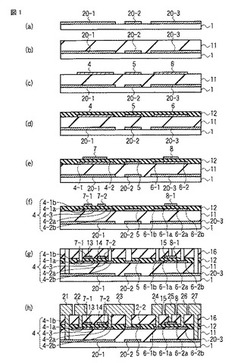

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変動しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、スイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜(6e、5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変化しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、スイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜(6e、5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変動しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、基板10と第1絶縁膜11の間に駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、第2絶縁膜12とパッシベーション膜14の間にスイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜6e(5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変動しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、スイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜(6e、5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変化しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、スイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜(6e5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

表示装置及びプロジェクター

【課題】液晶の配向不良を抑制するために画素電極を平坦化し、開口率を下げずに十分な容量を得られる容量素子を有する半導体装置を実現することを課題とする。

【解決手段】薄膜トランジスタ上の遮光膜、前記遮光膜上の容量絶縁膜、前記容量絶縁膜上に導電層、前記導電層と電気的に接続するように画素電極を有する半導体装置であり、前記遮光膜、前記容量絶縁膜および前記導電層から保持容量素子を形成することにより、容量素子として機能する領域の面積を増やすことができる。

(もっと読む)

1 - 20 / 106

[ Back to top ]