Fターム[5F140AA30]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 大電流化 (642) | 低オン抵抗化 (457)

Fターム[5F140AA30]に分類される特許

441 - 457 / 457

半導体装置及びその製造方法

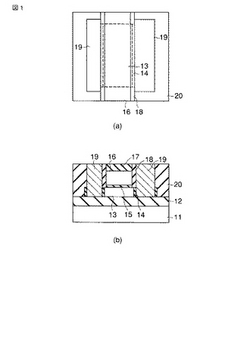

【課題】フェルミ・レベル・ピンニング効果を抑制するとともに、トランジスタの微細化を図ること。

【解決手段】シリコン基板または支持基板11上に形成された島状のチャネル層13と、チャネル層13上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、チャネル層13の一方向に対向する両側面上に形成されたシリコン窒化膜14と、シリコン窒化膜14の側面上に形成された金属材料からなるソース電極及びドレイン電極19とを具備する。

(もっと読む)

陥没トレンチを用いた表面側ドレインを有する半導体電力素子

本発明による半導体電力素子は、第1導電型を有する基板と、該第1導電型を有し且つ該基板の表面を覆ってこれと接触するエピタキシャル層とを含む。第1トレンチが該エピタキシャル層の内部に伸張してそこで終端する。陥没トレンチが該エピタキシャル層の表面から伸張し該エピタキシャル層を通って該基板の内部で終端する。該陥没トレンチは、該第1トレンチの横に間隔をおいて設けられ、該第1トレンチよりも広く且つ深く伸張する。該陥没トレンチは自身の側壁に沿ってのみ絶縁体によって裏打ちされることで、該陥没トレンチを充填する導電材料が該基板との電気的接続を該陥没トレンチの底部に沿ってなすと共に、相互接続層との電気的接触を該陥没トレンチの表面側に沿ってなす。  (もっと読む)

(もっと読む)

トレンチ構造を利用した横型半導体装置及びその製造方法

【課題】 長さ方向がゲート長方向と平行なトレンチに形成されたゲート電極を有し、単位平面積当たり大きなゲート幅を有する高駆動能力横型のMOSトランジスタの駆動能力を、平面的な素子面積を増加させずに向上させる半導体装置を提供する。

【解決手段】 半導体基板の表面に長さ方向がゲート長方向と平行なトレンチが形成された第1トレンチ領域013と、前記第1トレンチ領域の凹部底面と同一平面に設けられた第2トレンチ領域014および第3トレンチ領域015と、前記第1,第2,第3トレンチ領域の少なくとも1領域に形成された第2導電型のウェル領域と、前記第1トレンチ領域に設けられたゲート絶縁膜とゲート電極と、前記第1,第2と3トレンチ領域に前記ウェル領域より浅く設けられた第1導電型のソース領域とドレイン領域を有する半導体装置。

(もっと読む)

半導体装置

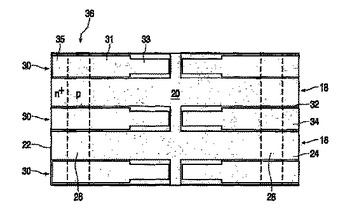

【課題】高耐圧化と低オン抵抗化を図ることができる半導体装置を提供する。

【解決手段】半導体基板1上に形成されたpウエル領域であるP−well35と、このP−well35の表面層に形成されるpオフセット領域であるP−off5と、P−off5の表面からP−well35に達するように形成したトレンチ19と、このトレンチ19の側壁にゲート酸化膜20を介して形成したゲート電極21と、トレンチ底に形成した拡張ドレイン領域である拡張ドレイン領域であるN−body6と、このN−body6と接するようにトレンチ19内部上方に向かって形成されたドレイン領域となるnエピタキシャル層30と、Pwell35の表面層に形成したソース領域となる上部のn+ 領域8とで構成する。この構成では、タングステン層23を形成する箇所にドレイン領域となるnエピタキシャル層30を形成するために、トレンチ19を広げることなく、ゲート電極21とドレイン領域となるnエピタキシャル層30の間隔を広げることができるために、高耐圧化と、低オン抵抗化を図ることができる。

(もっと読む)

横型短チャネルDMOS

【課題】 ゲート抵抗およびオン抵抗が低く、高速スイッチング特性および電流駆動特性に優れた横型短チャネルDMOSを提供する。

【解決手段】 P型半導体基体106の表面近傍にはN−型エピタキシャル層110が形成され、その表面近傍にはP型ウェル114およびN+型ソース領域116が形成されている。N−型エピタキシャル層110の表面近傍には、オン抵抗低減用N型ウェル134が形成され、その表面近傍にはN+型ドレイン領域118が形成されている。P型半導体基体106とN−型エピタキシャル層110との境界の、上面から見て少なくともP型ウェル114と重なり合う部分にはN型埋め込み層108が形成されている。また、このN型埋め込み層108の少なくとも一部とN−型エピタキシャル層110とが接するように、N型埋め込み層108の上面を覆うようにP型埋め込み層109が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 製造工程を簡略化することができ、低抵抗のソース、ドレインを具備した高性能かつ高信頼性の薄膜トランジスタを有する半導体装置、その製造方法、薄膜トランジスタアレイ基板及び液晶表示装置を提供する。

【解決手段】 導電型が異なる薄膜トランジスタを含んで構成される半導体装置であって、上記薄膜トランジスタは、基板上に半導体層を形成し、この半導体層上にゲート絶縁膜を介してゲート電極を形成し、ゲート電極をマスクにして半導体層に低濃度の不純物を注入して導電型が異なる低濃度不純物領域をそれぞれ形成し、ゲート電極の側面にサイドウォールスペーサーを形成した後に、ソース、ドレイン領域のみに高濃度不純物層としてSiGeを選択的に形成し、一方の導電型の低濃度不純物領域上のSiGeにのみ高濃度不純物層中の不純物とは異なる他の不純物をドーピングし、低濃度不純物領域上に同じ導電型の高濃度不純物領域を形成したものである半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】電力用のような高耐圧用途に使用できるボディ部分のプロファイルのばらつきの少ないDMOSを提供することを課題とする。

【解決手段】半導体基板の主表面に形成された第一導電型のウェルの所定の領域に形成された第二導電型のDMOSのボディ部分と、半導体基板上に形成されたゲート誘電膜と、ゲート誘電膜上にボディ部分の端部を跨ぐように形成されたゲート電極と、ゲート電極の両側の半導体基板の主表面に形成された第一の導電型の拡散層(但し、拡散層の少なくとも一方がボディ部内に形成されている)と、ボディ部分内に形成されたボディ部分より高い不純物濃度の第二導電型のコンタクト層とを含み、ボディ部分は、深さ方向のボディ部分とウェルとの濃度差が、半導体基板表面におけるボディ部分とウェルとの濃度差より大きい領域を備えていることを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】熱負荷をより小さく抑えて下地への影響なく成膜可能であると共に、十分に引っ張り応力を維持可能でかつパーティクルの発生を抑えた膜質良好な窒化シリコン膜によってMOSトランジスタを覆うことにより、トランジスタ特性の向上を図ることが可能な半導体装置およびこの半導体装置の製造方法を提供する。

【解決手段】半導体基板1の表面側に形成されたMOSトランジスタ11を覆う状態で窒化シリコン膜13が設けられた半導体装置において、窒化シリコン膜13は、両側の界面層における窒素濃度が中央部分の窒素濃度よりも高いことを特徴としている。窒化シリコン膜の界面層における窒素濃度は、化学量論的組成よりも高いことが好ましい。

(もっと読む)

埋設導電層を備えた高電圧トランジスタ

【課題】埋設導通層を備えた低オン抵抗値の横方向高電圧電界効果トランジスタ(HVFET)を提供する。

【解決手段】P型基板に形成されたN型ウエル内にP型埋設層領域を設け、これをN型ウエル領域に形成された第1のP型ドレイン拡散領域によってドレイン電極に接続すると共に、PMOSゲート領域の一端で表面から下方に延びる第2のP型ドレイン拡散領域にも接続し、ソース電極に接続されるP型ソース拡散領域でゲート領域の他端を定める。

(もっと読む)

横型トレンチMOSFET

【課題】 素子面積を増大させずにオン抵抗の低減を実現した横型MOSFETにおいて、更にオン抵抗を低減させる。

【解決手段】 トレンチ構造を用いることで素子面積を増大させずにチャネル幅を増大させ、オン抵抗の低減を実現した横型トレンチMOSFETにおいて、トレンチ008の両端付近に多方向イオン注入によりソース層004およびドレイン層005を形成する。このような構成にすることでソース層004およびドレイン層005がトレンチ008より深く形成され、電子がチャネル全域に広がって流れ、実効的なL長も短くなることで更なるオン抵抗の低減化が実現できる。

(もっと読む)

半導体装置

【課題】 ゲート−ドレイン間の容量が小さく、尚且つ、オン抵抗の低いパワー半導体装置を提供する。

【解決手段】

半導体装置100は、N型の半導体層20と、半導体層20の表面に形成されたP型のソース30およびP型のドレイン40と、ソース30とドレイン40との間のチャネル領域上にゲート絶縁膜60を介して設けられたゲート電極70であって、チャネル領域のチャネル長方向の長さがLgであるゲート電極70と、チャネル領域にイオン注入して形成されたボディ領域80であって、深さがXj、ゲート絶縁膜60を介してゲート電極70と対向するイオン注入された部分のチャネル長方向の長さがLaであるボディ領域80とを備え、La≦Lg−Xjを満たすことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

炭化シリコン半導体基板を用いた二重拡散MOS構造の半導体装置。この半導体装置は、炭化シリコン半導体基板の表面に積層されて、炭化シリコン半導体基板と同じ第1導電型を有する炭化シリコン半導体エピタキシャル層と、この炭化シリコン半導体エピタキシャル層の表層部に第2導電型不純物をドーピングすることによって形成されて、その表面付近における第2導電型不純物濃度が相対的に薄く、深部における第2導電型不純物濃度が相対的に濃くされたプロファイルを有する不純物領域とを備えている。 (もっと読む)

エンハンスメント型III族窒化物デバイス

III族窒化物スイッチは、凹型のゲートコンタクトを含み、ノミナリーオフの、すなわち、エンハンスメント型のデバイスを提供する。凹型のゲートコンタクトを提供することにより、ゲート電極が不活性状態である場合には、2つのIII族窒化物材料の界面に形成された伝導チャンネルが遮断され、デバイス中の電流の流れを防止する。ゲート電極は、ショットキコンタクト又は絶縁金属コンタクトである可能性がある。2つのゲート電極が提供され、ノミナリーオフ特性の双方向スイッチを形成することが可能である。ゲート電極と共に形成された凹部は、傾斜した側壁を持つ可能性がある。デバイスの電流伝達電極に関連して、多くの形状にてゲート電極を形成することが可能である。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

LDMOSトランジスタを有する電子装置

本発明のLDMOSトランジスタは、段付きシールド構造及び/又は第1及び第2ドレイン延長領域を具備し、前記第1ドレイン延長領域は、前記第2ドレイン延長領域よりも高いドーパント濃度を有し、前記シールドによって被われている。

(もっと読む)

(もっと読む)

絶縁トレンチゲート電極を有する横型電界効果トランジスタ

縦方向、横方向に交互に配置されたソース領域(22)、ソースボディ領域(26)、ドリフト領域(20)、ドレインボディ領域(28)、およびドレイン領域(24)をそれぞれ有するセル(18)を、減表面電界を達成するための構造とともに有する、電界効果トランジスタである。実施形態における構造は、ソースまたはドレイン領域(22、24)近傍にゲート領域(31)を定義する縦方向に離間された絶縁ゲートトレンチ(35)と、ドリフト領域(20)近傍に縦方向に延在する電位プレート領域(33)と、を含むことができる。代替的に、別個の電位プレート領域(33)または縦方向に延在する半絶縁フィールドプレート(50)をドリフト領域(20)近傍に設けてもよい。このトランジスタは、双方向切り替えに適している。  (もっと読む)

(もっと読む)

トレンチMOS構造

半導体装置はセル(18)に隣接するトレンチ(42)を有する。このセルは、ソース・コンタクト領域及びドレイン・コンタクト領域(26、28)と、それとは逆の導電型の中央本体(40)とを含む。この装置は双方向性であり、比較的低いオン抵抗で電流をいずれの方向にも制御する。好ましい実施形態は、ソース・ドリフト領域及びドレイン・ドリフト領域(30、32)と共に働いてRESURF効果を生み出す電位プレート(60)を含む。  (もっと読む)

(もっと読む)

441 - 457 / 457

[ Back to top ]