Fターム[5F140AC10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | 電圧印加 (40) | DTMOS (11)

Fターム[5F140AC10]に分類される特許

1 - 11 / 11

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とボディ領域とを接続したトランジスタを有する半導体装置に関し、動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

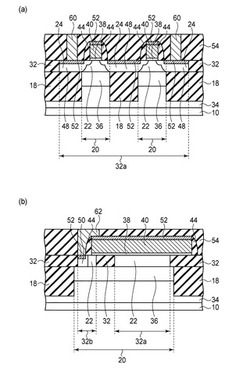

【解決手段】第1の素子分離絶縁膜と、第1の素子分離絶縁膜により画定され、第1の素子分離絶縁膜よりも浅いウェルと、ウェル内に形成され、ウェルよりも浅く、ウェルの第1の部分とウェルの第2の部分とを画定する第2の素子分離絶縁膜と、第1の部分上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、第2の部分においてウェルに電気的に接続され、ゲート電極とウェルとを電気的に接続する配線層とを有し、第2の素子分離絶縁膜下の領域のウェルの電気抵抗が、ウェルの他の領域の同じ深さにおける電気抵抗よりも低くなっている。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】新規なDTMOSトランジスタの製造方法を提供する。

【解決手段】半導体装置の製造方法は、第1領域と、第1領域に接続しこれより幅狭の第2領域と、第2領域に接続しこれより幅狭の第3領域とを含む半導体領域の画定工程、半導体領域に第1導電型不純物でウェル領域を形成する工程、ウェル領域上へのゲート絶縁膜形成工程、第3領域を幅方向に横断する第1部と、第1部から第1領域上に延びた第2部とを含むゲート電極を形成する工程、ゲート電極側面に、第2領域の一部を覆い他の一部を露出させるサイドウォールを形成する工程、第1領域及び第2領域の他の一部にゲート電極及びサイドウォールをマスクとし第2導電型不純物を注入する工程、熱処理による第2導電型不純物拡散工程、サイドウォールの一部を薬液で除去する工程、第1領域及び第2領域の他の一部へのシリサイド層形成工程を有する。

(もっと読む)

半導体装置、半導体集積回路装置、SRAM、Dt−MOSトランジスタの製造方法

【課題】Dt−MOSトランジスタよりなる半導体装置の素子寸法を縮小する。

【解決手段】シリコン基板21と、素子分離領域21Iと、前記素子分離領域により画成された、第1の導電型を有する第1のウェルよりなる素子領域21DNWと前記第1の導電型と逆の第2の導電型のコンタクト領域21P+1と、ゲート絶縁膜を介して、前記素子領域上から、前記素子分離領域のうち前記素子領域と前記コンタクト領域との間に延在するゲート電極と、第2の導電型のソース拡散領域と、第2の導電型のドレイン拡散領域と、前記ソース拡散領域の下端部に接して形成された第1の絶縁領域と、前記ドレイン拡散領域の下端部に接して形成された第2の絶縁領域と、前記ゲート電極と前記コンタクト領域とを電気的に接続するビアプラグと、を含み、前記第1のウェルは前記素子分離領域部分の下の前記シリコン基板を介して前記コンタクト領域に電気的に接続されていること。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

【課題】

電子デバイスにおける電力消費を低減するシステム及び方法が開示される。この構造及び方法は、大部分が、バルクCMOSのプロセスフロー及び製造技術を再利用することによって実現され得る。この構造及び方法は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することを可能にするとともに、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有し、それにより、電力制御の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

半導体装置

【課題】 従来の比例縮小側(係数α、α>1)を適用した平面型MOSTのしきい電圧のばらつきの標準偏差σ(VT)が、微細化とともに、すなわちαを大きくするとともに大きくなり、動作電圧が低くできないという問題がある。

【解決手段】 フィンの高さをチャンネル長よりも高くしたFinFET構造によって上記の問題を解決する。

(もっと読む)

半導体装置およびその駆動方法

【課題】集積回路内に多数形成され、論理回路などを構成するMOSFETから成る半導体素子1において、高機能化を図る。

【解決手段】ウェル2内にソース領域3とドレイン領域4とが形成され、かつそれらの領域間のチャネル領域5上に、ゲート絶縁膜6を介してゲート電極7が形成されるMOSFETにおいて、たとえばSOI基板を用い、かつフィールド酸化膜などによって各素子間を電気的に絶縁し、各素子毎にソース領域3およびドレイン領域4以外の領域で層間絶縁膜にコンタクト孔を形成し、チャネル領域5から基板端子TWを引出す。これによって、ゲート端子TGと該基板端子TWとの2つを入力とする2入力1出力の素子を実現することができ、論理回路などを構成するにあたって、集積度を向上し、高速化および低コスト化を図ることができる。

(もっと読む)

電界効果型トランジスタ及びその製造方法

【課題】 良好なボディコンタクトを得ることが可能でかつヘテロ接合層の電位を好適に制御可能なヘテロ接合MIS型電界効果型トランジスタを提供する。

【解決手段】 少なくともその上部が主にSiからなる半導体で構成された基板1と、基板1の直上に形成された主にSiからなるバッファ層である第1の半導体層3と、第1の半導体層3の上面にヘテロ接合するように形成されたヘテロ接合層4を少なくとも有する第2の半導体層4,5と、第2の半導体層4,5上に形成されたゲート絶縁膜9と、ゲート絶縁膜9上に形成されたゲート電極10と、少なくとも第2の半導体層4,5内に位置しかつ平面視においてゲート電極10を挟むように形成されたソース領域7及びドレイン領域8と、少なくとも第2の半導体層を貫通して第1の半導体層又は基板に達するように形成されたコンタクトホール31と、コンタクトホールの底面に露出する第1の半導体層及び基板の少なくともいずれかに接触するように形成された導電体からなるコンタクト12と、を備える。

(もっと読む)

MOSトランジスタ、MOSトランジスタの制御方法、およびトランスインピーダンスアンプ

【課題】低容量でオン抵抗が低いMOSトランジスタを実現する。

【解決手段】MOSトランジスタに、半導体基板に対して外部から任意の電位を印加するためのバックゲート端子を設け、MOSトランジスタの動作状態やそのときのドレイン電位やソース電位に応じた電位をバックゲート端子から半導体基板に対して任意の電位を印加する。

(もっと読む)

電界効果トランジスタ及びその製造方法、相補型電界効果トランジスタ

半導体基板の上に設けられた第1導電型の不純物を含むボディ領域を有する半導体層と、半導体層の上に設けられたゲート絶縁膜と、ゲート絶縁膜の上に設けられたゲート電極と、半導体層のうち、ゲート電極の側下方に位置する領域に設けられ、第2導電型の不純物を含むソース領域及びドレイン領域とを備え、ゲート電極とボディ領域とが電気的に短絡されている電界効果トランジスタであって、半導体層からソース領域及びドレイン領域を除いた領域のうち、ソース領域またはドレイン領域との接合部の少なくとも一部は、ボディ領域のうちソース領域及びドレイン領域との接合部を除く部分よりも高濃度で第1導電型の不純物を含んでいる。  (もっと読む)

(もっと読む)

半導体装置、その製造方法、および情報処理装置

【課題】ソース・ドレイン領域の占有面積が小さい半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1910は、素子分離領域101と活性領域102とを有する半導体基板100と、活性領域102上にゲート絶縁膜103を介して設けられ、側壁の少なくとも一部がゲート電極側壁絶縁膜105で覆われたゲート電極104と、ゲート電極104の両側にゲート電極側壁絶縁膜105を介してそれぞれ設けられたソース領域106およびドレイン領域106とを備えている。ソース領域106およびドレイン領域106の少なくとも一方は、コンタクト配線と接触するための第2の面を有し、第2の面は、第1の面AA’に対して傾いており、第2の面は、素子分離領域の表面と80度以下の角度で交差する。

(もっと読む)

1 - 11 / 11

[ Back to top ]