Fターム[5F140AC38]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 動作、用途、素子構造 (4,642) | CCD (7)

Fターム[5F140AC38]に分類される特許

1 - 7 / 7

半導体装置の製造方法

【課題】MOSトランジスタの特性のばらつきを低減するために有利な技術を提供する。

【解決手段】MOSトランジスタを含む半導体装置の製造方法は、半導体基板の上に形成された第1絶縁膜の上にゲート電極材料層を形成する工程と、前記ゲート電極材料層の上にエッチングマスクを形成する工程と、前記ゲート電極材料層をパターニングすることによりゲート電極を形成する工程と、前記ゲート電極が形成された前記半導体基板の上に第2絶縁膜を形成する工程とを含み、前記ゲート電極を形成する工程では、前記ゲート電極材料層がパターニングされるとともに、少なくとも、前記ゲート電極の側面の下部と、前記第1絶縁膜のうち前記側面に隣接する部分とを保護する保護膜が形成され、前記第2絶縁膜を形成する工程では、前記保護膜を覆うように前記第2絶縁膜が形成される。

(もっと読む)

絶縁ゲート型半導体素子及び絶縁ゲート型半導体集積回路

【課題】耐放射線性を有する絶縁ゲート型半導体素子、絶縁ゲート型半導体集積回路を提供する。

【解決手段】一部がチャネル領域をなすp型の半導体層11と、半導体層11の上部に活性領域21Bを定義する素子分離絶縁膜21と、チャネル領域にキャリア注入口を介してキャリアを注入するn型の第1主電極領域12と、チャネル領域から、キャリアを排出するキャリア排出口を有するn型の第2主電極領域13と、活性領域21Bの上に設けられたゲート絶縁膜22と、ゲート絶縁膜22の上に設けられ、第1主電極領域12と第2主電極領域13との間を流れるキャリアの流路に直交する主制御部、主制御部に交わる2本のガード部241,242を有してπ字型をなすゲート電極24と、第2主電極領域13のゲート幅方向の両端側に設けられたp型のリーク阻止領域61,62とを備える。

(もっと読む)

MOSトランジスタ、固体撮像装置、電子機器、及びそれらの製造方法

【課題】チャネル領域の特性向上及び、1/fノイズの改善を図ったMOSトランジスタを提供する。また、そのMOSトランジスタを用いた固体撮像装置を提供する。

【解決手段】ゲート電極31と、ゲート電極31に対して、チャネル領域34が素子分離領域32により複数に分割されたソース・ドレイン領域33から構成されるMOSトランジスタとする。

(もっと読む)

固体撮像装置とその製造方法、並びに半導体装置とその製造方法

【課題】MOS固体撮像装置における画素のノイズを低減する。白点の発生、1/fノイズの低減を図る。さらに読出し特性の改善を図る。

【解決手段】MOS固体撮像装置における所要の画素トランジスタにおいて、ゲート電極に所要導電型のサイドウォールを形成する。読み出しトランジスタでは、例えばゲート電極63の光電変換素子43側を第1導電型領域63Pとし、フローティングディフージョン部46側を第2導電型領域63Nとして構成とする。好ましくは、ゲート電極63の光電変換素子43側に絶縁膜56を介して第1導電型の半導体材料部64Pを形成する。例えば増幅トランジスタでは、ゲート電極下に埋め込みチャネルを形成し、第1導電型または第2導電型の半導体材料部を形成する。リセットトランジスタでは、ゲート電極のフローティングディフージョン部と電気的に接続される領域側に、所要導電型の半導体材料部を形成する。

(もっと読む)

半導体素子、半導体素子の製造方法

【課題】製造プロセスにおけるゲート電極への帯電に起因するチャージアップを防ぐことが可能な半導体素子を提供する。

【解決手段】半導体基板内に形成されたn型の不純物からなるソース領域4と、半導体基板内に形成されたn型の不純物からなるドレイン領域5と、ソース領域4及びドレイン領域5間の半導体基板上にゲート絶縁膜3を介して形成されたゲート電極6とを含むMOSトランジスタを有する半導体素子であって、半導体基板内に形成されたn型の不純物領域7と、半導体基板内に形成されたp型の不純物領域10と、n型の不純物領域7及びp型の不純物領域11の各々とゲート電極6とを接続するために設けられた配線H1及びH2とを備える。

(もっと読む)

半導体素子

【課題】所定のマスクを介して形成した不純物領域と、所定のマスクとは別のマスクを介して形成した不純物領域との位置ずれを評価することが可能なTEGを有する半導体素子を提供する。

【解決手段】TEGに含まれる第1の素子は、pウェル層2内に第1のマスクを介して形成された特定方向に並ぶ同一形状のn−領域4,5と、n−領域4,5間のpウェル層2内にn−領域4,5のそれぞれと所定の間隔をあけて第2のマスクを介して形成されたn−領域6と、pウェル層2上にゲート絶縁膜3を介して形成された2つの電極であって、n−領域4上とn−領域6上とに跨って形成された電極10及びn−領域5上とn−領域6上とに跨って形成された電極11と、n−領域4内の電極10と重ならない位置に形成されたn+領域8と、n−領域5内の電極11と重ならない位置に形成されたn+領域9と、n−領域6内の電極10,11と重ならない位置に形成されたn+領域7とを備える。

(もっと読む)

半導体装置の製造方法

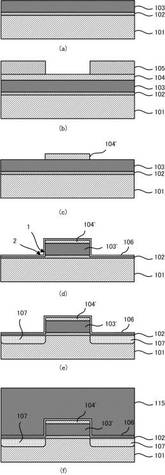

【課題】 酸化種の拡散による応力の発生を抑制してリーク電流の更なる低減を図る。

【解決手段】 半導体基板上に、隣接する素子を電気的に分離するための素子分離領域104としてトレンチ形状の埋め込み絶縁領域を形成した後、全面にシリコン酸化膜109を形成する。さらに、シリコン酸化膜109上にシリコン窒化膜110を形成し、そのシリコン窒化膜110全体を酸化することでシリコン酸化膜を得る。

(もっと読む)

1 - 7 / 7

[ Back to top ]