Fターム[5F140BB11]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル部の不純物プロファイル (687)

Fターム[5F140BB11]の下位に属するFターム

Fターム[5F140BB11]に分類される特許

1 - 11 / 11

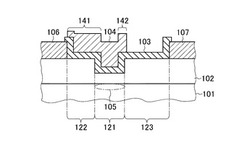

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、高いドレイン電流が実現できるようにする。

【解決手段】ドレイン電極107とゲート領域121との間のドレイン領域123の距離は、ソース電極106とゲート領域121との間のソース領域122の距離より長く形成され、加えて、ゲート電極104は、ゲート領域121からソース電極106の側に延在する延在部141を備えて形成されている。ゲート電極104のソース電極106の側への延在部141により、ゲート電極104に対する電圧印加でソース領域122のチャネル層101における電子濃度が増加可能とされている。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

半導体装置

【課題】間接遷移型の半導体を用いた場合でも、単一の電子の転送により単一の光子が生成できるようにする。

【解決手段】p型領域102とn型領域103とに挾まれた領域の半導体層101に導入された第1不純物原子106および第2不純物原子107からなる不純物原子対を備える。ここで、不純物原子対は、p型領域102とn型領域103とが対向して配置されている方向(第1方向)で、p型領域102とn型領域103とに挾まれた領域(チャネル領域)に配置される。また、第1不純物原子106および第2不純物原子107は、上記チャネル領域のゲート電極105の側の界面より30nmの範囲に導入されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子の特性や信頼性を向上させることが可能な半導体装置およびその製造方法を提供する。

【解決手段】Hfを含む高誘電率ゲート絶縁膜3上にゲート電極13、14を有する相補型電界効果型トランジスタにおいて、ゲート電極13、14の少なくともゲート絶縁膜3に接する部分は、Ni組成が40%を超えない結晶化したNiシリサイドを主成分とし、pチャネル上のゲート電極14に含まれるNiシリサイドとゲート絶縁膜3との界面にB、Al、Ga、In、Tlの中の少なくともひとつの元素を含み、且つ、nチャネル上のゲート電極13に含まれるNiシリサイドとゲート絶縁膜3との界面にN、P、As、Sb、Biの中の少なくともひとつの元素を含む半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル拡散層における不純物濃度プロファイルを急峻で且つ浅接合化することによって短チャネル効果を抑制すると共に、十分な活性化濃度を有する低抵抗なチャネル拡散層によって高駆動力を維持する微細デバイスを実現できるようにする。

【解決手段】MIS型トランジスタは、MIS型の半導体基板100の主面に形成されたゲート絶縁膜101と、該ゲート絶縁膜101の上に形成されたゲート電極102と、半導体基板100におけるゲート電極102の下方に形成されたP型のチャネル拡散層103とを有している。チャネル拡散層103は不純物として炭素を含んでいる。

(もっと読む)

ドーパントを阻止する超格子を有する半導体素子及び関連方法

半導体素子は、少なくとも1つの金属-酸化物電界効果型トランジスタ(MOSFET)を有して良い。前記少なくとも1つのMOSFETは、主部、該主部に隣接するチャネル層、及び前記主部と前記チャネル層との間に設けられたドーパントを阻止する超格子を有して良い。前記ドーパントを阻止する超格子は、複数の層からなる複数の積層群を含んで良い。前記ドーパントを阻止する超格子の層が構成する各群は、基本半導体部分を画定する複数の積層された基本半導体分子層、及び隣接する基本半導体部分の結晶格子内部に束縛された少なくとも1層の非半導体分子層を有して良い。  (もっと読む)

(もっと読む)

半導体装置

【課題】 従来のコンベンショナル型のドレイン構造を持つNMOSトランジスタを用いた静電保護回路では不可能であった動作電圧(トリガ−電圧)および保持電圧をが低く、かつ、自由に設定できる静電保護素子を容易に提供する。

【解決手段】 コンベンショナル型のドレイン構造を持つNMOSトランジスタのN型ソース・ドレイン拡散層の間に局所的にP型拡散層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 シリコン窒化膜のカーボンストッパーとしての機能を向上させることによって、良好なトランジスタ特性を確保し、製品歩留まりを向上させる半導体装置の製造方法を提供する。

【解決手段】 カーボンストッパー20となるシリコン窒化膜を7nm以下の膜厚に堆積し、NH3雰囲気下で1000℃の熱処理を行うことで、シリコン窒化膜20の密度を3.3g/cm3以上にする。7nm以下のシリコン窒化膜20でも良好なカーボンストッパーとしての機能を果たすので、STI12中のカーボン濃度を10E17atoms/cm3以下にし、安定したトランジスタ特性を得る。また、ゲート間隔を広げることにより、製品歩留りが向上する。

(もっと読む)

置換ゲート電界効果トランジスタ、及びその製造方法

【課題】

基板上に作製されるゲルマニウムまたはSiGeチャネルを有する、p−チャネルMISFETおよびn−チャネルMISFETの両方を提供する。

【解決手段】

傾斜SiGeチャネルまたはGeチャネルを有する、シリコン基板(502)上の自己整列MISFETトランジスタ(500H)。チャネル(526)は、ガスクラスタイオンビーム(524)照射を用いて形成され、従来のシリコンチャネルMISFETより高いチャネル移動度を提供する。上記トランジスタの製造方法は、ガスクラスタイオンビーム処理ステップで強化され、SiGeまたはGeチャネルを形成する置換ゲート工程に基づく。該チャネルは、補足ステップであるガスクラスタイオンビーム処理によって、あるいは、増移動度チャネルと同時にドープすることもできる。

(もっと読む)

半導体素子

【課題】 高い耐圧を有し且つ低いオン抵抗を有するノーマリオン型の半導体素子を提供する。

【解決手段】 ゲート電極9のドレイン層6側の端部と、チャネル領域7とドレイン層6との間の接合面との間は、距離x(x>0)がとられている。チャネル領域7は、ゲート電極9の直下の部分がチャネルとして機能し、右側の領域がドレイン層6の拡張領域として機能する。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル拡散層における不純物濃度プロファイルを急峻で且つ浅接合化することによって短チャネル効果を抑制すると共に、十分な活性化濃度を有する低抵抗なチャネル拡散層によって高駆動力を維持する微細デバイスを実現できるようにする。

【解決手段】 MIS型トランジスタは、MIS型の半導体基板100の主面に形成されたゲート絶縁膜101と、該ゲート絶縁膜101の上に形成されたゲート電極102と、半導体基板100におけるゲート電極102の下方に形成されたP型のチャネル拡散層103とを有している。チャネル拡散層103は不純物として炭素を含んでいる。

(もっと読む)

1 - 11 / 11

[ Back to top ]