Fターム[5F140BB12]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | チャネル構造 (2,673) | チャネル部の不純物プロファイル (687) | 平面分布 (80)

Fターム[5F140BB12]に分類される特許

1 - 20 / 80

半導体装置とその製造方法

【課題】 寄生ダイオードを介したリーク電流を抑えること。

【解決手段】 半導体装置1は、c面を表面とする窒化物半導体の半導体層13と、厚みが減少する厚み減少部14aを有する窒化物半導体のp型の埋込み層14と、を備える。埋込み層14では、厚み減少部14aの内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部14aの傾斜面の間のp型不純物の濃度が酸素濃度よりも高い部分が存在する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】比較的簡素な構成で電流コラプスの発生を抑制し、デバイス特性の劣化を抑えた信頼性の高い高耐圧のAlGaN/GaN・HEMTを実現する。

【解決手段】SiC基板1上に化合物半導体積層構造2を備えたAlGaN/GaN・HEMTにおいて、3層のキャップ層2eを用いることに加え、キャップ層2eのドレイン電極5の近傍(ゲート電極6とドレイン電極5との間で、ドレイン電極5の隣接箇所)に高濃度n型部位2eAを形成し、高濃度n型部位2eAでは、そのキャリア濃度が電子供給層2dのキャリア濃度よりも高く、そのエネルギー準位がフェルミエネルギーよりも低い。

(もっと読む)

横型の絶縁ゲート型バイポーラトランジスタを備えた半導体装置

【課題】オン電圧の低減と、破壊耐量確保、高速スイッチングを同時に実現できる横型IGBTを提供する。

【解決手段】エミッタ側にn型バリア層15を形成することで、ホールのバリアとして機能させ、コレクタ側から注入されたホールがエミッタ側のチャネルpウェル層6に流れ出てホール濃度が低下することを防止する。これにより、エミッタ近傍のn-型ドリフト層2内のキャリア濃度を上げることが可能となり、オン電圧の低減が可能となる。また、コレクタ側において、コレクタ電極12のうちp+型層4aと接触している部分をオーミック接触、p型層4bと接触している部分をショットキー接触とする。このショットキー接触とされた部分において、コレクタ側からのホールの注入が抑制され、蓄積キャリアを低減して、寄生バイポーラトランジスタがオンし難くなるようにできる。よって、低オン電圧を維持しながらスイッチング耐圧を確保することが可能となる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極とチャネル層との間の障壁層に低抵抗領域を備えた構成において、ゲートリーク電流を防止することによりドレイン電流の最大値の向上を図ることが可能な半導体装置を提供する。

【解決手段】化合物半導体で構成されたチャネル層14と、チャネル層14上に設けられた上部障壁層15とを備え、上部障壁層15における表面層には、不純物を含有することにより周囲よりも低抵抗に保たれた低抵抗領域15gが設けられている。また、この低抵抗領域15gを挟んだ位置において上部障壁層15に接続されたソース電極17sおよびドレイン電極17dを備えている。さらに、低抵抗領域15g上に設けられたゲート絶縁膜18と、このゲート絶縁膜18を介して低抵抗領域15g上に設けられたゲート電極19とを備えている。

(もっと読む)

半導体装置

【課題】耐圧の向上が図られる半導体装置を提供する。

【解決手段】n-型半導体領域には、ドレイン領域となるn-型の拡散領域が形成されている。n-型の拡散領域の周囲を取囲むようにp型の拡散領域が形成されている。p型の拡散領域には、ソース領域となるn+型の拡散領域が形成されている。n-型の拡散領域の直下には、p-型の埋め込み層13が形成されている。n-型の半導体領域の領域には、高電位が印加されるn+型の拡散領域が形成され、そのn+型の拡散領域の表面上には電極が形成されている。電極とドレイン電極とは、配線20によって電気的に接続されている。配線20の直下に位置する部分に、p-埋め込み層13に達するトレンチ3aが形成されて、ポリシリコン膜81が形成されている。

(もっと読む)

窒化物半導体装置および窒化物半導体装置の製造方法

【課題】オン抵抗が低く、かつ、Vth(閾値電圧)が高い窒化物半導体装置の提供。

【解決手段】アクセプタになるアクセプタ元素を含み、窒化物半導体で形成されたバックバリア層106と、バックバリア層106上に窒化物半導体で形成されたチャネル層108と、チャネル層108の上方に、チャネル層よりバンドギャップが大きい窒化物半導体で形成された電子供給層112と、チャネル層108と電気的に接続された第1主電極116、118と、チャネル層108の上方に形成された制御電極120と、を備え、バックバリア層106は、制御電極120の下側の領域の少なくとも一部に、アクセプタの濃度がバックバリア層の他の一部の領域より高い高アクセプタ領域126を有する窒化物半導体装置100。

(もっと読む)

半導体装置

【課題】回路面積の増大を抑制しつつ高耐圧の半導体装置を得る。

【解決手段】第1導電型の第1半導体層は、第1方向を長手方向として素子領域から延びて素子終端領域まで形成され、第1の不純物濃度を有し、MOSトランジスタのドレイン領域として機能する。また、第1導電型の第2半導体層は、第1方向を長手方向として素子領域から延びて素子終端領域まで形成され、第1の不純物濃度より小さい第2の不純物濃度を有し、第1半導体層と接続されるように配置されてMOSトランジスタのドリフト層として機能する。素子領域及び素子終端領域は、第1方向と直交する第2方向の幅が同一であり、第2方向に沿った断面に関し、素子終端領域における第2半導体層の幅は、素子領域における第2半導体層の幅よりも大きい。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】バッファ層の結晶成長時に高抵抗化の不純物をドーピングすることなく上層の化合物半導体の結晶品質を保持するも、バッファ層を高抵抗化してオフリーク電流を確実に抑制し、信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2の裏面から、化合物半導体積層構造2の少なくともバッファ層2aに不純物、例えばFe,C,B,Ti,Crのうちから選ばれた少なくとも1種類を導入し、バッファ層2aの抵抗値を高くする。

(もっと読む)

半導体装置の製造方法

【課題】基板に対して斜め方向からイオン注入を行う工程を含む半導体装置の製造方法においてゲート電極サイズの縮小化とリーク電流特性の改善を両立することができる製造方法を提供する。

【解決手段】

半導体基板の表面にゲート電極を形成する。ゲート電極のゲート長方向と交差するゲート幅方向における両端面を被覆するレジストマスクを形成する。半導体基板にゲート長方向成分およびゲート幅方向成分を有する注入方向で不純物イオンを注入して半導体基板の表面のゲート電極を挟む両側にゲート電極とオーバーラップした低濃度不純物層を形成する。ゲート電極の側面を覆うサイドウォールを形成する。ゲート電極およびサイドウォールをマスクとして不純物イオンを注入して半導体基板の表面のゲート電極を挟む両側にゲート電極から離間した高濃度不純物層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】寄生動作を抑制し破壊耐量を向上させた半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、半導体層と、第1導電形のソース領域と、第2導電形のバックゲート領域と、第1導電形のドレイン領域と、ゲート絶縁膜と、ゲート電極と、ソース電極と、ドレイン電極とを備えている。バックゲート領域のドレイン領域側の端が、ソース領域のドレイン領域側の端よりも、ドレイン領域側に位置する。

(もっと読む)

半導体装置および集積回路

【課題】ドレイン端での局所的な電流集中を防止して静電放電に対する耐性を向上させる。

【解決手段】N型高濃度埋め込み領域102の上面にN型低濃度領域103とN型ウエル領域104とN型高濃度埋め込みコンタクト領域105を順次隣接して配置し、N型低濃度領域103の上面にP型低濃度領域106を配置し、ドレイン電極113Dが接続される第1のN型高濃度領域107をN型高濃度埋め込みコンタクト領域105の上面に配置し、ソース電極113Sが接続される第2のN型高濃度領域108とP型高濃度領域109をP型低濃度領域106の上面にチャネル幅方向に並べて配置し、第1のN型高濃度領域107からN型ウエル領域104の上面を経由しP型低濃度領域106の上面に向けて素子分離領域110を配置し、P型低濃度領域106の上面に位置する箇所の上面にゲート酸化膜を介してゲート電極111を配置し、P型低濃度領域106のうちのゲート電極111の下部にチャネルが形成されるようにした。

(もっと読む)

半導体装置

【課題】半導体基板へのリーク電流が少ないMOS構造をダイオードとして用いる半導体装置を提供する。

【解決手段】電界効果トランジスタと、抵抗素子20と、を備える。前記抵抗素子は、前記電界効果トランジスタのバックゲート電極24と一方のソース・ドレイン領域16との接続点23と、前記電界効果トランジスタのゲート電極19との間に接続されている。そして、前記電界効果トランジスタの他方のソース・ドレイン領域15と前記ゲート電極19との間に電圧が印加される。

(もっと読む)

半導体装置

【課題】 工程の増加や占有面積の増加もなくオフリーク電流を小さく抑えた、十分なESD保護機能を持たせたシャロートレンチ分離構造を有するESD保護用のN型のMOSトランジスタを有する半導体装置を提供する。

【解決手段】 素子分離にシャロートレンチ分離領域501を有するESD保護用のN型MOSトランジスタにおいて、ESD保護用のN型MOSトランジスタのゲート電極301下面のゲート絶縁膜を介してP型シリコン基板表面に形成されたチャネル領域の表面に、ESD保護用のN型MOSトランジスタのドレイン領域202から一定の距離を隔てたオフセット領域601を介して、濃いP型の不純物濃度領域からなるP型ブレークダウン領域401を形成した半導体装置とした。

(もっと読む)

半導体装置

【課題】トランジスタ間の分離性が良好な半導体装置を提供する。

【解決手段】半導体装置において、第1導電型の半導体基板と、前記半導体基板の上層部分を複数の能動領域に区画する素子分離絶縁膜と、前記能動領域の上部に相互に離隔して形成された第2導電型のソース層及びドレイン層と、前記半導体基板上における前記ソース層と前記ドレイン層との間のチャネル領域の直上域に設けられたゲート電極と、前記半導体基板と前記ゲート電極との間に設けられたゲート絶縁膜と、第1導電型であり、実効的な不純物濃度が前記半導体基板の実効的な不純物濃度よりも高く、前記能動領域における前記ソース層及び前記ドレイン層の直下域に形成され、前記ゲート電極の直下域には形成されていないパンチスルーストッパ層と、を設ける。

(もっと読む)

半導体装置の製造方法

【課題】オン抵抗の低いパワーMOS等の半導体装置を提供する。

【解決手段】ゲート酸化膜を介しゲート電極22を形成するゲート電極形成工程と、ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する工程と、第1の開口部において露出している表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、ゲート電極間よりも狭い第2の開口部31を有する層間絶縁膜30を形成する層間絶縁膜形成工程と、第2の開口部よりも広い第3の開口部を有する第2のレジストパターン32を形成する工程と、第3の開口部33において露出している表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、を有し、第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする。

(もっと読む)

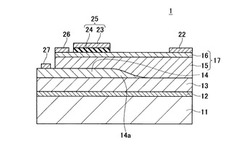

半導体装置及びその製造方法

【課題】トンネルFETの閾値ばらつきの抑制をはかる。

【解決手段】Si1-x Gex (0<x≦1)の第1の半導体層13上にゲート絶縁膜21を介して形成されたゲート電極22と、Geを主成分とする第2の半導体と金属との化合物で形成されたソース電極24と、第1の半導体と金属との化合物で形成されたドレイン電極25と、ソース電極24と第1の半導体層13との間に形成されたSi薄膜26とを具備した半導体装置であって、ゲート電極22に対しソース電極24のゲート側端部とドレイン電極25のゲート側端部とは非対称の位置関係にあり、ドレイン電極25のゲート側の端部の方がソース電極24のゲート側の端部よりも、ゲート電極22の端部からゲート外側方向に遠く離れている。

(もっと読む)

半導体装置およびその製造方法

【課題】素子面積の増大を抑制しつつ、ハンプ特性を改善できる半導体装置およびその製造方法を提供する。

【解決手段】一導電型半導体基板100の一主面101にSTI構造の素子分離領域30を形成し、素子分離領域30上の端部に凹部13、14を有するゲート電極10を形成し、ゲート電極10をマスクにして一導電型不純物を斜めにイオン注入して、凹部13、14を介して素子領域50の端部領域53、54に不純物注入領域71、72を形成し、ゲート電極10をマスクにしてソース、ドレイン領域81、82を形成する。

(もっと読む)

電子デバイス及びシステム、並びにその製造方法及び使用方法

幅広い電子デバイスのアレイ及びシステムにおける電力消費を低減する一式の新たな構造及び方法が提供される。これらの構造及び方法の一部は、大部分が、既存のバルクCMOSのプロセスフロー及び製造技術を再利用することで実現され、半導体産業及びより広いエレクトロニクス産業がコスト及びリスクを伴って代替技術へ切り替わることを回避可能にする。これらの構造及び方法の一部は、深空乏化チャネル(DDC)設計に関係し、CMOSベースのデバイスが従来のバルクCMOSと比較して低減されたσVTを有することと、チャネル領域にドーパントを有するFETの閾値電圧VTがより正確に設定されることとを可能にする。DDC設計はまた、従来のバルクCMOSトランジスタと比較して強いボディ効果を有することができ、それにより、DDCトランジスタにおける電力消費の有意義な動的制御が可能になる。  (もっと読む)

(もっと読む)

1 - 20 / 80

[ Back to top ]