Fターム[5F140BH26]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | 埋込ソース (33)

Fターム[5F140BH26]に分類される特許

1 - 20 / 33

半導体装置の製造方法

【課題】縦型トランジスタにおける上部拡散層の深さ方向のばらつきを低減することのできる半導体装置の製造方法を提供する。

【解決手段】本発明は表面が平坦なシリコン層からなる上部拡散層11を形成しようとするものであり、具体的には、ファセットを有するシリコン層を選択的に過剰成長させた後、層間絶縁膜7表面に形成されたシリコン層をCMPで擦り切ってシリコン層の表面を平坦化する。シリコン層の成長は、シリコン層を単結晶シリコンで選択的にエピタキシャル成長させる。この場合、ファセットが生じるので、最も成長が遅いファセットが層間絶縁膜表面より上方に位置するまで充分過剰に成長させる。

(もっと読む)

パルス列アニーリング方法および装置

【課題】基板の所望の領域上でアニーリングプロセスを実行するために使用される装置および方法を開示する。

【解決手段】1つの実施形態では、電磁エネルギのパルスはフラッシュランプまたはレーザ装置を使用して基板に送出される。パルスは約1nsecから約10msecの長さであってもよく、各パルスは基板材料を融解するのに必要なエネルギより少ないエネルギを有する。パルスの間隔は一般的に、各パルスにより与えられるエネルギを完全に放散させるのに十分な長である。このようにして、各パルスはマイクロアニーリング周期を終了する。パルスは1回で基板全体にまたは同時に基板の一部に送出されてもよい。

(もっと読む)

半導体装置および半導体装置の製造方法

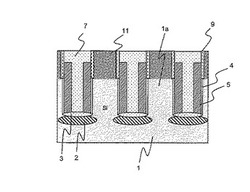

【課題】縦型トランジスタの特性を悪化させることなく縦型トランジスタの設置面積を削減できる高集積化に適した半導体装置およびその製造方法を提供する。

【解決手段】一定の間隔を空けて配置された複数のピラー30が備えられ、複数のピラー30が、縦型トランジスタTのチャネルとして機能する半導体層からなるチャネルピラー1と、不純物拡散層からなり、前記チャネルピラー1の下部に接続されて縦型トランジスタTの一方のソースドレインとして機能する下部拡散層4に電気的に接続された引き上げコンタクトプラグ2とを含む半導体装置とする。

(もっと読む)

双方向素子および半導体装置

【課題】高耐圧でオン電圧を低くできる双方向素子および半導体装置を提供すること。

【解決手段】分割半導体領域にpオフセット領域5とその表面に第1、第2nソース領域9、10を形成することで、第1、第2nソース領域9、10の平面距離を短縮してセルの高密度化を図り、トレンチに沿って耐圧を維持させることで高耐圧化を図り、ゲート電極7の電圧を第1、第2nソース電極11、12より高くすることで、トレンチ側壁にチャネルを形成して、双方向へ電流が流れる高耐圧で低オン電圧の双方向LMOSFETとすることができる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】高集積であり且つビット線を埋め込む必要のない3次元トランジスタを有する半導体記憶装置を提供する。

【解決手段】ゲートトレンチを介して両側に位置する第1及び第2の拡散層とゲートトレンチの底面に形成された第3の拡散層とを有する活性領域と、第1及び第2の拡散層にそれぞれ接続された第1及び第2の記憶素子と、第3の拡散層に接続されたビット線と、ゲート絶縁膜を介してゲートトレンチの第1の側面を覆い、第1の拡散層と第3の拡散層との間にチャネルを形成する第1のゲート電極と、ゲート絶縁膜を介してゲートトレンチの第2の側面を覆い、第2の拡散層と第3の拡散層との間にチャネルを形成する第2のゲート電極とを備える。本発明によれば、ゲートトレンチの両側面にそれぞれ別のトランジスタが形成されることから、従来の2倍の集積度が得られる。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラー型SGTを複数並列に接続する際に、配線層を設ける必要のない半導体装置を提供する。

【解決手段】3Dピラー型SGTの上部主電極領域が選択エピタキシャル成長半導体層を含み、少なくとも2つの隣接する3Dピラー型SGTを、各々の選択エピタキシャル成長半導体層を接触させて並列接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】シリサイド層が第1不純物拡散層まで拡がるのを抑制し、複数種類のトランジスタを自由に設計することが可能な半導体装置及びその製造方法を提供する。

【解決手段】少なくとも、基台部1Bの上に複数立設された柱状のピラー部1Cを含むシリコン基板1と、基台部1Bの側面1bを覆うように設けられるビット線6と、ピラー部1Cの側面を覆うゲート絶縁膜4と基台部1Bの上面1aにおいて、ピラー部1Cが設けられる位置以外の領域に設けられる第1不純物拡散層8と、ピラー部1Cの上面1dに形成される第2不純物拡散層14と、ビット線6とシリコン基板1との間に形成され、第1不純物拡散層8との間で高低差を有し、且つ、上端5aが、第1不純物拡散層8の上端8aよりも低い位置に配されてなる第3不純物拡散層5と、ピラー部1Cの側面1c側に設けられるワード線10の一部をなすゲート電極10Aと、が備えられる。

(もっと読む)

P型電界効果トランジスタ及びその製造方法

【解決手段】GaAsを用いることができる基板(1)の上方にn層(3)が配置され、前記n層上にp層(4)が配置される。前記p層は、ゲート電極(10)によって2つの別個の部分に分けられ、ソース及びドレインが形成されている。前記ゲート電極は、ゲート絶縁膜(6)によって半導体材料から絶縁されている。ソース/ドレインコンタクト(11)が、前記p層の前記2つの別個の部分に電気的に接続されている。 (もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート長が膜厚で規定された縦型の半導体装置であって、良好な信頼性のゲート絶縁膜を備え、微細化が容易な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置10の基板11上の、チャネル領域32に対応する領域を

除いた領域を種結晶領域として用い、チャネル領域32を迂回する形で、

基板11上に選択エピタキシャル成長又は固相エピタキシャル成長によってゲートとなる単結晶膜を結晶成長させる。この単結晶膜をCMPで窒化膜19の膜厚に規定し、この単結晶膜と絶縁膜からなる積層膜に、チャネルとなる任意の大きさの開口を形成する。この開口形成時にできた、単結晶膜の端面を酸化させることによりゲート酸化膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに容易な製造プロセスにより、微細で、高速且つ高性能なMIS電界効果トランジスタを提供する。

【解決手段】半導体基板1上に酸化膜2を介して、横方向エピタキシャル半導体層3が設けられ、素子分離領域形成用の埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。絶縁分離された横方向エピタキシャル半導体層3上に選択的に縦方向エピタキシャル半導体層7が設けられ、上部には高濃度ドレイン領域10及び低濃度ドレイン領域9が設けられ、下部には高濃度ソース領域8が設けられ、側面にはゲート酸化膜11を介してゲート電極12が設けられている。高濃度ドレイン領域10、高濃度ソース領域8及びゲート電極12には、それぞれバリアメタル18を有する導電プラグ19を介してバリアメタル21を有するCu配線22が接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】接触抵抗の増加が抑制されたピラー形状の縦型MOSトランジスタを用いた半導体装置を提供する

【解決手段】基部1aと複数のピラー部1Aとを有するシリコン基板1と、基部1aに設けられた一方のソースドレイン領域6と、ピラー部1Aの側面1bを覆うゲート絶縁膜4と、ゲート絶縁膜4を介してピラー部1Aの側面1bを覆うゲート電極5と、ピラー部1Aの上部に設けられた他方のソースドレイン領域12と、他方のソースドレイン領域12と接続されるコンタクトプラグ9とを備え、ピラー部1Aの上面1cの全面にコンタクトプラグ9が接続されていることを特徴とする半導体装置10。

(もっと読む)

半導体装置及びその製造方法

【課題】改良された縦型のMOSトランジスタを備える半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10の主面に対してほぼ垂直に延在するチャネル領域22と、チャネル領域22の下部に設けられた第1の拡散層領域22aと、チャネル領域の上部に設けられた第2の拡散層領域22bと、半導体基板10の主面に対してほぼ垂直に延在し、ゲート絶縁膜30を介してチャネル領域22の側面に設けられた第1のゲート電極34と、半導体基板10の主面とほぼ平行に延在し、第1のゲート電極34の上部に接続された第2のゲート電極35aと、第1の拡散層領域22aに接続され、第2のゲート電極と交差する埋め込み配線21を備えている。第2のゲート電極35aの平面的な位置は、第1のゲート電極34の平面的な位置に対してオフセットされている。

(もっと読む)

半導体素子及びその製造方法

【課題】チャネルが上下方向に形成されるトランジスタアレイ内における各トランジスタの駆動電圧の伝達効率を増大させるための半導体素子及びその製造方法を提供すること。

【解決手段】本発明の半導体素子は、複数の柱パターンと、各々の前記柱パターンを囲むゲート絶縁膜と、各々の前記ゲート絶縁膜を囲み、かつ、隣接する前記ゲート絶縁膜間を連接する導電膜とを備え、該導電膜は、ゲート電極及び配線として機能することを含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】異なるチャネル長のトランジスタを有し、設計の自由度が向上され、かつ、ゲート容量の増加を防止できる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】半導体基板1に、第一の導電型の活性領域41、42を形成し、チャネル用シリコン柱4b、4cを含む複数のシリコン柱4a〜4dを形成した後、第二の導電型の第一半導体領域7aを形成する工程と、容量増加防止用絶縁膜10を設けてゲート電位供給用シリコン柱4a、4dを形成する工程と、前記チャネル用シリコン柱4b、4cの周囲にゲート絶縁膜11を設ける工程と、ゲート電位供給用電極12bとゲート電極12aを形成し、接続する工程と、第一層間絶縁膜13を形成する工程と、前記チャネル用シリコン柱4bの高さを低くする工程と、第二の導電型の第二半導体領域7bを形成する工程と、を有する半導体装置100の製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置及びその製造方法

【課題】縦型絶縁ゲート型電界効果トランジスタのソースコンタクト抵抗を低減する。

【解決手段】半導体装置40では、半導体基板1の上部に、第1のソース層2aが設けられ、第1のソース層2a内に第1のソース層2aより深く、凹部3を有する第2のソース層2bが設けられる。凹部3上には、積層された第1の層間絶縁膜4a、ゲート電極膜5、及び第2の層間絶縁膜4bを貫通するようにゲート開口部が設けられる。側面にゲート絶縁膜6が設けられたゲート開口部には、第3のソース層2c、チャネル部7、及びドレイン層8が積層埋設される。第3のソース層2cは、下部が第2のソース層2bと接するように、凹部3上及びゲート開口部に埋設される。第1の層間絶縁膜4aと凹部3の間に突起状のゲート絶縁膜凸部6aが設けられる。

(もっと読む)

半導体装置

【課題】縦型MOSトランジスタが密集するアレイ部において、設計自由度の高いゲート電極への電位供給手段を有した半導体装置を提供する。

【解決手段】第1の導電型のゲート電極(2)を共有した複数の角柱縦型MOSトランジスタを有する半導体装置であって、角柱縦型MOSトランジスタが第1の角柱(3,4,5)の周りに形成されたゲート絶縁膜(18)を介して前記ゲート電極と対峙して成り、該ゲート電極への電位供給(6)を、前記第1の角柱と同時に形成され、かつ、ゲート電極の導電型と同じ第1の導電型であり、少なくとも一部分のゲート絶縁膜を除去した部分で前記ゲート電極に接している第2の柱(8)を介して行う。

(もっと読む)

半導体装置及びその製造方法

【課題】STI領域で囲まれた部分のシリコン基板をエッチングすることによりシリコン柱を形成して、シリコン柱をゲート絶縁膜およびゲート電極で覆いチャネル部とし、チャネル部の上下にソース・ドレインとなる拡散層を有した縦型MOSトランジスタにおいて、STI絶縁膜側壁に残ったゲート電極材による寄生MOS動作を解消する。

【解決手段】STI絶縁膜2の側壁に形成されるゲート電極材8に、該ゲート電極材の電位を制御する電極14を形成する。

(もっと読む)

窒化物半導体結晶成長基板、窒化物半導体素子および窒化物半導体結晶成長基板の製造方法

【課題】パワーデバイスの材料として適したIII族窒化物半導体結晶成長基板およびその製造方法、ならびに、そのIII族窒化物半導体結晶成長基板を用いて形成されるIII族窒化物半導体素子を提供すること。

【解決手段】この電界効果トランジスタは、積層界面がGaN膜2の主面2Aと斜めに交差するように、GaN膜2の主面2A側から順に積層された、N型GaN層6、P型GaN層7およびN型GaN層8を備える窒化物半導体積層構造部5を備えている。また、N型GaN層6、P型GaN層7およびN型GaN層8の各端面は、それぞれGaN膜2の主面2Aに平行な方向に沿って露出する露出面61、露出面71および露出面81となっている。

(もっと読む)

半導体装置

【課題】トレンチ構造を有する半導体装置において、トレンチの終端コーナー部への電界集中を防ぎ、それによってデバイスの耐圧低下を防止すること。

【解決手段】交差する複数のトレンチ63,64のうち、最外周のトレンチ64の幅はその内側のトレンチ63の幅よりも狭いこと、また、最外周のトレンチ64はその内側のトレンチ63よりも浅いこと、それによって、トレンチ終端コーナー部におけるゲート酸化膜やゲート電極の特異点をなくし、トレンチ終端コーナー部への電界集中を緩和するか、またはなくし、トレンチ終端コーナー部での耐圧低下を防止する。

(もっと読む)

半導体装置

【課題】半導体装置において半導体素子間の分離を好適に達成するとともに半導体装置の小型化を図ること。

【解決手段】半導体基板1と、半導体基板1上に形成されたエピタキシャル層2と、半導体基板1とエピタキシャル層2との間に形成された埋め込み層3と、エピタキシャル層2表面から埋め込み層3に達する第1のトレンチ7と、第1のトレンチ7内に埋め込まれるとともに埋め込み層3と接続されたドレイン取出電極8bと、ドレイン取出電極8bを電極とした半導体素子と、エピタキシャル層2表面からその半導体素子を囲むように設けられた第2のトレンチ5とを備え、第2のトレンチ5内の少なくとも側壁を絶縁膜6aで被覆した。

(もっと読む)

1 - 20 / 33

[ Back to top ]