Fターム[5F140BK40]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース・ドレイン領域、電極及びSD近傍領域の製造 (13,929) | その他 (14)

Fターム[5F140BK40]に分類される特許

1 - 14 / 14

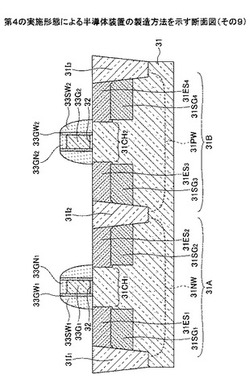

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

半導体集積回路装置の製造方法

【課題】低抵抗で、かつ接合リーク電流の少ないCoシリサイド層を形成することのできるサリサイドプロセスを提供する。

【解決手段】Co純度が99.99%以上で、FeおよびNiの含有量が10ppm以下、より好ましくはCo純度が99.999%の高純度Coターゲットを用いたスパッタリング法によってウエハの主面上に堆積したCo膜をシリサイド化することにより、MOSFETのゲート電極(8n、8p)、ソース、ドレイン(p+型半導体領域13、n+型半導体領域14)の表面に低抵抗で接合リーク電流の少ないCoSi2層(16b)を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ソース領域を燐注入によって高濃度不純物のソース領域を形成すると、ソース領域表面のみ増速酸化され、ウェル領域とソース領域表面との間に段差を生じるため、チャネル抵抗が増大する。

【解決手段】炭化珪素からなる絶縁ゲート半導体装置であって、少なくともウェル領域3、ソース領域4の表面に、等しい燐の濃度プロファイルを持つ犠牲層14を形成する。このようにすれば、ゲート絶縁膜を形成するときに、ウェル領域3とソース領域4の表面で増速酸化が均一に起こり、もってウェル領域3表面とソース領域4表面の間に段差が生じることが無い。

(もっと読む)

半導体素子、高電圧トランジスタ及び半導体素子の製造方法

【課題】高い降伏電圧を持つ半導体素子及びその製造方法を提供する。

【解決手段】半導体素子は、半導体基板100に形成された第1導電型ウェル領域に相互離隔して形成される第2導電型ドリフト領域、ドリフト領域310上に突起されるバーティカル領域320、及びバーティカル領域上に形成される第2導電型ソース/ドレイン領域600を含む。

(もっと読む)

半導体装置の製造方法

【課題】 MOSトランジスタの電気的特性を劣化させることなく、LDD構造を有するMOSトランジスタの実装が可能な半導体装置の製造方法を提供する。

【解決手段】 P型半導体基板1上に、ゲート酸化膜4及びゲート電極膜5を形成後、ゲート電極5aよりもパターン幅を拡げて形成された第1マスク手段6aをマスクとして、高濃度のN型不純物イオンを注入して高濃度不純物拡散領域7を形成する。その後、第1マスク手段6aに対してスリミング処理を施してパターン幅を狭めた第2マスク手段をマスクとして、低濃度のN型不純物イオンを注入して低濃度不純物拡散領域8を形成する。これによりLDD構造のソース・ドレイン領域を有するNMOSトランジスタが形成される。PMOSトランジスタについても同様に行って、CMOSトランジスタを形成する。

(もっと読む)

半導体装置の製造方法

【課題】 トレンチ溝の周囲にオフセットドレイン領域を有する横型高耐圧トレンチMOSFETを製造するため、トレンチ溝の周囲に最適な濃度の不純物を注入し、また幅の広いトレンチ溝内を酸化膜で埋めること。

【解決手段】 トレンチ溝2の周囲にオフセットドレイン領域3を形成するにあたり、トレンチ内面にドープドポリシリコン膜24を形成し、ドライブおこないトレンチ溝の側面および底面に拡散する。その後、ドープドポリシリコン膜24を熱酸化する。その後トレンチ溝内を酸化膜で埋めるにあたり、熱酸化によりトレンチ溝2内を酸化物4で埋めるか、熱酸化によりトレンチ溝内に酸化膜を生成して溝を狭めた後、残った溝を酸化物の堆積により埋める。あるいは、複数のトレンチ溝を形成し、それらの中を酸化物で埋めると共に、トレンチ間の基板部分を熱酸化して酸化膜に変える。

(もっと読む)

MOSトランジスタ、半導体装置及びその製造方法

【課題】 選択エピタキシャル成長技術を用いて基板上のソース及びドレインをせり上げた構造を有するMOSトランジスタにおいて、選択エピタキシャル成長によるシリコン層への不純物濃度を低く抑えたまま、バルクの抵抗を低減する。

【解決手段】 シリコン基板上に形成したサイドウォールを有するゲートと、シリコン基板上に選択エピタキシャル成長により形成したシリコン層とを備えるMOSトランジスタにおいて、シリコン層及びゲートを含む断面の少なくとも一部に、ゲートと反対の方向に下る傾斜部を形成する。

(もっと読む)

炭化ケイ素半導体装置の製造方法および炭化ケイ素半導体装置

【課題】オーミックコンタクト抵抗が低減できるようなオーミックコンタクト形成のためのアニール処理を施した、炭化ケイ素(000-1)面上に絶縁膜を有する半導体装置の製造方法および半導体装置を提供すること。

【解決手段】炭化ケイ素半導体の(000-1)面8上に、少なくとも酸素と水分を含むガス中で熱酸化し前記炭化ケイ素半導体の(000-1)面8上に接するように絶縁膜18を形成する工程と、絶縁膜18の一部を除去し開口部を形成する工程と、開口部の少なくとも一部にコンタクトメタル20を堆積する工程と、熱処理によりコンタクトメタル20と炭化ケイ素の反応層21を形成する工程とを有する炭化ケイ素半導体装置の製造方法において、前記熱処理を不活性ガスと水素の混合ガス中にて実施することを特徴とする炭化ケイ素半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】ソース・ドレイン領域にシリサイド層が設けられたトランジスタの接合リーク電流を抑制する。

【解決手段】シリコン基板101の素子形成面にゲート電極105を形成した後、シリコン基板101に絶縁膜を形成する。絶縁膜をエッチバックしてゲート電極105の側壁を覆うサイドウォール107を形成するとともに、サイドウォール107の側方のソース・ドレイン領域109が形成される領域において、シリコン基板101の素子形成面をエッチング除去し、素子形成面に略水平な掘り下げ面を形成する。その後、ゲート電極105の周囲のシリコン基板101に不純物をイオン注入し、ソース・ドレイン領域109を形成する。そして、ゲート電極105が設けられたシリコン基板101の素子形成面にNi膜を形成し、Ni膜とシリコン基板101とを反応させて、Niシリサイド層111を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】スイッチング損失を低減することができ、混載されたバイポーラトランジスタ回路などの特性変動を抑制する。

【解決手段】コレクタ領域をP型不純物層8b、ベース領域をN型不純物層2、エミッタ領域をP型不純物層3とP型拡散層8aとP型基板1とする横型絶縁ゲートバイポーラトランジスタ(IGBT)であって、前記N型不純物層2内に格子欠陥層12を形成し、このN型不純物層2内に形成された格子欠陥層12がライフタイムキラーの役割を果たす。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されたゲート電極をCo膜を用いてシリサイド化する場合であっても、ゲート電極の抵抗のばらつきを抑制しうる半導体装置及びその製造方法を提供する。

【解決手段】ゲート長Lgが50nm以下のゲート電極30上に、Co膜72を形成する工程と、熱処理を行うことにより、Co膜72とゲート電極30とを反応させ、ゲート電極30の上部にCoSi膜76aを形成する第1の熱処理工程と、Co膜72のうちの未反応の部分を選択的にエッチング除去する工程と、熱処理を行うことにより、CoSi膜76aとゲート電極30とを反応させ、ゲート電極30の上部にCoSi2膜42aを形成する第2の熱処理工程とを有し、第1の熱処理工程では、CoSi膜76aの幅wに対するCoSi膜76aの高さhの比h/wが0.7以下となるように、CoSi膜76aを形成する。

(もっと読む)

半導体素子、及び半導体素子の製造方法

【課題】 配線工程完了後においても簡便に電気的特性を調整することができる半導体素子を提供する。

【解決手段】 半導体基板上に形成される半導体素子であって、半導体基板と、半導体基板の一主面に形成される不純物拡散層と、不純物拡散層上に形成される絶縁膜と、絶縁膜上に形成され所定の熱処理により正電荷の量が変動して不純物拡散層の表面近傍の不純物濃度を制御するシリコン窒化膜と、を備えることを特徴とする半導体素子。

(もっと読む)

1 - 14 / 14

[ Back to top ]