Fターム[5F140CD06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | その他の領域、その他の素子構造及び製造 (630) | 内部ストレスの存在する領域 (31)

Fターム[5F140CD06]に分類される特許

1 - 20 / 31

半導体装置の製造方法

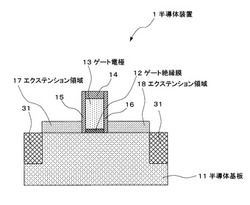

【課題】ヒ素(As)を高濃度にドーピングした状態でエクステンション領域のエピタキシャル成長膜表面に凹凸を発生させることなく、平滑な面に形成することを可能とする。

【解決手段】半導体基板11上にゲート絶縁膜12を介してゲート電極13を備え、前記ゲート電極13の両側の前記半導体基板11上に形成された不純物を含有してなるエクステンション領域17、18を備えた半導体装置1であって、前記エクステンション領域17、18は、シリコンゲルマニウムにヒ素を含む状態でエピタキシャル成長されたエピタキシャル成長膜からなり、このエピタキシャル成長膜は、ヒ素をドーピングしながらシリコンとゲルマニウムとを前記半導体基板11上に選択的にエピタキシャル成長させて形成される。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、シリコンエピタキシャル層に結晶欠陥が生じ易いという問題がある。

【解決手段】半導体装置1は、シリコン基板10、歪み付与層20、シリコン層30、FET40、および素子分離領域50を備えている。シリコン基板10上には、歪み付与層20が設けられている。歪み付与層20上には、シリコン層30が設けられている。歪み付与層20は、シリコン層30中のFET40のチャネル部に格子歪みを生じさせる。シリコン層30中には、FET40が設けられている。FET40は、ソース・ドレイン領域42、SD extension領域43、ゲート電極44およびサイドウォール46を含んでいる。ソース・ドレイン領域42と上述の歪み付与層20とは、互いに離間している。FET40の周囲には、素子分離領域50が設けられている。素子分離領域50は、シリコン層30を貫通して歪み付与層20まで達している。

(もっと読む)

半導体装置、電源装置、増幅器及び半導体装置の製造方法

【課題】半導体装置に形成される絶縁膜の付着力を高め歩留りを向上させる。

【解決手段】基板10の上方に形成された半導体層20〜23と、前記半導体層20〜23上に形成された絶縁膜31,32と、前記絶縁膜上31,32に形成された電極41と、を有し、前記絶縁膜31,32は、前記電極41の側における膜応力よりも、前記半導体層20〜23の側における膜応力が低いことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

ゲルマニウムベースの量子井戸デバイス

量子井戸トランジスタは、ゲルマニウムの量子井戸チャネル領域を有する。シリコンを含有したエッチング停止領域が、チャネル近くへのゲート誘電体の配置を容易にする。III−V族材料のバリア層がチャネルに歪みを付与する。チャネル領域の上及び下の傾斜シリコンゲルマニウム層によって性能が向上される。複数のゲート誘電体材料によって、high−k値のゲート誘電体の使用が可能になる。  (もっと読む)

(もっと読む)

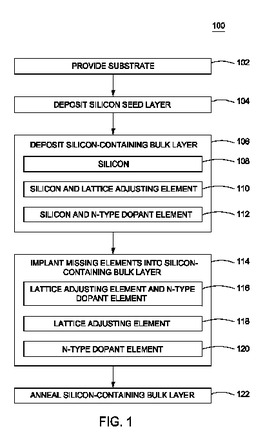

NMOSエピ層の形成方法

制御されたチャネル歪みおよび接合抵抗を有するNMOSトランジスタ、およびその製造方法が、本明細書で提供される。いくつかの実施形態において、NMOSトランジスタを形成するための方法は、(a)p型シリコン区域を有する基板を準備すること、(b)p型シリコン区域の上にシリコンシード層を堆積すること、(c)シリコン、シリコンおよび格子調整元素またはシリコンおよびn型ドーパントを備えるシリコン含有バルク層をシリコンシード層の上に堆積すること、(d)(c)で堆積されたシリコン含有バルク層に欠けている格子調整元素またはn型ドーパントのうちの少なくとも1つをシリコン含有バルク層の中に注入すること、(e)(d)の注入の後、シリコン含有バルク層をエネルギービームを用いてアニールすることを含むことができる。いくつかの実施形態において、基板は、その中に画定されたソース/ドレイン区域を有する、部分的に製造されたNMOSトランジスタデバイスを備えることができる。  (もっと読む)

(もっと読む)

半導体装置

【課題】MOSトランジスタを有する半導体装置であって、エリアパッド下のMOSトランジスタの特性変動を抑制することが可能な半導体装置を提供する。

【解決手段】MOSトランジスタとエリアパッドを有する半導体装置10であって、結晶方位面<110>を表面とするシリコンを材料とする半導体チップ11と、ソース領域、ゲート領域及びドレイン領域がシリコンの結晶方位<110>の方向に並び、半導体チップ11内に形成される複数のMOSトランジスタ12と、半導体チップ11上のエリアパッドとして2次元状に形成された複数の接合用電極パッド13と、複数の接合用電極パッド13それぞれの上に形成された接合用バンプ14とを備え、複数の接合用電極パッド13は、その中心点が結晶方位<110>の方向に対して斜めの方向に並ぶことを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板側への金属材料のリークを防止したフルシリサイドゲートの形成が可能で、これによりフルシリサイドゲートを備えながらも素子特性を維持することが可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1上にパターン形成されたゲート絶縁膜3と、ゲート絶縁膜3上にパターン形成されたゲート電極5a’とを備えた半導体装置40であって、ゲート電極5a’は、全層がシリサイド化されたものであり、ゲート絶縁膜3よりも狭い幅でゲート絶縁膜3の中央に設けられている。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】半導体基板1にSTI法で素子分離領域4を形成し、ゲート絶縁膜7を形成し、ゲート電極8a,8bを形成し、ソース・ドレイン用のn+型半導体領域9bおよびp+型半導体領域10bを形成し、半導体基板1上に金属膜12を形成し、金属膜12上にバリア膜13を形成する。それから、第1の熱処理を行って金属膜12とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させて金属シリサイド層を形成してから、バリア膜13および未反応の金属膜12を除去し、前記金属シリサイド層を残す。素子分離領域4は半導体基板1に圧縮応力を作用させる。バリア膜13は半導体基板1に引張応力を生じさせる膜であり、第1の熱処理では、金属膜12を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層が形成される。

(もっと読む)

半導体装置とその製造方法

【課題】

窒化物半導体を利用する半導体装置に関し、動作時に発生したホールを円滑に排出することが可能な技術を提供する。

【解決手段】

半導体装置1は、高転位密度領域18と低転位密度領域19を有する窒化物ガリウムのp型窒化ガリウム領域16を備えている。半導体装置2では、平面視したときに、低転位密度領域19が存在する範囲にスイッチング構造体が形成されている。半導体装置2はさらに、p型窒化ガリウム領域16に接するボディ電極20を備えている。ボディ電極20は、高転位密度領域18に接していることを特徴としている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート長に依存することなく均一な組成のFUSI構造を持つゲート電極を有するMISFETを得られるようにする。

【解決手段】第1のゲート電極114の両端部は、その他の部分よりも低く形成されており、当該両端部の側面及び上面を覆うように第1のサイドウォールスペーサ105Aが形成されている。第1のゲート電極114よりもゲート長が大きい第2のゲート電極115の両端部も、その他の部分よりも低く形成されており、当該両端部の側面及び上面を覆うように第2のサイドウォールスペーサ105Bが形成されている。

(もっと読む)

半導体装置とその製造方法

【課題】

表面荒れの抑制されたニッケルシリサイドを有する半導体装置、またはその製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン領域又はポリシリコン領域の上に、ニッケルプラチナ合金層を形成する工程と、プラチナが拡散しない温度で、ニッケルプラチナ合金層とシリコン領域又はポリシリコン領域とのシリサイド反応を生じさせ、ニッケルプラチナシリサイド層を形成する1次熱処理を行う工程と、薬液による面荒れを実質的に生じることなく、未反応ニッケルプラチナ合金層を薬液でウォッシュアウトする工程と、ニッケルプラチナシリサイド層をニッケルプラチナモノシリサイド層に変換する2次熱処理を行う工程と、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】十分大きな歪をシリコンの電界効果型トランジスタのチャネル部分に加えることによってトランジスタの特性を向上させる。

【解決手段】素子分離領域112に囲まれて形成された、チャネル層106、ソース・ドレイン形成領域107、ゲート絶縁膜113、ゲート電極115、サイドウォール116を有する電界効果型トランジスタのチャネル層106が、チャネル幅に沿った方向で下方に凸に湾曲している。この構造は、チャネル層106下の層をエッチング除去して空洞を形成しその空洞内にチャネル層を落とし込むことによって形成される。

(もっと読む)

半導体素子及びその製造方法

【課題】従来の方法を用いて作製したMOSFETよりも、十分大きな歪をMOSFETのチャネル部分に加えることによって、電子又はホール移動度を増加させトランジスタの特性を向上させたMOSFETを有する半導体装置及びその製造方法を提供する。

【解決手段】基板101上に形成されたp型のMOSFETを有する半導体装置において、チャネル層201とシリコン基板101との間に空洞200が形成されている。更に、ゲート電極105及びソース・ドレイン領域112等を含むシリコン基板の101の表面を覆うように、常態で圧縮応力を有するシリコン窒化膜107が形成されている。このような構成により、チャネル層201に圧縮歪が作用している。

(もっと読む)

半導体装置及びその製造方法

【課題】 ポケット領域を有するMOSトランジスタにおいて、ポケット不純物の濃度ゆらぎを低減し、MOSトランジスタの特性を改善する。またMOSトランジスタのチャネル領域に応力を加え、結晶格子を歪ませることによりMOSトランジスタの特性を向上させる。

【解決手段】 シリコン基板上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にアモルファスシリコン層を堆積する工程と、アモルファスシリコン層をMOSトランジスタのゲート電極形状に加工する工程と、ゲート電極形状に加工されたアモルファスシリコン層をマスクとしてシリコン基板表面に対して斜め方向からポケット不純物の注入を行なう工程とからなる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル層に歪みシリコンを用い、エクステンション領域にシリコンゲルマニウム層を用いることで、エクステンション領域の浅い接合を可能とする。

【解決手段】基板11上に形成されたもので該基板11側より徐々に応力が緩和されている応力緩和シリコンゲルマニウム層12と、前記応力緩和シリコンゲルマニウム層12に形成された歪みシリコンからなるチャネル層13と、前記チャネル層13上にゲート絶縁膜14を介して形成されたゲート電極15と、前記チャネル層13の両側に形成された応力を持たないシリコンゲルマニウム層16,17と、前記チャネル層13の両側の前記応力を持たないシリコンゲルマニウム層16,17およびその下部の前記応力緩和シリコンゲルマニウム層12に形成された不純物領域18,19とを有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル長さ方向が<100>結晶軸方向に設置されたn型MISトランジスタを有する半導体装置において、電流特性の向上を効果的に実現する。

【解決手段】(100)結晶面を主面とするシリコン半導体基板の表面領域に、MISトランジスタを構成するための活性領域1と、活性領域1を囲む素子分離領域2とが形成されている。活性領域1の上には、ゲート絶縁膜7およびゲート電極3が形成されている。活性領域1およびゲート電極3の上には、引っ張り応力を有する応力制御膜5が形成されている。応力制御膜5のうちチャネル領域8からゲート幅方向の両側方に位置する部分は、応力制御膜加工領域6となっている。応力制御加工領域6とは、応力制御膜5が非設置の領域、または応力制御膜5が他の領域よりも薄い膜厚で形成されている領域のことをいう。

(もっと読む)

半導体装置

【課題】本発明は、Si/SiGe基板を用いて構成されるMOSトランジスタのキャリアの移動度を向上させるために、基板上の有効な方向に応力がかかるようにすることを特徴とする。

【解決手段】Si及びSiGeの積層構造を有する半導体基板10と、半導体基板上にゲート絶縁膜を介して形成されたゲート電極15と、ゲート電極下の半導体基板表面に形成されたチャネル領域と、チャネル領域を挟むように半導体基板表面に形成されたソース・ドレイン領域17とを具備し、チャネル領域下のGe濃度とソース・ドレイン領域のGe濃度が異なる。

(もっと読む)

半導体装置

【課題】 チャネル領域に十分な歪みを与えることができ、性能の向上をはかることが可能な半導体装置を提供する。

【解決手段】 空洞102を有し、空洞の上方にソース領域108、ドレイン領域108及びチャネル領域を有する半導体基板100と、チャネル領域上にゲート絶縁膜105を介して形成されたゲート電極106と、空洞の上面に形成された第1の部分を有し、チャネル領域に歪みを与える応力発生膜112とを備える。

(もっと読む)

半導体装置

【課題】 半導体チップを折り曲げることにより、Pチャネル電界効果型トランジスタとNチャネル電界効果型トランジスタの移動度を同時に向上させる。

【解決手段】 <110>方向に沿って凹状に折り曲げられた(100)基板11には、<110>方向に沿って(100)基板11の折り曲げ方向と平行にチャネルが配置されたPチャネル電界効果型トランジスタが形成されるとともに、<110>方向に沿って(100)基板11の折り曲げ方向と平行にチャネルが配置されたNチャネル電界効果型トランジスタが形成され、Nチャネル電界効果型トランジスタ上には、(100)基板11の折り曲げによる圧縮応力よりも大きな引っ張り応力F1´を印加するゲートキャップ膜15が形成されている。

(もっと読む)

NMOSトランジスタおよびPMOSトランジスタに凹んだ歪みのあるドレイン/ソース領域を形成する技術

PMOSトランジスタ(110、210)に歪み半導体層(117、217)を形成することで、対応の圧縮歪みチャネル領域(111A)が得られる一方で、他方では、NMOSトランジスタ(120、220)の対応の歪みが緩和され得る。NMOSトランジスタ(120、220)中のシリコン/ゲルマニウムのバンドギャップが低減することで生じる接触抵抗の低下により、全体的なパフォーマンスゲインが実現される。ここでは、特に、一部空乏型SOIデバイスでは、PMOSトランジスタ(110、210)とNMOSトランジスタ(120、220)のシリコン/ゲルマニウム層(117、127、217、227)によって生成される漏れ電流の増加に起因して、有害なフローティングボディ効果もまた低減される。  (もっと読む)

(もっと読む)

1 - 20 / 31

[ Back to top ]