Fターム[5F152LN40]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | その他 (8)

Fターム[5F152LN40]に分類される特許

1 - 8 / 8

半導体装置基板の製造方法および半導体装置基板

【課題】特定方向の基板反りを抑制できる半導体装置基板の製造方法を実現する。

【解決手段】ガラス基板11の裏面に、ストライプ形状にパターニングされた応力制御層51を形成する。応力制御層51の形成後に、ガラス基板11のおもて面にCLC技術を用いて多結晶シリコン膜を形成する。応力制御層51のストライプの長手方向は、CLC技術において使用される連続波レーザの走査方向と垂直な方向に一致させる。

(もっと読む)

半導体基板の製造方法、半導体基板

【課題】シリコン層又はシリコン基板上に、欠陥密度が低く高品質なエピタキシャル層を、少ない工程で低コストに形成することが可能な半導体基板の製造方法を提供する。

【解決手段】シリコンウエーハ11の一面11aに対して、ウエットエッチング法によって異方性エッチングを行う。シリコンウエーハ11の一面11aに対して、異方性エッチングを行うと、シリコンウエーハ11の一面11aに微細な凹凸12が形成される。この微細な凹凸12は、例えば(111)面からなる傾斜面12a,12bで構成された溝14が、周期的に多数形成されたものであればよい。

(もっと読む)

半導体装置の製造方法

【課題】MISトランジスタを備える半導体装置の性能を向上させる。

【解決手段】シリコン基板1の主面s1上のうち、nMIS領域RnにnMIS用ゲート電極GEnを形成し、pMIS領域RpにpMIS用ゲート電極GEpを形成し、それらの側方下部に、それぞれ、n型ソース・ドレイン領域sdnおよびp型ソース・ドレイン領域sdpを形成する。続いて、シリコン基板1の主面s1と両ゲート電極GEn,GEpとを覆うようにして、引張応力を持つ第1応力膜N1aを形成する。その後、pMIS領域Rpの第1応力膜N1aにイオン注入300を施すことで応力を緩和させる。その後、熱処理を施すことで両ゲート電極GEn,GEpを結晶化してから、第1応力膜N1aを除去する。両ゲート電極GEn,GEpを結晶化する工程では、第1応力膜N1aの引張応力をnMIS用ゲート電極GEnに記憶させる。

(もっと読む)

歪み半導体基板の製造方法および歪みMOSFETの製造方法

【課題】歪み緩和バッファ層を設けることなく、結晶構造を有する半導体基板の表面に歪み半導体層を形成でき、したがって、簡単かつ低コストで歪み半導体基板を作製できる歪み半導体基板の製造方法を提供すること。

【解決手段】結晶構造を有する半導体基板の表面に絶縁膜を形成する(S1)。半導体基板の材料とは格子定数が異なる元素をその絶縁膜中にイオン注入する(S2)。その元素が絶縁膜中からはじき出されて半導体基板中に拡散して、その元素を要因とした歪みが半導体基板に生じるように熱処理を行う(S3)。

(もっと読む)

半導体装置およびその製造方法

【課題】

埋め込み絶縁(BOX)膜の薄い完全空乏型シリコンオンインシュレータ(FDSOI)型トランジスタで、トランジスタの性能向上を図る歪印加手法の効果の増大を図る。

【解決手段】

極薄のSOI構造6を有するFDSOI型トランジスタで、極薄のBOX層4の裏側5に応力発生領域を設けてチャネル形成部分に歪を印加する。応力発生領域は、BOX裏側の所望の領域をイオン注入により非晶質化させ、しかる後に応力印加膜3を形成した状態において熱処理再結晶化を行うことにより、応力印加膜3からの応力をチャネル形成部分に転写させることで形成する。

(もっと読む)

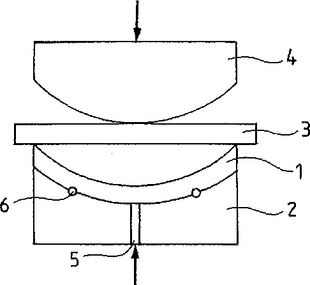

応力下の構造体の組立により複合構造体を作製する方法

本発明は、複合マイクロエレクトロニック構造体の作製方法に関し、2つの基本マイクロエレクトロニック構造体1、3が、その2つの結合面で組み立てられる。本発明は、組立前に、接線応力状態における差が組み立てられる2つの面間で引き起こされ、この差が、組立条件に対する所与の条件下で、組立構造体内で所定の応力状態を得るように選択されることを特徴とする。  (もっと読む)

(もっと読む)

埋め込みp+シリコン・ゲルマニウム層の陽極酸化による歪みシリコン・オン・インシュレータ

【課題】ウエハ・ボンディングを回避し、歪み半導体オン・インシュレータ(SSOI)基板を製造する、コスト効率がよく製造実施可能な方法と、この方法によって製造されたSSOI基板とを提供する。

【解決手段】本方法は、基板の上にさまざまなエピタキシャル半導体層を成長させる工程であって、半導体層の少なくとも一つはひずみ半導体層の下にあるドープされた緩和半導体層である工程と、ドープされた緩和半導体層を電解陽極酸化プロセスによって多孔質半導体に変換する工程と、酸化して多孔質半導体層を埋め込み酸化物層に変換する工程と、を含む。本方法は、基板の上の緩和半導体層と、緩和半導体層の上の高品質埋め込み酸化物層と、高品質埋め込み酸化物層の上の歪み半導体層と、を備えるSSOI基板を提供する。本発明によれば、緩和半導体層と歪み半導体層とは同一の結晶配向を有する。

(もっと読む)

空洞を有するシリコン基板上の高移動度MISFET半導体装置及びその製造方法

MISFETの高性能化を実現する高移動度歪みシリコン構造に、低欠陥かつ低コストで移動度を向上した半導体装置を提供する。MISFETの高性能化を実現する高移動度歪みシリコン構造として、空洞を有するシリコン基板上に、格子緩和シリコン・ゲルマニウム膜/濃度傾斜シリコン・ゲルマニウム膜を形成し、さらにその上に歪みシリコン膜を形成する。これにより、空洞近傍の格子の束縛が緩み、自由度が増すことにより、シリコン・ゲルマニウム膜の薄膜化が実現できるため、低欠陥かつ低コストで移動度を向上した半導体装置を提供できる。 (もっと読む)

1 - 8 / 8

[ Back to top ]