Fターム[5H007CC14]の内容

インバータ装置 (60,604) | 主回路 (6,673) | 入力回路(CH−IV) (2,416) | 直流直列接続 (71) | 分圧によるもの (37)

Fターム[5H007CC14]に分類される特許

1 - 20 / 37

インバータ装置及びそれを備えた空気調和機

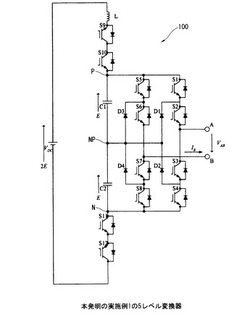

マルチレベル電力変換器

【課題】電圧均一回路を用いることなく、半導体素子の必要個数を減らし、装置の小型化及びコスト低減ができるマルチレベル電力変換器を提供する。

【解決手段】直流電源VDCと、該VDCの正、負極端間に順次直列接続されたリアクトルL,スイッチング素子S9,S10,コンデンサC1,C2,スイッチング素子S11,S12と、前記C1,C2の直列体の両端間に各々接続されたS1〜S4とS5〜S8と、前記S1,S2の共通接続点とS3,S4の共通接続点との間に直列接続されたダイオードD1,D2と、前記S5,S6の共通接続点とS7,S8の共通接続点との間に直列接続されたダイオードD3,D4と、前記S1〜S8のオン、オフ制御によってマルチレベル電圧を切り換える制御手段とを備え、前記D1、D2間、D3、D4間、C1、C2間を共通に接続し、前記S2、S3間と、S6、S7間を交流出力端子A,Bとする。

(もっと読む)

電力変換装置

【課題】電力変換装置の半導体素子群の発熱ばらつきを活かして、冷却器の冷却性能を向上し、かつ回路のインダクタンスを最小限にして、冷却器の小型化を図る。

【解決手段】ユニット構成する半導体素子群は、冷却器受熱部1に設置され自冷あるいは風冷により放熱するようにし、第1、第4の半導体素子Q1,Q4を冷却器受熱部の下側に配置し、第2、第3の半導体素子Q2,Q3を中央に配置し、第1のダイオードD5と第2のダイオードD6を上側に配置し、第1、第2の半導体素子Q1,Q2、第3、第4の半導体素子Q3,Q4はそれぞれ冷却器の上下方向の中心線に対し、左右方向で互いに反対側の位置に配置し、第1のダイオードD5は、第2の半導体素子Q2と前記中心線に対し左右方向で同じ側に配置し、第2のダイオードD6は、第3の半導体素子Q3と前記中心線に対し左右方向で同じ側に配置する。

(もっと読む)

電力変換装置

【課題】本発明は、製造が容易な構成の電力変換装置を提供する。

【解決手段】本発明は、3レベルインバータ10a,10bを、2n個直列に接続してある直列3レベルインバータ群と、直列3レベルインバータ群のうちの2個の前記3レベルインバータの出力を選択する少なくとも1個のスイッチ回路11とを備える電力変換装置10である。スイッチ回路11は、前記直列3レベルインバータ群の隣合う2個の3レベルインバータ10a,10bの出力のうち、いずれか一方を選択することが可能なように2n−1個接続し、スイッチ回路が2個以上の場合、前段に接続された2個のスイッチ回路の出力のうち、いずれか一方を選択することが可能なように次段のスイッチ回路を順に接続して1つの出力を得る。

(もっと読む)

マルチレベルインバータ回路

【課題】4レベル以上のダイオードクランプ形マルチレベルインバータであっても、DCリンクコンデンサの電圧均一性を確保することのできるマルチレベルインバータ回路を提供する。

【解決手段】本発明に係るマルチレベルインバータ回路は、共振形スイッチトキャパシターコンバータを用い手いることを特徴のひとつとする。また、マルチレベルインバータ回路は、マルチレベルインバータ部と、マルチレベルインバータ部とDCリンクコンデンサ部を介して接続されるRSCC部と、を有することを特徴とする。

(もっと読む)

インバータ装置、および、このインバータ装置を備えた系統連系インバータシステム

【課題】マルチレベルインバータ回路において、スイッチング素子のスイッチング回数を減少させることができ、かつ、中間の電位を制御することができるインバータ装置を提供する。

【解決手段】マルチレベルインバータ回路と制御回路とを備えるインバータ装置において、制御回路が、第1の信号と第2の信号とを組み合わせた第1の指令値信号と、前記第1の信号に対して位相が2π/3だけ遅れた信号と前記第2の信号に対して位相が2π/3だけ遅れた信号とを組み合わせた第2の指令値信号と、前記第1の信号に対して位相が4π/3だけ遅れた信号と前記第2の信号に対して位相が4π/3だけ遅れた信号とを組み合わせた第3の指令値信号とに基づいてPWM信号を生成するようにした。第1の信号と第2の信号との組み合わせ方により、マルチレベルインバータ回路の中間の電位の変化の振幅および中心電位が変化する。

(もっと読む)

電力変換装置

【課題】同期PWM制御を有するマルチレベル電力変換装置あるいは直列多重型電力変換装置において、三角波キャリアの周波数fcの設定の自由度を増すことにより制御系の安定性を向上する。

【解決手段】交流電源電圧を直流電圧に変換し変換された直流電圧を交流電圧に変換する電力変換器を複数備え、該複数の電力変換器の交流出力を組み合わせて多レベルの交流電圧を出力する電力変換装置において、前記電力変換装置は三角波のキャリア信号と正弦波の相電圧指令を比較して前記直流電圧を交流電圧に変換する電力変換器をPWM制御するPWM変調器を備え、前記PWM変調器に入力する三角波のキャリア信号の周波数と前記相電圧指令の周波数の比は、3の奇数倍の外に、3の偶数倍、3の奇数倍および偶数倍を除く整数倍を含む。

(もっと読む)

放電制御回路

【課題】電力供給時の電力消費を小さくすると共に、電源遮断時には当該平滑コンデンサに蓄積された電荷を速やかに放電させることが可能であり、放電を制御するスイッチの耐圧が低く抑えられた放電制御回路を提供する。

【解決手段】第1抵抗器1と第2抵抗器2とが直列接続されて構成されていると共に、平滑コンデンサ9に対して並列に接続されている抵抗直列部3と、第1抵抗器1と並列に接続されると共に、主電源20と電気回路30との接続が維持されている際には非導通状態に制御され、主電源20と電気回路30との接続が切断された際には導通状態に制御されて第1抵抗器1の両端を短絡させるスイッチ4とを備え、電気回路30へ直流電力を供給する主電源20と電気回路30との間に介在された平滑コンデンサ9に蓄積された電荷を、主電源20と電気回路30接続が切断された際に放電させる。

(もっと読む)

共振型電力変換装置

【課題】非常時に迅速且つ確実に停止できる共振型電力変換装置。

【解決手段】共振コンデンサ6a〜6dが並列に接続されたノーマリオフ型のスイッチQ1〜Q4を複数個用いて単相又は三相ブリッジ接続した第1スイッチ回路、直流電源1及び第1スイッチ回路に接続され第1スイッチ回路の各共振コンデンサと共振回路を形成する共振リアクトル5及び共振用スイッチQ7を有し、第1スイッチ回路の各ノーマリオフ型のスイッチをゼロ電圧スイッチングさせる第2スイッチ回路を備え、直流電源の直流電力を第1スイッチ回路で交流電力に変換して出力する装置で、第2スイッチ回路の共振用スイッチはノーマリオン型のスイッチであり、第1スイッチ回路の各ノーマリオフ型のスイッチ及び第2スイッチ回路のノーマリオン型のスイッチはそれぞれ、制御端子と一方の主端子との間を短絡する短絡手段12a〜12fが接続され短絡手段は常時に動作しないよう制御され非常時に動作するよう制御される。

(もっと読む)

電力変換装置

【課題】200V系電源に接続される倍電圧整流回路とインバータ回路を備えた200V系電源用の電力変換装置を提供する。

【解決手段】200V系の交流電源(1)に接続され、該交流電源(1)からの電流を倍電圧整流するように構成されたコンバータ回路(20)と、6つのスイッチング素子(31)を有してコンバータ回路(20)により倍電圧整流された直流を交流に変換するインバータ回路(30)を備えている。スイッチング素子(31)は、ワイドバンドギャップ半導体が用いられたユニポーラ素子であるSiC-MOSFETからなっている。

(もっと読む)

電力変換装置

【課題】正、負直流電源の発電能力が異なっている場合でも、正、負直流電源それぞれの最大発電能力を引き出すことを可能にして、システム発電効率の向上を図ることにある。

【解決手段】直流電力を交流に変換するインバータとして中性点クランプ方式インバータ5(NPCインバータ)を用い、このNPCインバータ5の中性点と直列接続した正側直流電源1Pと負側直流電源1Nの中性点とを接続する構成とし、その上で、NPCインバータ5で直流回路の正負電力の分担比率を制御する。

(もっと読む)

鉄道車両駆動制御装置

【課題】駅から発車するときや駅へ停車するときなどの低速での電動機による耳障りな電

磁音を低減するとともに、トルクショックを防止して乗り心地が悪化することを防止する

ことが可能な鉄道車両駆動制御装置を提供することを目的とする

【解決手段】

車両を駆動する交流電動機と、直流電圧を任意の電圧と任意の周波数の交流電圧に変換し

て前記の交流電動機に交流電力を供給する電力変換手段と、前記電力変換手段が内蔵する

スイッチング素子を各々ON(導通)・OFF(阻止)するためのスイッチング信号を出

力する制御手段を有し、前記制御手段において、スイッチング信号として出力する波形を

、非同期パルス波形から同期パルス波形へ、または同期パルス波形から非同期パルス波形

へ切替える場合に、前記出力周波数と前記搬送波周波数に基づき切替えることを特徴とす

る鉄道車両駆動制御装置。

(もっと読む)

3レベルインバータ回路

【課題】複数の3レベルインバータ回路を1つのユニットに収納する場合の装置の小形化及び低コスト化に有効な3レベルインバータ回路を提供する。

【解決手段】3レベルインバータ回路30の各素子パッケージは、取付板15の平面上に第1の結合ダイオード5、第1のIGBT1〜第4のIGBT4、第2の結合ダイオード6の順に直線上に配置される。第1及び第2の結合ダイオード5及び6が第1〜第4のIGBT1〜4の外側に配置されているので、第1及び第2の結合ダイオード5及び6の絶縁バリア16及び17との干渉を避ける必要がある積層接続板9の上部導体板10を1つの接続導体板で構成することができ、スナバ回路を必要とせずターンオフサージ電圧を抑制することができる3レベルインバータ回路を簡素な形状で構成できる。3相分を1ユニットに収容する場合は、3本のAC引出配線を通すように第2のIGBT2と第3のIGBT3間の間隙を広げる。

(もっと読む)

電力変換装置

【課題】2倍のスイッチング電圧を回避し且つ低次の高調波を低減した電圧を得る。

【解決手段】三相インバータ2のスイッチング動作をPWM制御する制御部4を備えた低次高調波消去PWM制御方式の電力変換装置において、制御部4は、インバータ2の変調率mを演算する変調率演算手段5と、インバータ出力電圧の特定の高調波を低減し且つ三相出力電圧の線間電圧が最大値と3番目に大きい値とを遷移する期間thmを所定の時間だけ確保したスイッチングパターンth1、th2、th3を変調率の大きさ毎に記憶している記憶手段6と、スイッチングパターンと出力電圧指令の位相thとから、インバータのスイッチング素子をオンオフするゲート信号を発生するゲート信号発生手段7とを備えている。

(もっと読む)

コンデンサの放電回路

【課題】コンデンサの放電回路において、複数のコンデンサの充電電圧の残留を防止した上で、回路を小型化し、コストを低減する。

【解決手段】スイッチ12を開放した上で第1のIGBT34aのゲートに制御信号を入力してオン状態とすると、第1のコンデンサ13の電圧が第1の放電用抵抗15、第1のIGBT34aのルートで放電し、第2のIGBT34bのゲートに制御信号を入力してオン状態とすると、第2のコンデンサ14の電圧が第2のIGBT34b、第2の放電用抵抗17のルートで放電する。これによりコンデンサ13,14の電圧がともに0ボルトまで放電する。これら第1のIGBT34aと第2のIGBT34bのゲートを介在した制御を行なうことで、放電スイッチおよびチョッパスイッチの機能を実現する。

(もっと読む)

交流電流発生回路

【課題】簡易な回路構成で歪みの小さい交流電流を発生する交流電流発生回路を提供することを課題とする。

【解決手段】グランド11aと直流電源10との間に直列に接続された第1〜第4のキャパシタ12a〜12dと、一端が各キャパシタの直流電源側の一端に接続された第1〜第4のスイッチ素子13a〜13dと、一端が第1〜第4のスイッチ素子13a〜13dの他端に接続され、他端がグランド11bに接続された第0のスイッチ素子13zと、一端が第1〜第4のスイッチ素子13a〜13dの他端と第0のスイッチ素子13zの一端とに接続され、他端が第2のキャパシタ12bと第3のキャパシタ12cとの間に接続されたインダクタ14と、第0のスイッチ素子及び第1〜第4のスイッチ素子を、第0,第1,第2,第3,第4の正順序でそれぞれ所定時間づつオンに制御し、次にそれと逆順序でそれぞれ所定時間づつオンに制御する制御回路15とを有する。

(もっと読む)

電力変換回路

【課題】多レベルの出力が可能な電力変換回路で使用する素子数を最小限にして小型化,低コスト化を可能とする。

【解決手段】例えば、18in1モジュール2Aと、従来の2レベルインバータ回路に使用されている6in1モジュール2Bの2台を隣り合わせに設置し、モジュール2Aでは出力端子T1,T2,T3とコンデンサまたは電池1A〜1Dの中間電位端子A,B,Cとを結線する一方、出力端子T4,T5,T6と、モジュール2Bの出力端子T7,T8,T9とを結線し、負荷(モータ)4に結線して構成する。これにより、Vp,Va,Vb,Vc,Vnの5レベルの電圧出力を可能とする。

(もっと読む)

半導体モジュール

【課題】3レベルインバータ回路を従来の半導体モジュールを用いて構成すると配線インダクタンスが大きくなり、半導体素子に過大な電圧が印加される。

【解決手段】直流電源のPN間に接続されるIGBTの直列接続回路と、この直列接続回路の直列接続点と直流電源の中性点との間に接続する交流スイッチ素子を一つのパッケージに内蔵することにより、配線インダクタンスの低減と装置の低価格化を実現する。

(もっと読む)

3レベルインバータ装置

【課題】短絡故障が生じたとき、直流コンデンサが過電圧となるのを防止し、且つ装置の稼働率を悪化させないようにした3レベルインバータ装置を提供する。

【解決手段】出力側に正及び負の分圧コンデンサ1P、1Nを備え、3レベルの電位を有する直流電源1と、この直流電源1に並列に接続された3組のスイッチングレグ2U、2V及び2Wと、直流電源1と各々のスイッチングレグ2U、2V及び2Wの中点間に設けられた遮断器5によって構成する。各々のスイッチングレグ2U、2V及び2Wの正側アームには正側ヒューズF1が、また負側アームには負側ヒューズF2が、夫々直列に接続されたスイッチング素子Q1、Q2、Q3及びQ4と直列に接続されている。

(もっと読む)

電力変換装置

【課題】スイッチング素子にワイドバンドギャップ半導体を用いても装置全体のコストアップを抑えられるような電力変換装置を得る。

【解決手段】主スイッチング素子(13)をSiC半導体からなるチップによって構成する。そして、そのチップサイズは、オン電圧降下が従来のSi半導体からなるチップと同等以上になるようなサイズにする。これにより、チップの小型化を図ることができ、装置全体の小型化及びコストの低減を実現することができる。

(もっと読む)

1 - 20 / 37

[ Back to top ]