Fターム[5J022AA14]の内容

アナログ←→デジタル変換 (13,545) | A/D変換器の型式 (1,573) | 上位桁・下位桁分離合成型A/D (205)

Fターム[5J022AA14]の下位に属するFターム

Fターム[5J022AA14]に分類される特許

1 - 20 / 42

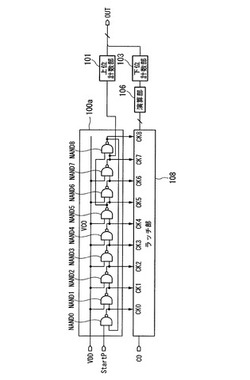

AD変換回路および撮像装置

【課題】エンコードエラーの発生を抑圧することができるAD変換回路および撮像装置を提供する。

【解決手段】VCO100aの出力信号CK0〜CK8のうち出力信号CK7が上位計数部101のカウントクロックとなる。演算部106は、出力信号CK7を基準として定義される出力信号CK0〜CK8の状態(状態0〜状態7)を検出するため、各出力信号の論理状態の変化位置を検出し、検出された変化位置に基づいて下位計数信号を生成する。演算部106がこの変化位置を検出する際の手順では、立下りエッジが略同時になる出力信号CK0と出力信号CK7の論理状態の比較は行われない。このため、エンコードエラーの発生を抑圧することができる。

(もっと読む)

固体撮像装置

【課題】従来よりも高精度かつ高速の変換が可能なカラムADCを内蔵した固体撮像装置を提供する。

【解決手段】固体撮像装置200において、各変換部12は、対応の垂直読出線9を介して出力された各画素の信号を第1〜第N(Nは3以上の整数)の変換ステージを順に実行することによってデジタル値に変換する。第1〜第N−1の変換ステージでは、各変換部12は、画素の信号を保持する保持ノードND1の電圧を所定の電圧ステップずつ変化させながら参照電圧と比較することによって、デジタル値の最上位ビットを含む上位の複数ビットの値を決定する。第Nの変換ステージでは、各変換部12は、第N−1の変換ステージにおける電圧ステップの範囲またはそれを超える範囲で、保持ノードND1の電圧を連続的に変化させながら参照電圧と比較することによって、残りの最下位ビットまでの値を決定する。

(もっと読む)

アナログデジタル変換器および信号処理システム

【課題】面積の増大を防止でき、かつサンプリングされるコース用ADCとファイン用ADC間のアナログ信号に誤差が生じることを抑止できるAD変換器および信号処理システムを提供する。

【解決手段】アナログ入力信号をNビットのデジタル信号に変換する際に、上位mビットのデジタル信号に変換するコース(Coarse)AD変換器と、コースAD変換器の変換結果に基づきアナログ入力信号の下位nビット(n=N-m)のデジタル信号に変換するファイン(Fine)AD変換器と、アナログ入力信号をサンプリングし、コース用参照電圧との比較電圧をコースAD変換器に供給し、ファインAD変換器の変換結果に応じたファイン用参照電圧との比較電圧を上記ファインAD変換器に供給するTH回路と、を含み、TH回路は、アナログ入力信号、コース用参照電圧、ファイン用参照電圧の選択的入力経路でサンプリング容量を共有する。

(もっと読む)

ハイブリッド・アナログ/デジタル変換器、イメージセンサおよび複数のデジタル信号を提供するための方法

【課題】パワーおよびエリア比により良い変換率を有するアナログ/デジタル変換器を提供する。

【解決手段】ハイブリッド・アナログ/デジタル変換器100は、複数の変換回路101a〜101nを含む。それぞれの変換回路は、逐次近似変換の結果として、デジタル信号103a〜103nの第1の数のビットを得るために逐次近似変換を実行することによって、さらに、デジタル信号の第2の数のビットを得るために共通可変基準電圧105に基づいて傾斜変換をその後に実行することによって、アナログ入力信号104a〜104nに基づいてデジタル信号を提供するように構成され、第2の数のビットは、アナログ入力信号および逐次近似変換の結果間の残差に対応する。ハイブリッド・アナログ/デジタル変換器は、複数の変換回路のそれぞれの変換回路に共通可変基準電圧を提供するように構成される共通可変基準電圧プロバイダ102をさらに含む。

(もっと読む)

逐次比較型A/D変換器

【課題】同時サンプリング機能を有する逐次比較型A/D変換器の回路面積の低減。

【解決手段】Nチャネルのアナログ信号を同時サンプリングし、A/D変換する逐次比較型A/D変換回路であって、N個の容量主DACMDACCA,MDACB,MDACCと、抵抗副DACSDACと、N個のコンパレータCMPA,CMPB,CMPCと、逐次比較制御回路SARP1と、を備え、逐次比較制御回路は、N個の容量主DACおよびN個のコンパレータを制御して、Nチャネルのアナログ信号のAD変換結果の上位側ビットの値をそれぞれ決定し、抵抗副DACおよびN個のコンパレータを制御して、Nチャネルのアナログ信号のAD変換結果の下位側ビットの値を、それぞれ決定する。

(もっと読む)

光・周波数アナログ・ディジタル変換及び光・時間アナログ・ディジタル変換を組み合わせた画素センサ

光は、第1の動作フェーズ中に受け取られる上記光の光・周波数変換を行うことにより、電気信号に変換される。第1の動作フェーズに続き、第2の動作フェーズ中に受け取られた光に対して光・時間変換が行われる。第2の動作フェーズに続き、光のディジタル表現が、光・周波数変換及び光・時間変換に応じて生成される。  (もっと読む)

(もっと読む)

アナログデジタル変換回路及びアナログデジタル変換方法

【課題】消費電力を抑制することができるアナログデジタル変換回路を提供する。

【解決手段】抵抗体3、上位コンパレータ4a、下位コンパレータ4b、上位エンコーダ結果記憶手段6、前値上位コンパレータ7を備え、先発の入力信号の上位コードを上位エンコーダ結果記憶手段に記憶しておき、前値上位コンパレータで次発の入力信号の電圧値を判断し、先発の入力信号の上位コードと同一の上位コードである場合には、上位コンパレータ及び上位エンコーダを駆動することなく、上位エンコーダ結果記憶手段に記憶された上位コードを次発の入力信号の上位コードとして採用する。

(もっと読む)

A/D変換回路及び固体撮像装置

【課題】 特性のバラツキに起因する変換精度の低下防止と回路規模の増大防止の両方を効果的に実現できるサブレンジング方式のA/D変換回路及び固体撮像装置を提供する。

【解決手段】 直列接続された容量素子C1〜C3と、容量素子C1の出力値と閾値電圧値Vthを比較する電圧比較回路CMPと、容量素子C1とC2間のノードに被変換アナログ電圧信号Vpixを入力する第1入力回路と、容量素子C2とC3間のノードに、上位ビットの値を求める第1変換処理の実行期間中に、電圧値が単調変化する第1参照電圧を入力する第2入力回路と、容量素子C3の入力端に、第1変換処理終了後に未変換ビットの値を求める第2変換処理の実行期間中に、電圧値が単調変化する第2参照電圧を入力する第3入力回路と、第1変換処理における電圧比較回路CMPの出力変化時に、容量素子C3に第1参照電圧を保持する制御信号Vctlを生成する制御回路12を備える。

(もっと読む)

A−D変換装置

【課題】電圧−周波数変換方式のA−D変換装置の精度を向上する。

【解決手段】2つの等価な鋸波発生回路18Aおよび18Bと、その2つの鋸波発生回路18Aおよび18Bを交互に切り替えるスイッチ回路19と、を含む電圧制御型発振器24を有する、電圧−周波数変換回路を備える。好ましくは、第1の周期の周期信号を出力する第1の電圧制御型発振器と、第1の周期と異なり、かつ第1の周期と一定の比を保つ第2の周期の周期信号を出力する第2の電圧制御型発振器とを備え、サンプリング周期内に含まれる第1の周期信号の波数に基づいて、入力であるアナログ信号に対応するディジタル信号の上位ビットを算出し、サンプリング信号の活性化時点から第1および第2の周期信号の位相が一致する時点までの間に含まれる周期信号の波数に基づいて、デジタル信号の下位ビットを算出する。

(もっと読む)

直並列型アナログ/デジタル変換器及びアナログ/デジタル変換方法

【課題】高速化を図ることができる直並列型アナログ/デジタル(AD)変換器を提供する。

【解決手段】アナログ信号の電圧をサンプリングするリセットモードとアナログ信号の電圧と参照電圧との比較を行う比較モードとを交互に行う比較段を有する上位及び下位ビット用比較部と、上位ビット用比較部の比較結果に応じた参照電圧を参照電圧生成器から選択して下位ビット用比較部に出力する参照電圧選択部とを有するAD変換器において、下位ビット用比較部はインターリーブ動作する複数の比較段を有し、上位ビット用比較部のリセットモード時に複数の比較段のうち一つの比較段をリセットモードで動作させ、上位ビット用比較部の比較モード時に複数の比較段のうち一つの比較段を比較モードで動作させ、さらに、下位ビット用比較部の複数の比較段のうち一つの比較段がリセットモードのとき他の比較段に参照電圧選択部から参照電圧を入力する。

(もっと読む)

データ処理方法、データ処理装置、固体撮像装置、撮像装置、電子機器

【課題】参照信号比較型AD変換方式を採用する固体撮像装置において、消費電力の低減が可能な仕組みを実現する。

【解決手段】高速クロックCK1で動作する下位Mビットのカウンタ部と高速クロックCK1を2^M分周した低速クロックCK2で動作する上位“N−M”ビットのカウンタ部に分け、下位Mビットと上位“N−M”ビットの各カウンタ部を選択的に動作させる。カウント動作有効期間TENに関する高速クロックCK1でのカウント値に対する、低速クロックCK2でカウントされた上位“N−M”ビットのデータHの過不足分を、高速クロックCK1でカウントされた下位MビットのデータLで修正する。不足時にはカウント値Hにカウント値Lを加算する修正を行ない、超過時にはカウント値Hからカウント値Lを減算する修正を行なう。上位ビットカウンタ部でのカウント値Hと下位ビットカウンタ部でのカウント値Lとを繋ぎNビットデジタルデータにする。

(もっと読む)

アナログ量をデジタル化するための方法、前記方法を実装するデジタル化装置、及びそのような装置を統合する電磁放射線検出器

【課題】電磁放射線検出器が出力するアナログ量をデジタル化する方法を提供する。

【解決手段】元素センサのマトリクスを備える電磁放射線検出器が出力するアナログ量(VE)をデジタル化する方法であって、マトリクスの各行または各列に関して、積分器ステージを使用してアナログ量の第1の積分段階を実行する処理と、積分されたアナログ量(VS)を比較器ステージの出力端子に接続された2進カウンタ及びメモリ素子により第1の数値(B)に変換する処理と、第1の数値をアナログ信号(VDAC)に変換する処理と、アナログ信号(VDAC)をアナログ量(VE)から減算する処理と、減算結果(VE-VDAC)を第1の数値に相当する利得で増幅する処理と、増幅されたアナログ信号“2B・(VE-VDAC)”に比例する第2の数値(M)を生成するために、第2の積分段階を実行する処理と、アナログ量(VE)に相当する数“N”を形成するために第1の数値と第2の数値とを加算する処理とを含む。

(もっと読む)

アナログ・デジタル変換器

【課題】比較器のオフセット異常によるA/D変換器の歩留まり低減を回避する構成のパイプライン型A/D変換器の提供。

【解決手段】カスケード接続され、前段より入力されたアナログ信号を所定ビットのデジタル信号に変換して出力する、第1乃至第N(ただし、Nは2以上の整数)のステージ(101〜10N)を備え、第1乃至第N−1のステージ(101〜10N−1)の各々が、アナログ信号を予め定められた互いに異なる基準電位と並列に比較する比較器を含むアナログデジタル変換回路を備え、第1乃至第N−1のステージは、該ステージの比較器が予備の比較器を備えた冗長構成とされ、前記冗長構成の比較器のうちの1つを選択的に活性化する比較器選択信号を出力する比較器選択回路(40)を備え、冗長構成の比較器について、オフセットが許容値を超えている比較器であると判定された場合、前記比較器選択信号に基づき、オフセットが許容値を超えている比較器は予備の比較器で置き換えられる。

(もっと読む)

デジタル回路、並びにそれを備えたアナログ/デジタル変換回路

【課題】ゲイン誤差および歪みによる出力の誤差の補正を行い、AD変換回路のAD変換精度を向上させるデジタル回路、並びにそれを備えたAD変換回路を実現する。

【解決手段】AD変換回路30は、デジタル回路20を備えている。デジタル回路20は、ゲイン誤差および歪みによる誤差を補正するための補正係数Sを算出する解算出部14と、この解算出部14にて算出された補正係数Sを用いて、上記誤差を補正するAD出力補正部16とを備えている。

(もっと読む)

フォールディング回路およびアナログ−デジタル変換器

【課題】小信号応答性がよく、クロック信号の負荷を軽減でき、面積の増大を防止することができるフォールディング回路およびアナログ−デジタル変換器を提供する。

【解決手段】複数の異なる電圧を基準電圧として発生させる基準電圧発生回路120と、基準電圧とアナログ入力電圧と差電圧を差電流に変換して出力する複数のアンプ140と、を有し、アンプの出力端が交互に接続され、アンプはカスコード出力トランジスタを有する差動アンプで構成されており、カスコードトランジスタの両ソース間に制御クロックに同期してオン状態となるスイッチが設けられている。

(もっと読む)

アナログ−ディジタル変換装置

【課題】全差動増幅回路に信号を巡回させてアナログ信号をディジタルデータに変換するアナログ−ディジタル変換回路に関し、変換精度を向上できるアナログ−ディジタル変換装置を提供することを目的とする。

【解決手段】本発明は、全差動増幅回路(113)に信号を巡回させてアナログ信号をディジタルデータに変換するアナログ−ディジタル変換回路において、全差動増幅回路(113)の接続極性を切り換える極性切換手段(115)と、第1巡目と第2巡目以降とで全差動増幅回路(113)の接続極性が切り換わるように極性切換手段(115)を制御する制御手段(116)とを有することを特徴とする。

(もっと読む)

アナログ・ディジタル変換器

【課題】A/D変換器の内部でノイズが発生した場合にも、精度を損なうことなくA/D変換が可能なA/D変換器を提供する。

【解決手段】制御回路101、DAコンバータ102、スイッチ付きコンパレータ103、逐次比較レジスタ104、及びDAコンバータ105によって、アナログ入力信号S001を上位ビットと下位ビットに分けたうちの上位ビット部分を出力する上位ビット用AD変換部を構成し、また下位ビット用に並列型ADコンバータ106を設ける。そして、多数決回路107によって、並列型ADコンバータ106の出力(AD変換結果)を複数回サンプリングして、多数決により、下位ビットにおける各ビットの値を決定して出力する。

(もっと読む)

A/D変換回路

【課題】インターポレーション回路における複数の抵抗の直列接続するとき、接続配線に生じる寄生容量のばらつきを低減すること。

【解決手段】それぞれ位相の異なる正相信号及びその逆相信号を生成して出力する複数のフォールディングアンプと、フォールディングアンプの出力から複数の同相及び逆相の補間信号を生成するインターポレーション回路と、このインターポレーション回路によって生成される補間信号を入力する複数のコンパレータと、これらのコンパレータからの出力をエンコードするエンコーダ回路6とを備え、インターポレーション回路は、複数の抵抗を所定数毎に分けて、所定数の抵抗が直線上に直列接続される抵抗列を複数並設し、各抵抗列の一端部の抵抗同士を2つの列毎にそれぞれ接続し、各抵抗列の他端部の抵抗同士を前記2つの列の組み合わせとは異なる組み合わせの2つの列毎にそれぞれ接続して複数の抵抗を環状に接続した。

(もっと読む)

AD変換器、無線受信機

【課題】消費電力の増大を招くことなく、受動素子の数を削減しチップ占有面積を小さくして低コスト化を図ることが可能なAD変換回路を提供すること。

【解決手段】n次元ベクトルを表すm(n<m<2n)個のアナログ信号のそれぞれを1ビット以上に量子化してm個並列の量子化信号を生成する量子化部と、このm個並列の量子化信号をそれぞれ復号してm個の復号アナログ信号を生成する復号部と、このm個のアナログ信号のそれぞれと上記m個の復号アナログ信号のそれぞれとの差のそれぞれを定数倍してm個の増幅残差信号を出力する残差増幅部と、を有する変換ステージを複数縦続接続して備えた変換部と、この変換部の変換ステージそれぞれにおけるm個並列の量子化信号を該変換ステージの縦続位置に応じた遅延量を考慮して並列位置ごとに合成し、m個並列のディジタル信号を生成する合成部とを具備する。

(もっと読む)

A/D変換器

【課題】異なる仕様の複数のA/D変換器を同一チップに搭載する場合においてチップ面積を削減する。

【解決手段】A/D変換器は、オペアンプに接続される入力コンデンサ、帰還コンデンサ、積分コンデンサのうち少なくとも1種類を含むコンデンサ群2と、異なる仕様の複数の半導体集積回路群1A,1Bと、コンデンサ群2を複数の半導体集積回路群1A,1Bのうちの何れか1つに選択的に接続して、選択した半導体集積回路群とコンデンサ群2にA/D変換を実行させる切替回路となるスイッチ群3A,3Bとを有する。

(もっと読む)

1 - 20 / 42

[ Back to top ]