Fターム[5J032AC13]の内容

Fターム[5J032AC13]の下位に属するFターム

電源投入時 (14)

Fターム[5J032AC13]に分類される特許

1 - 9 / 9

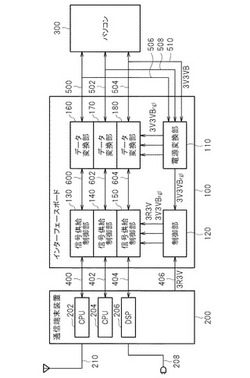

信号供給制御回路、信号供給制御回路の動作方法、制御方法、及び信号処理回路

【課題】複数の電源の供給を受けて動作する信号処理回路においていずれの電源が供給されない場合にも回路の破壊を回避する信号供給制御回路、信号供給制御回路の動作方法、制御方法、及び信号処理回路を提供する。

【解決手段】複数の電源の供給を受け、複数の電源により動作する通信端末装置200、データ変換部160,170,180への信号の供給を制御する信号供給制御部130,140,150は、複数の電源の少なくとも1つが供給されていない場合に、供給されていない電源とは異なる電源に起因する信号の通信端末装置200、データ変換部160,170,180への供給を制限する。

(もっと読む)

プローブカード及び検査装置

【課題】自動切り替え機構の制御をプローブカード内で行ってテスタから独立させ、テスタからの制御信号数に制限されることがなく、検査対象を増やす。

【解決手段】検査対象物の電極に接触させる複数のプローブと、当該プローブとテスタとを電気的に接続する電源チャネルとを備えたプローブカード及び検査装置である。各電源チャネルをそれぞれ複数の電源配線部に分岐させて前記各プローブにそれぞれ接続させると共に、過電流等の電気的変動に基づいて前記電源配線部を遮断する自動切り替え機構と、前記検査対象物の中に不良品が存在することによって前記電気的変動が生じた場合に、その電気的変動を検出する電気的変動検出機構と、当該電気的変動検出機構で電気的変動を検出した時、当該電気的変動が生じた電源配線部を前記自動切り替え機構で遮断させる制御機構と、を備えた。

(もっと読む)

半導体集積回路

【課題】常時電源オン回路領域の電源が先に遮断されても電源オフ回路領域に悪影響を及ぼすことを防止する半導体集積回路を提供する。

【解決手段】第1電源から電力供給される回路領域である電源オンドメインと、第2電源から電力供給される回路領域である電源オフドメインとを同一チップ上に備え、電源オンドメインは、第1電源がオンかつ第2電源がオフであるときに電源オフドメインと電源オンドメインとの間で入出力される信号を遮断する第1信号遮断部と、第2信号遮断部の遮断を有効または無効にする旨を示す第1制御信号を出力する遮断制御部とを備え、電源オフドメインは、遮断制御部からの遮断を有効にする旨を示す第1制御信号に基づき、電源オンドメインと電源オフドメインとの間で入力される信号を遮断する第2信号遮断部を備え、前記遮断制御部は、第1電源からの電源供給の停止を検出したとき、遮断を有効にする旨を示す第1制御信号を出力する。

(もっと読む)

電子装置

【課題】本発明は、電源電圧の変動時における回路素子間の信号電圧を適切な範囲に抑制する電子装置に関する。

【解決手段】電子装置1は、信号出力回路部2が電源電圧Vaによって動作して信号を信号線5を通して信号入力回路部3に出力し、信号入力回路部3が電源電圧Vbによって動作して信号の処理を行う。保護回路部4は、信号線5に接続され、電源オフ時等において、信号線5を流れる信号の電圧値が、ダイオードD1と抵抗1との接続点Pの電位とダイオードD1の順方向電圧を加算した閾値電圧を超える電圧値になると、ダイオードD1に信号線5から電流を流して、信号線5を流れる信号の電圧値を該閾値電圧以下に抑制する。

(もっと読む)

半導体集積回路

【課題】 複数の半導体集積回路が出力するエラー検出信号のワイヤードORを取って各半導体集積回路にパワーダウン指令信号として与える場合に、各半導体集積回路を安定してパワーダウン状態に移行させる。

【解決手段】 外部からのパワーダウン指令信号PDNがインバータ13の閾値を下回ったときにパワーダウン制御信号をアクティブレベルとするパワーダウン制御回路14と、パワーダウン制御信号が非アクティブレベルのときに、エラーの検出に応じてNチャネル電界効果トランジスタ12をON状態としてエラー検出信号ERNをアクティブレベルとするエラー検出回路11との間に遅延回路15を介挿し、パワーダウン指令信号PDNがインバータ13の閾値を下回った後も、エラー検出信号ERNが非アクティブレベルからアクティブレベルへ向かう方向の変化を継続するようにした。

(もっと読む)

半導体装置

【課題】複数の電源ブロックに分割した半導体装置にて、誤動作を引き起こし得る状態が発生した場合に、その発生を簡便かつ速やかに検出できるようにする。

【解決手段】異なる電源ブロックに配置され、クロックに同期して動作する第1及び第2の記憶回路と、一方の記憶回路の出力端子と他方の記憶回路の入力端子との間に接続される第1及び第2の遅延回路と、記憶回路の入力信号及び出力信号に基づいて誤動作が生じ得る状態であるか否かを判定し、判定結果をエラー検出信号として出力する判定回路とを備え、第1及び第2の記憶回路に異なる初期値を与えて、記憶回路間においてトグル状態で信号が送受信されているか否かをモニターすることにより、誤動作が生じ得る状態になったことを簡便かつ速やかに検出できるようにする。

(もっと読む)

電源ノイズ抑制装置

【課題】ICチップの動作時に発生する電源ノイズ、特に出力バッファが同時動作する際に発生する電源ノイズを低減する電源ノイズ抑制装置を提供する。

【解決手段】電源ノイズ抑制装置は、複数の出力バッファと、該複数の出力バッファの専用電源IO−VDDおよび専用グラウンドIO−VSSの間に接続されたデカップリング容量とを備えるICチップが収納されたパッケージをボード上に搭載すると共に、そのボード上のプレーンと前記専用電源IO−VDDとの間、および/または前記ボード上のプレーンと前記専用グラウンドIO−VSSとの間に、2つの直列RLC回路が並列に接続された直列RLC回路セットを備える。

(もっと読む)

電子回路装置

【課題】複数個の電子回路ブロックと容量素子とが、同じ半導体チップに形成されてなる小型の電子回路装置であって、チップ面積を増大することなく十分なノイズ低減効果が得られると共に、容量素子の容量値および配置に関する自由度が高められた電子回路装置を提供することを目的としている。

【解決手段】半導体チップ1に形成されてなる電子回路装置10であって、主電源ラインMLdおよび主接地ラインMLgから分岐する各分岐ラインALd,ALgをそれぞれの電源ラインALdおよび接地ラインALgとする電子回路ブロックAを、複数個有してなり、複数個の電子回路ブロックA,Bの電源ラインALd,BLdと接地ラインALg,BLgの間に、容量素子C1と、容量素子C1の各電子回路ブロックA,Bへの接続状態を切り替えるスイッチング回路S10とが、挿入配置されてなる電子回路装置10とする。

(もっと読む)

半導体装置及びその冗長救済方法

【課題】 大規模化した半導体装置の歩留向上および信頼性向上が容易に図れるようにすること。

【解決手段】 制御回路108からの制御信号S(i)によって電流測定タイミングになると、各分割論理回路ブロック1051〜r−1の静止電源電流値が測定される。そして制御回路108は、分割論理回路ブロック1051〜r−1の静止電源電流値と基準値とを比較して、静止電源電流が基準値を超える場合、判定信号(i)をLoレベルに設定する一方、静止電源電流が基準値を超えないときは判定信号(i)をHiレベルに設定する。そして、判定信号(i)がLoレベルである不良ブロックを冗長回路ブロック105rと置換するように、セレクタ1062〜r,1071〜r−1に切替え制御信号R(1)〜R(r)を出力し、入出力バスの接続を切り替え、その不良ブロックへの電源供給も停止する。

(もっと読む)

1 - 9 / 9

[ Back to top ]