Fターム[5J039JJ02]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 入力信号特性 (318) | 振幅 (8)

Fターム[5J039JJ02]に分類される特許

1 - 8 / 8

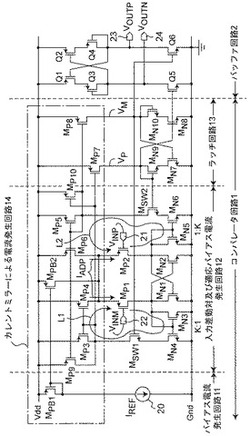

コンパレータ回路

【課題】コンパレータ回路において、従来技術に比較して高速で消費電力を低下させる。

【解決手段】入力される2つの入力電圧に応じて、第1及び第2のMOSトランジスタからなる入力差動対のいずれか1つのMOSトランジスタにおいて、当該1つのMOSトランジスタとスイッチトランジスタとを含むループにより適応バイアス電流を発生する入力差動対及び適応バイアス電流発生回路と、上記適応バイアス電流に対応する電流を検出してラッチ論理を変化させた後、上記スイッチトランジスタをオンからオフに切り換えることにより上記適応バイアス電流を遮断するラッチ回路とを備える。

(もっと読む)

インピーダンス調整回路及びこれを備える半導体装置

【課題】インピーダンス調整回路における調整誤差を低減する。

【解決手段】レプリカ回路1441,1443のインピーダンスをそれぞれ変化させるカウンタ回路1421,1422と、これらカウンタ回路のカウント値を更新するインピーダンス調整制御回路141とを備える。制御回路141は、レプリカ回路1441のインピーダンスが外部抵抗REのインピーダンスよりも低い状態から高い状態に変化したことに応答してカウンタ回路1421のカウント値更新を終了し、レプリカ回路1443のインピーダンスがレプリカ回路1441のインピーダンスよりも高い状態から低い状態に変化したことに応答してカウンタ回路1422のカウント値更新を終了する。これにより、レプリカ回路1441,1443にて生じる調整誤差が相殺される。

(もっと読む)

アナログ信号比較器

【課題】アナログ信号の値を、比較的簡易な回路でかつ短時間で、所定の値と比較する。

【解決手段】所定時間経過後にしきい値を超える基準信号を生成する波形生成回路51Aと、アナログ信号を入力し当該アナログ信号を積分してアナログ積分信号を出力する積分回路52と、前記波形生成回路51Aからの基準信号と、前記積分回路52からのアナログ積分信号とを入力し、前記波形生成回路51Aからの基準信号が所定値に達するまでの時間と積分回路52からのアナログ積分信号が所定値に達するまでの時間とを比較する比較回路と、を備えたことを特徴とするアナログ信号比較器。

(もっと読む)

アナログ信号比較器

【課題】

アナログ信号の値を、比較的簡易な回路でかつ短時間で、所定の値と比較する。

【解決手段】

第1のパルス信号を生成する発振器21Aと、アナログ信号を入力し当該アナログ入力信号を第2のパルス信号に変換して出力するVCO22と、発振器21からの第1のパルス信号を入力する第1のシフトレジスタ241と、VCO22からの第2のパルス信号を入力する第2のシフトレジスタ242と、第1および第2のシフトレジスタ241,242の全ビットまたは一部ビットの値を検出し、これらの検出値に基づき、発振器21Aが生成する第1のパルス信号の個数と、VCO22が生成する第2のパルス信号の個数とを比較するパルス個数比較回路とを備えたことを特徴とするアナログ信号比較器。

(もっと読む)

周波数/位相比較器

【課題】フルレートとハーフレートの両方に対応して、周波数比較モードおよび位相比較モードで正常動作を行うことのできる周波数/位相比較器を得る

【解決手段】フルレートおよびハーフレートのどちらに対してもクロック信号の振幅値をアナログホールド出力するアナログホールド位相比較部10と、フルレートの場合に1/4周期遅れのクロック信号の振幅をデジタルホールド出力し、ハーフレートの場合に1/8周期遅れのクロック信号の振幅をデジタルホールド出力するデジタルホールド位相比較部20、30と、アナログホールド値とデジタルホールド値に基づいて、入力データ信号とクロック信号の周波数比較を行う周波数比較手段50と、デジタルホールド値の極性に応じて、アナログホールド位相比較部10からの出力値と周波数比較手段50からの出力値を選択出力する最終出力信号選択手段60とを備える。

(もっと読む)

差動増幅装置

【課題】1対の入力信号の同相成分に比べ、電圧レベル差が少さい場合でも、これを感知して論理レベルに応じて出力できる差動増幅装置を提供すること。

【解決手段】本発明の差動増幅装置は、第1(IN)及び第2入力信号(INB)が有する電圧レベルの差を感知及び増幅して、第1(OUT)及び第2出力信号(OUTB)として出力するための増幅手段と、前記第1出力信号を第1フィードバック信号(OUT_FD)として、前記第2出力信号を第2フィードバック信号(OUTB_FD)として受けて、前記第1フィードバック信号と前記第2フィードバック信号との電圧レベルの差を増幅するためのフィードバック手段(NM9,10、MN15,16)とを備える。

(もっと読む)

半導体装置の二重基準入力受信器及びその入力データ信号の受信方法

【課題】半導体装置の二重基準入力受信器及びその入力データ信号の受信方法を提供する。

【解決手段】第1及び第2入力バッファと位相検出器とを備える入力受信器であって、第1入力バッファは、クロック信号によって同期して、イネーブルまたはディセーブルされ、ポジティブ入力端子に入力される入力データ信号とネガティブ入力端子に入力される第1基準電圧との電圧差を感知して増幅し、第2入力バッファは、クロック信号によって同期して、イネーブルまたはディセーブルされ、ポジティブ入力端子に入力される第2基準電圧とネガティブ入力端子に入力される入力データ信号との電圧差を感知して増幅する。第1基準電圧のレベルは、入力データ信号のレベルの中間レベルより高く、第2基準電圧のレベルは、入力データ信号のレベルの中間レベルより低い。位相検出器は、第1入力バッファの出力信号と第2入力バッファの出力信号との位相差を検出し、検出された位相差に対応する出力信号を発生させる。

(もっと読む)

比較器

【課題】小面積で計算速度が速い比較器を提供する。

【解決手段】比較器は、各々の入力端にクロック信号が共通して入力される第1及び第2遅延回路と各々の第1入力端に第1遅延回路の出力信号及び第2遅延端の出力信号が各々入力される第1及び第2論理ゲートを含む第1ラッチ回路、及び第1論理ゲートの出力端から出力される信号及び前記第2論理ゲートの出力端から出力される信号をラッチする第2ラッチ回路を備える。第1遅延回路の遅延時間は外部から入力される第1デジタル信号により制御される可変の遅延時間であり、前記第2遅延回路の遅延時間は外部から入力される第2デジタル信号により制御される可変の遅延時間である。

(もっと読む)

1 - 8 / 8

[ Back to top ]