Fターム[5J039JJ19]の内容

パルスの操作 (9,993) | 2以上のパルス(列)の比較 (786) | 比較結果の出力(アナログ) (180) | 比較結果が2端子に生じるもの (5)

Fターム[5J039JJ19]に分類される特許

1 - 5 / 5

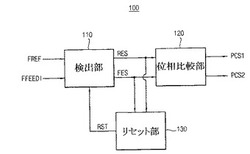

デジタル位相周波数検出器、それを含むデジタル位相固定ループ、及びデジタル位相周波数検出方法

【課題】デジタル位相周波数検出器、それを含むデジタル位相固定ループ、及びデジタル位相周波数検出方法を提供すること。

【解決手段】デジタル位相周波数検出器は検出部、位相比較部及びリセット部を含む。検出部は基準信号及びフィードバック入力信号のエッジを検出して基準エッジ信号及びフィードバックエッジ信号を発生する。リセット部は基準エッジ信号及びフィードバックエッジ信号に基づいてリセット信号を発生する。位相比較部は基準エッジ信号及びフィードバックエッジ信号に基づいて第1位相比較信号及び第2位相比較信号を発生し、第1フリップフロップ、第2フリップフロップ、及びラッチブロックを含む。第1フリップフロップは基準エッジ信号を受信するデータ入力端及びフィードバックエッジ信号を受信するクロック入力端を具備し、第2フリップフロップはフィードバックエッジ信号を受信するデータ入力端及び前記基準エッジ信号を受信するクロック入力端を具備する。

(もっと読む)

同期回路

【課題】小面積で広帯域特性及び低位相雑音特性を得ることが可能な同期回路を提供する。

【解決手段】位相検出器11は、参照信号と帰還信号との位相差を検出する。電圧生成器12,13は、位相検出器の出力信号に基づき電圧を発生する。パルス発生器16は、参照信号に基づきパルス信号を生成する。電圧制御発振器14は、パルス信号に同期して、発振信号を発振する。分周器15は、電圧制御発振器からの信号を分周し、帰還信号を生成する。電圧制御発振器14は、電圧発生回路から供給される電圧レベルをシフトするレベルシフト回路14cと、電圧発生回路からの電圧とレベルシフト回路からのレベルシフトされた電圧により駆動される複数のインバータ回路14a、14bからなるリング発振器とにより構成され、インバータ回路の1つにパルス信号が供給される。

(もっと読む)

デューティ比補正回路及びデューティ比補正方法

【課題】非同期信号のデューティ比を補正可能なデューティ比補正回路を提供すること。

【解決手段】本発明に係るデューティ比補正回路は、第1クロック信号が入力されるクロック用入力バッファと、補正信号に基づいて、前記クロック用入力バッファから出力される第2クロック信号のデューティ比を調整して第3クロック信号を生成するクロック用デューティ調整回路と、第1データ信号が入力されるデータ用入力バッファと、前記補正信号に基づいて、前記データ用入力バッファから出力される第2データ信号のデューティ比を調整して第3データ信号を生成するデータ用デューティ調整回路と、前記第3クロック信号に基づいて、前記補正信号を生成するデューティ比較回路と、を備えるものである。

(もっと読む)

比較器

【課題】小面積で計算速度が速い比較器を提供する。

【解決手段】比較器は、各々の入力端にクロック信号が共通して入力される第1及び第2遅延回路と各々の第1入力端に第1遅延回路の出力信号及び第2遅延端の出力信号が各々入力される第1及び第2論理ゲートを含む第1ラッチ回路、及び第1論理ゲートの出力端から出力される信号及び前記第2論理ゲートの出力端から出力される信号をラッチする第2ラッチ回路を備える。第1遅延回路の遅延時間は外部から入力される第1デジタル信号により制御される可変の遅延時間であり、前記第2遅延回路の遅延時間は外部から入力される第2デジタル信号により制御される可変の遅延時間である。

(もっと読む)

位相比較回路及びクロックリカバリ回路

データ信号とクロック信号の位相差を示す位相差信号を出力する位相比較回路であり、異なる複数の識別レベルを用いてデータ信号の位相を検出し、位相を示す複数の信号を出力する検出部と、検出部から出力される複数の識別レベルに対応する複数の出力信号の各々とクロック信号との位相差を示す複数の位相差信号を出力する位相比較部と、位相比較部から出力される複数の位相差信号の全部又は一部を用いて、複数の位相差信号のうちの1つの信号を出力するか又は出力しないかを制御する制御部とを有するように構成する。  (もっと読む)

(もっと読む)

1 - 5 / 5

[ Back to top ]