Fターム[5J042CA03]の内容

Fターム[5J042CA03]に分類される特許

1 - 11 / 11

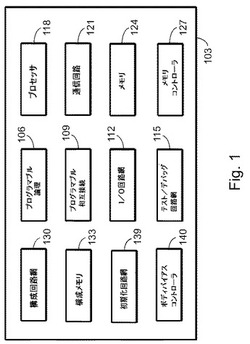

フィールドプログラマブルゲートアレイの性能を向上させるための装置および関連方法

【課題】性能が向上されたフィールドプログラマブルゲートアレイ(FPGA)を提供する。

【解決手段】フィールドプログラマブルゲートアレイ(FPGA)103であって、該FPGAは、該FPGA内の少なくとも1つの回路に対するプロセス、電圧、および温度の表示を提供するように適合された監視回路のセット115と、該少なくとも1つの回路に対するプロセス、電圧、および温度の該表示から該少なくとも1つの回路に対するボディバイアス値の範囲を導出するように適合されたコントローラ140と、該少なくとも1つの回路内の少なくとも1つのトランジスターにボディバイアス信号を提供するように適合されたボディバイアス生成器とを含み、該ボディバイアス信号は、該ボディバイアス値の範囲内の値を有する。

(もっと読む)

プログラマブル・ゲートアレイ部を備えたマスクプログラマブル論理装置

【課題】プログラマブルゲートアレイ部を備えるマスクプログラマブル論理装置を提供すること。

【解決手段】集積回路の基板上に配置される複数のマスク−プログラマブル領域と、上記マスク−プログラマブル領域に結合されると共に上記マスク−プログラマブル領域を相互接続するために基板上に配置される複数の相互接続導体と、基板上に配置される複数のゲートアレイ部とからなり、ゲートアレイ部はマスクプログラマブル論理装置上の回路設計の実行を促進する少なくとも一つの機能を達成するようにプログラム可能である集積回路上に配置されるマスク−プログラマブル論理装置。

(もっと読む)

自己修正可能な半導体、および自己修正可能な半導体を備えたシステム

【課題】歩留りの向上を実現できる、自己修正可能な半導体を提供する。

【解決手段】自己修正可能な半導体は、同じ機能を実行しかつ副機能ユニットを有する、多数の機能ユニットを備える。半導体は、完全または部分的な1つ以上のスペア機能ユニットを備え、当該スペア機能ユニットは、半導体へと集積される、副機能ユニットの欠陥が検出されると、その副機能ユニットは、切り替えられて、完全または部分的なスペア機能ユニットにおける副機能ユニットと、置き換えられる。この再構成は、副機能ユニットと関連付けられたスイッチング・デバイスによって実現される。欠陥のある機能ユニットや副機能ユニットは、組立後に電源を投入している最中に動作中に周期的に検出されてよく、および/又は手動で検出してもよい。

(もっと読む)

IC内のヒューズ・プログラミング電流を制御するためのシステムおよび方法

【課題】自動的に適切なプログラミング電流を決定して印加するためのシステムを提供する。

【解決手段】システムは、複数の測定ヒューズに複数の相違する電流を流し、複数の測定ヒューズの対応するものを破壊することなく切断した1つまたは複数の電流を特定し、特定された電流のうちの1つを自動的に選択するように構成されている測定回路と、選択された電流で1つまたは複数の目標ヒューズをプログラムするように構成されているプログラミング回路と、を具備する。

(もっと読む)

IC中のプログラム可能なヒューズの状態を決定するためのシステム及び方法

【課題】IC中のヒューズの状態又は設定を検出するためのシステム及び方法を提供する。

【解決手段】ヒューズ電圧を2つの基準電圧と比較することにより3つのヒューズ状態(未切断、切断、及び破壊)を判断するための方法を具備する。各ヒューズ状態は、異なるインピーダンスを有し、そしてヒューズ電圧に関係付けられる。ヒューズ電圧は、2つの基準電圧の下、間、又は上であり、それによってヒューズ状態を判断する。1つの実施形態は、読出しトランジスタ、同様に2つの基準電圧発生器と直列のヒューズを含み、各基準電圧発生器は抵抗器とトランジスタとを備える。両方のトランジスタのインピーダンスは、未切断ヒューズ・インピーダンスより大きく、そして1つは切断ヒューズ・インピーダンスより小さい。2つのコンパレータは、ヒューズ電圧を分類するために使用され、ヒューズが未切断、切断、又は破壊であるかを示す。

(もっと読む)

半導体装置

【課題】回路面積の増大を抑制し、かつ切断するヒューズの数を低減する。

【解決手段】複数の通常のヒューズと、通常ヒューズの出力と論理をとることで通常ヒューズにより記憶された情報を生成させるためのヒューズであって、N個(Nは2以上の自然数)の通常ヒューズに対して1つ設けられ、対応する通常ヒューズの切断に係る論理情報を示す論理情報ヒューズとを有し、多数の通常ヒューズが切断される場合には、論理情報ヒューズを切断して、元の論理では切断されない通常ヒューズを切断するように論理を反転させることで、回路面積をほとんど変えることなく、切断するヒューズの数を低減できるようにする。

(もっと読む)

電気ヒューズモジュール

【課題】書き換えの可能な電気ヒューズを最小回路で実現する。

【解決手段】一端が外部電源電圧端子に接続された2本の電気ヒューズと、前記2本の電気ヒューズの共通接続ノードと接地端子間に並列に接続されたプログラム制御用の2本のスイッチング素子および読出し用の2本のスイッチング素子と、前記第1の電気ヒューズとスイッチング素子の接続点の電圧を検知する検知回路と、前記第1の電気ヒューズと、第2の電気ヒューズの接続点の電圧レベルを受ける排他的論理和を備えており、複数の電気ヒューズを初段から順番に1つずつ電気ヒューズをプログラムするに際して、前段の電気ヒューズの状態を検知回路で検知し、前段の電気ヒューズがプログラムされている時だけ、次段の電気ヒューズをプログラムするかどうかを判断するので、1本のプログラム用外部制御端子からプログラムが必要な電気ヒューズの本数分の信号パルスを入れることでプログラムが実現する。

(もっと読む)

半導体集積回路

【課題】プログラミング後のヒューズ素子の読み出しの信頼性を向上できる半導体集積回路を提供する。

【解決手段】半導体集積回路は、プログラム用電圧ノードとラッチノードとの間に設けられた電気的にプログラム可能なヒューズ素子11と、前記ラッチノードの電圧をラッチするラッチ回路15と、前記ラッチ回路の動作電流の大きさを制御して、前記ヒューズ素子がプログラム済みか否かを判定する抵抗判別値を制御する電流源16とを具備する。

(もっと読む)

アーキテクチャを隠し、リバースエンジニアリングを防止し、デバイスを動作不能にするための、電気的にプログラム可能なヒューズの使用

【課題】 デバイスがデバイス製造者の制御を離れた後に、電子デバイスの特定の機能の作動及び/又は該電子デバイスの特定の機能へのアクセスを制御することができるようにする方法及びシステムを提供すること。

【解決手段】 デバイスが製造者の制御を離れた後に、電子デバイスの特定の機能の作動及び/又は該電子デバイスの特定の機能へのアクセスを制御することができる技術及びシステムが提供される。作動及び/又はアクセスは、電気的にプログラム可能なヒューズ(eFUSE)のような不揮発性記憶素子内に格納された値に基づいて提供することができる。

(もっと読む)

差異感知技術による低電圧プログラマブルeFUSE

【課題】 ノイズの影響をあまり受けない感知技術を組み入れ、従来設計よりも小さい回路リソースを要求する、単一の低電圧パルスによってプログラムすることができるeFuseを提供すること。

【解決手段】 集積回路のための差異感知技術を組み入れる低電圧プログラマブル電子ヒューズが開示される。プログラミング・ステップは約1.5倍のVddで実行され、一方、感知動作は、感知動作に起因する電子ヒューズ(xF[j])にわたる抵抗変動を制限するVddで実行される。基準ヒューズ(xF)及びプログラムされるヒューズ(xF[j])が直列に結合されるため、感知のために要求される電流の大きさがさらに2分の1に減少され、一方、プログラミングの間は、プログラムされたヒューズ(xF[j])のみがプログラミング電流を制限する。感知動作の間、ゲーティング・トランジスタ(mNR)は、そのままのヒューズの場合にはヒューズ選択トランジスタ(g[j])にわたる電圧低下をエミュレートする。電子ヒューズの抵抗を特徴付ける回路及び方法も開示される。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に搭載されるラッチ回路のソフトエラーレートを低減でき、救済情報等をラッチした場合にハードエラーと認識されるエラーの救済を可能とする。

【解決手段】不良アドレス等の情報を記憶した複数のフューズ素子10と、この複数のフューズ素子から並列に転送される複数の情報をラッチする複数の第1のラッチ回路11と、この複数の第1のラッチ回路から並列またはシリアルに転送される複数の情報をラッチする複数の第2のラッチ回路12と、これらの各ラッチ回路に入力する情報の転送を制御する転送制御回路13とを具備し、ラッチ回路にリフレッシュ機能を持たせている。

(もっと読む)

1 - 11 / 11

[ Back to top ]