Fターム[5J043AA21]の内容

Fターム[5J043AA21]の下位に属するFターム

周波数の調整、可変、切換 (118)

パルス幅の調整、可変、切換 (50)

Fターム[5J043AA21]に分類される特許

1 - 15 / 15

クロック発振回路及び半導体装置

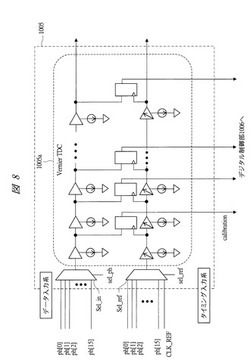

【課題】起動時にTDCにキャリブレーション処理を加えることで、時間分解能のばらつきが発生することを防ぎ、合わせて、遅延用の素子の冗長度を減らすことで回路規模の増大を防ぐ手段を提供する。

【解決手段】電源投入時等に多相発振器型TDCであるPDC_c及びバーニア型TDCであるPDC_fのキャリブレーションを実行する。キャリブレーション時にはPDC_fに入力するタイミング入力を参照クロックCLK_REFからDCCOの出力信号のうち一つを選択する。またデータは、先のDCCOの出力信号に隣接し、位相が進んだ出力信号とし、その間の遅延を導出する。これを全出力信号繰り返すことで、DCCOの出力信号1周期を導出する。

(もっと読む)

データラッチ回路およびそれを用いた試験装置

【課題】多様な信号形式のDUTからのデータを取り込み可能なデータラッチ回路を提供する。

【解決手段】データ入力端子INは、シリアル形式のデータ信号DINが入力される。n個(nは2以上の整数)のクロック入力端子CLK1〜CLKnは、それぞれにクロック信号CLK1〜CLKnが入力される。ある入力フリップフロップFFiは、データ信号DINを対応するクロック信号CLKiに応じたタイミングでラッチする。シリアルパラレル変換器SPiは、シリアル形式のデータ信号DINを対応するクロック信号CLKiを用いてパラレル形式の中間データ信号DINTiに変換する。データセレクタMUX1は、n個の中間データ信号DINT1〜nのうち選択信号SELに応じたひとつを選択する。

(もっと読む)

差動リング発振器型電圧制御発振器

【課題】 発振周波数の可変幅が大きい電圧制御発振器を実現する。

【解決手段】 リング発振器を差動インバータで構成し、テイル電流と負荷電流を制御する。

差動インバータの出力をPMOSトランジスタとNMOSトランジスタでスイッチングし、出力電圧をクリッピングトランジスタで制限する。

出力振幅を反転増幅回路によって与えられる周波数制御電圧に応じて変化させる。

(もっと読む)

可変駆動電圧により動作するオシレータ

【課題】安定した発振周期の信号を出力することができるオシレータを提供すること。

【解決手段】複数の論理素子がリング状に接続され、所定の周期の発振信号を出力する可変駆動電圧により動作するオシレータであって、複数の論理素子に選択的に印加される第1及び第2の駆動電圧を発生させる内部電圧発生手段を備え、発振信号の周期が正常状態である場合には、第1の駆動電圧が複数の論理素子に印加され、発振信号の周期が正常状態より短いか又は長い場合には、第2の駆動電圧VOSCが複数の論理素子に印加され、発振信号の周期が一定に維持されるように構成されている。

(もっと読む)

セルフテスト回路を有するクロック生成回路

【課題】クロックの位相のばらつきが許容範囲内か否かをチェックできるセルフテスト回路を有するクロック生成回路を提供する。

【解決手段】クロック生成回路は,基準クロックの位相に対して所定の位相差をそれぞれ有する複数のクロックを生成するクロック生成ユニット20と,動作テストのときに,複数のクロックのうち位相が隣接する1対のクロックの位相差をそれぞれ測定するセルフテスト回路BISTとを有する。そして,セルフテスト回路は,複数のクロックのうち1対のクロックを選択するクロック選択回路SELと,選択された1対のクロックの位相差に対応するパルス幅を有する位相差パルス信号UPを繰り返し生成する位相検出回路PFDと,位相差パルス信号のパルス幅に比例する周波数であって位相差パルス信号より低い周波数を有するテスト信号N2を生成するテスト信号生成回路と,基準期間内におけるテスト信号のパルス数をカウントし当該カウント値CNTを出力するカウンタ12とを有する。

(もっと読む)

PLL回路

【課題】回路や制御を複雑にすることなく、電圧制御発振回路の発振周波数レンジを広く保持しつつ出力クロックのジッターを低減可能なPLL回路を提供すること。

【解決手段】前段のLPF3から入力される制御電圧信号VCTRLの電位に応じた周波数を有する出力クロックを、制御端子に入力される制御電圧に応じて遅延時間が変化する遅延回路のM個を環状に接続したリングオシレータを用いて発生するVCO回路4aを備えるPLL回路において、VCO回路4aは、制御電圧信号VCTRLから低周波帯域の制御電圧信号VCTRLを抽出する低域通過フィルタを備え、前記リングオシレータは、前記M個の遅延回路のうち、m個(m<M)の各遅延回路の制御端子に制御電圧信号VCTRLが入力され、(M−m)個の各遅延回路の制御端子に制御電圧信号VCTRL2が入力される。

(もっと読む)

電圧制御発振回路

【課題】出力クロックのスキューを補正でき、不良率を低減できる電圧制御発振回路を提供する。

【解決手段】電圧制御発振回路14は、最終段の出力と最初段の入力とが接続されることによって環状に接続される複数段の遅延回路を備える第1リングオシレータ21と、最終段の出力と最初段の入力とが接続されることによって環状に接続される複数段の遅延回路を備える第2リングオシレータ22と、前記第1、第2リングオシレータにクロスカップル接続される一対の第1、第2反転回路23-1,23-2と、入力が前記第1リングオシレータの出力に接続される第3反転回路と、入力が前記第2リングオシレータの最終段の遅延回路の入力に接続される第4反転回路とを少なくとも備える第1位相合成回路25と、入力が前記第2リングオシレータの出力に接続される第5反転回路と、入力が前記第1リングオシレータの最終段の遅延回路の入力に接続される第6反転回路とを少なくとも備える第2位相合成回路26とを具備する。

(もっと読む)

半導体装置

【課題】遅延時間を高い精度で調整できるようにする。

【解決手段】従属接続された複数の反転出力の論理ゲートと、負荷容量としてMOSトランジスタの酸化膜容量を用いて制御信号に応じて負荷容量値を可変する負荷容量回路とを有し、反転出力の論理ゲートの出力端に負荷容量回路を接続するようにして、遅延時間をより微小に制御することを可能にし、遅延時間を高い精度で調整することができるようにする。

(もっと読む)

信号遅延回路およびこれを用いたパルス発生回路

【課題】高速信号に対し遅延時間を連続的に調整可能な信号遅延回路を提供すること。さらに、電源電圧が低い場合でも、遅延時間の変動を抑制できる回路を提供すること。

【解決手段】信号遅延回路1は、第1のインバータ回路101と、その出力端子に接続する第2のインバータ回路102と、第2のインバータ回路の出力端子からその入力端子に至る帰還回路105を備える。帰還回路の帰還量を制御することで、第1のインバータ回路の遅延時間を調整する。ここに、帰還回路はMOSトランジスタ106で構成し、MOSトランジスタのゲート電圧を制御することで遅延時間を調整する。また、電源電圧の変動に応じて帰還量を調整し、信号遅延回路の遅延時間の変動を抑制する。

(もっと読む)

発振安定化検出回路

【課題】発振信号の安定化時間が短い発振安定化検出回路を提供する。

【解決手段】本発明の発振安定化検出回路は、水晶振動子の発振により生成されたパルス形態の発振信号が印加されて、前記発振信号を分周して出力するTフリップフロップ50と、インバータ及びトランジスタを含み、前記Tフリップフロップから出力された信号をハイレベルから始まるパルス形態の信号に変換して出力するパルス制御部60と、前記パルス制御部から出力される信号により充電されるキャパシタと複数のトランジスタとを含み、バイアス電流の調節により前記キャパシタの充電時間を制御し、その充電時間が経過した後に前記発振信号の安定状態を表す安定信号をCPUに出力する発振安定化検出部70と、を含む。

(もっと読む)

水晶発振子のためのパルス整形回路

可変閾値の多段パルス整形回路を活用した、回路配置及び方法を用いて、水晶発振回路の信号出力をパルス整形する。パルス整形回路の各段は、ラッチの入力を駆動するシュミット・トリガを有し、該シュミット・トリガは水晶発振回路によって発生する歪んだパルスを拒否するために制御されるプログラム可能なトリップ・ポイントを有する。可変閾値の多段パルス整形回路は、例えば、ノイズおよび他の環境効果に対して強い電子回路のためのクロック信号の生成に用いることによって、電子回路におけるクロック関連のエラーの可能性を低減できる。  (もっと読む)

(もっと読む)

デュアルパスマルチモード順次記憶素子

本明細書では、デュアルパスマルチモード順次記憶素子(SSE)(10)が説明されている。一実施例では、デュアルパスマルチモードSSEは、第1(14)および第2(12)の順次記憶素子、データ入力、データ出力ならびに選択機構(16)を備えている。第1および第2の順次記憶素子(14、12)は、それぞれ、入力および出力を有する。データ入力は両方の順次記憶素子の入力に結合され、データを受け入れるように構成される。データ出力は両方の順次記憶素子の出力に結合され、データを出力するように構成される。選択機構(16)は、データ入力からのデータをデータ出力に渡すために、順次記憶素子のうちの1つを選択するように構成される。一実施例では、第1の順次記憶素子はパルストリガー式記憶素子(14)を備えており、第2の順次記憶素子はマスタースレーブ記憶素子(12)を備えている。  (もっと読む)

(もっと読む)

パルス発生回路

【課題】比較的簡易な構成で、パルス信号の立ち上がり時間、立ち下がり時間を制御し、かつ、短い繰り返し周期でパルス信号を発生すること。

【解決手段】制御信号供給部102は、間欠制御信号S1から、ベース端回路制御信号S12とエミッタ端回路制御信号S13を生成し、間欠動作回路103へ出力する。間欠動作回路103内のバイポーラトランジスタ304のベース端電圧が、ベース端回路制御信号S12により切り替えられて、ベース端回路制御信号S12がオンとなる時間だけコレクタ−エミッタ電流が急激に流れだし寄生容量のチャージ時間が短縮される。一方、エミッタ端回路制御用信号S13がオンとなる時間だけエミッタ電圧が切り替えられて、この間コレクタ−エミッタ電流が流れ、これに伴い回路電流が流れ出す。そして、回路電流に追従して、発信信号が増幅されて、出力端子306からパルス信号として出力される。

(もっと読む)

電源電圧制御装置

【課題】システムクロック周波数に応じて自由にクロック周期設定マージンを設定でき、システムクロック周波数の変化に対し、内部回路を誤動作させずに短時間で電源電圧を正常に動作する最小電源電圧に収束させること。

【解決手段】電源電圧制御装置100は、システムクロックを分周比1で分周する分周回路121、電圧制御発振回路110の出力を分周比2で分周する分周回路122、分周回路121と分周回路122のそれぞれの出力信号を位相比較/周波数比較する位相比較器/周波数比較器130、及びコントローラ145内にメモリ142を備え、システムクロック周波数に連動した動作モード信号に応じて、制御回路141によりそれぞれの分周回路121,122の分周比を設定する。また、システムクロック周波数が変化する時に、コントローラ145内のプリセット値を用いてアップダウンカウンタ143の初期設定とレジスタ設定を行う。

(もっと読む)

位相単独の予想可能な再設定の方法と装置

脳のオリーブ小脳ネットワークで発見される下オリーブ(IO)神経の振動力学が再現され、様々な制御アプリケーションに適用される。特徴のある振幅と周波数で準正弦波振動を生成するIO神経モデルが提供される。活動電位は振動のピークで発生し、正確なタイミング特性を有する。IO神経モデルに印加される刺激は、振動振幅と周波数の変化を示さず、振動位相のシフトを生じる、それゆえ活動電位の時間シフトを生じる。その結果として生じる位相は刺激の強さにより定義され、刺激がいつ印加されるかに依存せず、このように、自己参照位相再設定(SPR)の効果を提供する。結合された複数のIO神経、またはそのモデルは、振動位相クラスタの形態で空間と時間に組織される傾向がある。IO発振器の位相は、位相進化の過程にかかわりなく、所望の位相パターンに素早くセットされうる。IO神経モデルを実装する回路と、その回路に基づく制御システムが記載される。 (もっと読む)

1 - 15 / 15

[ Back to top ]