Fターム[5J043AA22]の内容

パルス発生器 (3,485) | 目的、効果 (1,186) | 出力の調整、可変、切換 (183) | 周波数の調整、可変、切換 (118)

Fターム[5J043AA22]に分類される特許

1 - 20 / 118

半導体装置

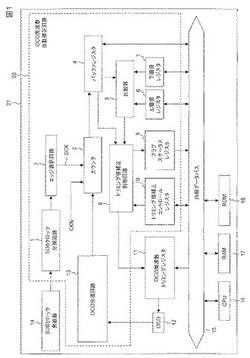

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

クロック信号生成装置およびクロック信号生成方法

【課題】クロック信号の精度を向上させる。

【解決手段】パルス信号S2を決められた数だけカウントする毎にクロック信号S3を生成する際に、2回の1秒信号S1の出力時点間におけるパルス信号S2の第1カウント数とパルス信号S2の周波数との差分値である第1の誤差を決められた数から増減する補正処理を実行する処理部31〜33を備え、処理部は、1秒信号S1の出力時点から1秒間に生成すべき数のクロック信号S3を生成する毎に出力する1秒完了信号S6の出力時点までの間におけるパルス信号S2の第2カウント数が第1規定値以下のときに第2カウント数を第2の誤差として特定し、第2カウント数が第1規定値よりも大きくかつ周波数の値および第1の誤差を合計した値と第2カウント数との差分値の絶対値が第1規定値以下のときにその差分値を第3の誤差として特定し、補正処理において第1〜第3の誤差の合計値を決められた数から増減する。

(もっと読む)

圧電発振器

【課題】安定駆動に達するまでの時間を短縮した圧電発振器を提供する。

【解決手段】本発明の水晶発振器(圧電発振器)50は、水晶振動子(圧電振動子)1と、水晶振動子1に接続されて発振ループを形成して発振信号を出力する水晶発振部(圧電発振部)24、及び水晶発振部24の起動時に自励発振する自励発振部25により構成された発振回路と、を備え、自励発振部25の周波数が水晶発振部24の周波数よりも高く設定されている。尚、自励発振部25は、複数のコンデンサー(容量素子)C、インバーター5及び抵抗素子4により構成され、複数のコンデンサーCの合成容量の値を調整するために、調整手段6を備えている。

(もっと読む)

PLL回路

【課題】特性の向上を図ることが可能なPLL回路を提供する。

【解決手段】PLL回路は、発振信号に基づいた充放電信号に応じて、充放電電流を出力端子に流すチャージポンプを備え、出力端子に一端が接続され、ローパスフィルタを構成する可変抵抗を備え、可変抵抗の他端に一端が接続され、接地に他端が接続され、ローパスフィルタを構成する容量を備え、前記チャージポンプ電圧を電流に変換した動作電流を出力する電圧電流変換器を備え、リング状に直列に接続された複数のインバータを有し、インバータを動作させるための動作電流が供給され、動作電流に応じて発振周波数が制御される発振信号を出力する電流制御発振器を備え、可変抵抗の他端のフィルタ電圧と、第1の基準電圧およびこの第1の基準電圧よりも高い第2の基準電圧とを比較する第1の比較回路を備え、その比較信号に基づいて、電流制御発振器のインバータの段数を制御する制御回路を備える。

(もっと読む)

半導体装置

【課題】広範囲、光分解能に周波数を可変することのできるクロック信号を生成する。

【解決手段】オペアンプAMP1は、正入力部と負入力部が等しい電圧となるようフィードバックがかかり、回路ノードfbckは、参照電圧VREFIに等しい電圧となる。デコーダDECは、制御信号CNT7,CNT6をデコードし、トランジスタT2〜T5のいずれか1つをオンさせる。この構成によって、回路ノードfbckが、参照電圧VREFIと同電位となるようフィードバック制御がかかるため、トランジスタT2〜T5のON抵抗を大幅に低減することができ、周波数精度の悪化を防止することができる。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

可変抵抗回路および発振回路

【課題】回路規模を比較的小さくすることができ且つ高精度な抵抗値調整が可能な可変抵抗回路を提供し、また、かかる可変抵抗回路を用いた比較的回路規模が小さく高精度な発振周波数を実現し得る発振回路を提供する。

【解決手段】

可変抵抗回路は、複数の抵抗素子からなる第1の直列抵抗回路と、制御信号に応じて第1の直列抵抗回路の所定のノードのうちの1つを選択的に第1の端子に接続せしめる第1のスイッチ部と、を有する第1の抵抗調整回路と、第2の端子に接続された複数の抵抗素子からなる第2の直列抵抗回路と、制御信号に応じて第1の直列抵抗回路を第2の直列抵抗回路の所定ノードのうちの1つに選択的に接続せしめる第2のスイッチ部と、を有する第2の抵抗調整回路と、を含む。

(もっと読む)

電圧制御可変容量及び電圧制御発振器

【課題】集積回路上に構成可能で、容量可変比率が大きくかつQ値が高く、VCOを構成した時に直線性の高い制御電圧と発振周波数の関係を実現する電圧可変型容量を提供すること。

【解決手段】下部電極を共通接続した複数のMOS型容量素子(CM1〜CMn)と、該複数のMOS型容量素子の上部電極に一端を接続し、他端を共通接続する同数の非電圧可変型容量(C1〜Cn)と、これらのMOS型容量素子と非電圧可変型容量の接続点に夫々異なる固定バイアス電圧を与える手段(VB1〜VBn及び抵抗)により構成され、前記複数のMOS型容量の共通接続された下部電極に制御電圧を加える。

(もっと読む)

局部発振器

【課題】PVTに依存しない安定した位相雑音特性を短時間で得ることができる局部発振器を提供する。

【解決手段】局部発振器は、デジタル制御発振器と、位相データ生成器と、減算器と、ループフィルタと、乗算器と、係数算出器と、を備える。前記デジタル制御発振器は、第1の発振器制御値により発振信号の発振周波数を制御可能である。前記発振周波数は、前記第1の発振器制御値と、前記第1の発振器制御値の単位値あたりの前記発振周波数の変化量と、の積に等しい。設定周波数データは、設定周波数を基準信号の基準周波数で除算して得られる。前記乗算器は、前記ループフィルタからの規格化制御値に第1の係数を乗算した前記第1の発振器制御値を出力する。前記係数算出器は、前記発振周波数が前記設定周波数に略等しくなった時の前記第1の発振器制御値を、前記設定周波数データで除算し、その除算結果を新たな前記第1の係数として前記乗算器に設定する。

(もっと読む)

同期回路

【課題】小面積で広帯域特性及び低位相雑音特性を得ることが可能な同期回路を提供する。

【解決手段】位相検出器11は、参照信号と帰還信号との位相差を検出する。電圧生成器12,13は、位相検出器の出力信号に基づき電圧を発生する。パルス発生器16は、参照信号に基づきパルス信号を生成する。電圧制御発振器14は、パルス信号に同期して、発振信号を発振する。分周器15は、電圧制御発振器からの信号を分周し、帰還信号を生成する。電圧制御発振器14は、電圧発生回路から供給される電圧レベルをシフトするレベルシフト回路14cと、電圧発生回路からの電圧とレベルシフト回路からのレベルシフトされた電圧により駆動される複数のインバータ回路14a、14bからなるリング発振器とにより構成され、インバータ回路の1つにパルス信号が供給される。

(もっと読む)

タイマ

【課題】タイマにおいて、簡易な構成を実現しつつ、実時間の計測精度をより向上させることにある。

【解決手段】次回の停止時間T11は、記憶部36に記憶される周波数(前回の周波数)と、周波数演算部31により演算された周波数(今回の周波数)との差分及び前回の停止時間に基づき算出される。従って、前回の周波数と、今回の周波数との差分が大きい場合、例えば、温度変化が大きい場合には、次回の停止時間が短く設定される。このため、周波数の差分が大きい場合には周波数の補正の頻度が上がる。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの同期を保ったまま、再生クロックの適切なジッタ量と適切なバースト応答時間とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aの駆動力は、CDR回路のバースト応答時間が仕様の範囲内で最大となるように予め設定される。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

半導体集積回路装置

【課題】リングオシレータ回路において、確実な発振動作を実現する。また、発振周波数の可変範囲の拡大を実現する。

【解決手段】例えば、リングオシレータ回路を複数段の差動増幅回路DAMP_Aで構成し、DAMP_Aの差動対(MN1およびMN2)の入力ノード(ITおよびIB)にそれぞれMOSトランジスタ(MN_LIM1およびMN_LIM2)を付加し、当該トランジスタのゲートをそれぞれ制御するゲート制御回路GCTL_T,GCTL_Bを設ける。GCTL_T,GCTL_Bは、モード3において、MN_LIM1,2を振幅制限用のリミッタ回路として機能させ、モード2において、当該リミッタ回路をオフに制御し、モード1において、当該リミッタ回路を利用して発振起動を行う。

(もっと読む)

パルス発生回路

【課題】極めて短いパルス幅のパルス電圧を発生するパルス発生回路を提供する。

【解決手段】パルス発生回路は、誘導エネルギーを蓄積するトランスと、トランスへの直流の供給経路と、供給経路を開閉するスイッチと、トランスの第1端と第2端とを自律的に短絡に近い状態にする補助回路と、トランスからのパルス電圧の出力経路と、直流を供給する直流電源と、直流電源からの直流の供給を安定させるキャパシタと、を備える。補助回路は、トランスに誘導起電力が発生してから短い時間が経過した後に第1端と第2端とを自律的に短絡に近い状態にする。補助回路は、短絡経路を流れる電流を直流電源へ回生する回生回路を備える。

(もっと読む)

可変周波数多相発振器

【課題】簡単なデューティサイクル制御と、広い周波数レンジと、簡単な周波数調整構成と、低消費電力を備え、集積回路に組み込まれ、且つ、その集積回路を複雑にすることのない多相出力を有する可変周波数多相発振器を提供する装置および方法を提供すること。

【解決手段】多相信号を供給するための可変周波数多相発振器が開示される。この可変周波数多相発振器は、相関器、複数の遅延セル、およびNOR回路を備える。上記相関器のそれぞれは、電流供給部、キャパシタ、コンパレータ、スイッチ、及び論理ユニットを備える。上記複数の遅延セルは、大きな周波数レンジの範囲内で相が相関性を有する多相信号を発生させる。上記多相信号の周波数とデューティサイクルは調整可能である。

(もっと読む)

伝送装置及び伝送信号のジッター抑圧方法

【課題】伝送装置の出力信号のジッターを抑制することを目的とする。

【解決手段】伝送装置は入力信号が入力しているか否かを検出する入力信号断検出部と、発振器と、前記入力信号断検出部により入力信号が入力していることが検出されたときには、前記発振器の発振周波数と、入力信号から抽出されるクロック信号を分周した分周信号の周波数との差の周波数がフィルタの通過帯域外となるように前記発振器の発振周波数を設定する周波数設定部とを備える。

(もっと読む)

半導体集積回路

【課題】広い周波数範囲で高調波電流成分を削減して高周波ノイズを低減することのできる半導体集積回路の提供を図る。

【解決手段】クロック信号CKに同期して動作する複数のデジタル回路11,12を含む半導体集積回路であって、前記各デジタル回路は、周波数が同じで位相が異なる第1および第2クロック信号CKa,CKbの一方を受け取り、前記第1および第2クロック信号の位相差は、m,nを自然数として、ほぼ[2m−1]/2nであるように構成する。

(もっと読む)

1 - 20 / 118

[ Back to top ]