Fターム[5J043DD06]の内容

Fターム[5J043DD06]に分類される特許

1 - 17 / 17

半導体装置

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

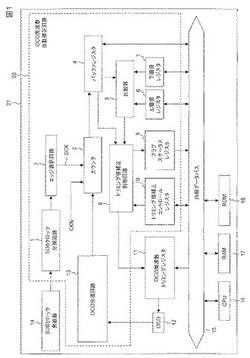

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

発振回路、発振装置およびクロックジェネレータ

【課題】消費電力を低減することができる発振回路を提供する。

【解決手段】入力信号が含むアナログ成分をデジタル信号に変換するアナログ/デジタル変換回路100と、アナログ/デジタル変換回路100で変換されたデジタル信号D1について、予め設定された周波数帯域成分のみを基準信号として通過させるバンドパスフィルタ101と、バンドパスフィルタ101を通過した基準信号D2と、PLLループ内に設けられる電圧制御発振器203からの出力信号D3との位相差が一定となるように電圧制御発振器203にフィードバック制御を行って発振させるPLL回路200とを備え、バンドパスフィルタ101は、所定の条件に基づいて、アナログ/デジタル変換回路100で変換されたデジタル信号D1の所定ビット幅について、「0」に固定するマスク処理を実行するマスク処理部102を備える。

(もっと読む)

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

デューティ比制御回路、デューティ比制御回路の制御方法、及びプログラム

【課題】小さな回路規模により発光素子の輝度を緩やかに変化させることを可能にする。

【解決手段】デューティ比制御回路は、デューティ比を変更することが可能なパルス信号の変更前のデューティ比である第1のデューティ比と、該パルス信号の変更後のデューティ比である第2のデューティ比とを保持する保持手段と、所定のパルス周期で前記パルス信号を生成するパルス生成回路と、前記パルス生成回路が生成する前記パルス信号のデューティ比を制御することにより、前記パルス生成回路の状態を、前記保持手段により保持された前記第1のデューティ比のパルス信号を生成する状態から、デューティ比の異なるパルス信号を生成する時間の比率を段階的に変化させる状態を経て、前記保持手段により保持された前記第2のデューティ比のパルス信号を生成する状態へ移行させるデューティ比制御手段と、を有する。

(もっと読む)

クロック発生装置およびクロック発生装置におけるジッタ低減方法

【課題】よりジッタの少ないクロック信号を発生させること。

【解決手段】周期信号を発生するDDS回路と、入力信号と基準信号とを比較して2値化信号を出力するコンパレータと、を有し、前記DDS回路において発生される前記周期信号に対し、前記基準信号との交差点における変化率を増加させる補正を行う変化率補正手段を備えることを特徴としている。

(もっと読む)

分周回路および電子機器

【課題】分周比を増やしても選択回路動作の高速化を維持する。

【解決手段】分周比に応じた一定周期の固定値をシフトレジスタ2の複数段のDフリップフロップの各前段にそれぞれデコーダ3から出力し、デコーダ3からの出力信号と前段のDフリップフロップからの出力信号から、最終段のDフリップフロップSFTCNT0からのロード信号LOADがハイレベルのときにデコーダ3からの出力信号にセレクタ40〜48により切り替える。複数段のDフリップフロップSFTCNT0〜8のうち最終段のフリップフロップSFTCNT0からの出力信号がハイレベルのときに、最終段のフリップフロップSFTCNT0からのQ出力をトグルフリップフロップ5から分周信号DIVOUTとして反転出力する。

(もっと読む)

シフトレジスタ回路

【課題】直並列変換器、複数の並列レジスタ、並直列変換器を含む構成のレジスタ回路において、消費電力の低減に好適な数の並列シフトレジスタを備えるレジスタを提供する。

【解決手段】本発明のシフトレジスタ回路は、n段構成のシフトレジスタとして機能するシフトレジスタ回路において、直列な入力データ信号を並列データに変換する直並列変換部と、並列データをシフトするデータシフト部と、データシフト部から出力される複数の出力を直列な出力データ信号に変換する並直列変換部と、を備え、直並列変換部及び並直列変換部は、n1段構成のシフトレジスタを含み、データシフト部はn1個の並列シフトレジスタを含み、n1は√(n/2)近傍の整数値に定められる、ことを特徴とする。

(もっと読む)

パルス生成装置

【課題】パルス信号の周期及びデューティ比を、相互に影響を与えることなく独自に設定可能にしたパルス生成装置を提供すること。

【解決手段】本発明にかかるパルス生成装置は、パルス周期を設定する信号を入力し、パルス周期を制御する周期制御信号を出力する周期設定手段11を備える。また、パルスのデューティ比を設定するデューティ比設定信号を入力するとともに、周期設定手段において設定されるパルス周期を含む信号を入力し、当該パルス周期とデューティ比設定信号に基づいて、パルスのデューティ比を制御するデューティ比制御信号を生成するデューティ比設定手段12を備える。さらに、周期制御信号とデューティ比制御信号に基づいて、設定された周期及びデューティ比を有するパルス信号を生成するPWM出力発生手段13を備えることを特徴とする。それにより、パルス周期に影響されることなくパルスのデューティ比を決定することが可能である。

(もっと読む)

パルス発生回路及びパルス発生回路を備えた電子機器

【課題】PVTに依存せずに安定した周波数を出力する。

【解決手段】出力する第1の出力信号Vf1の周波数を第1の制御電圧VC1で制御する第1の電圧制御発振器11と、第1の出力信号Vf1及び基準信号CLKに基づき第1の出力信号Vf1の周波数を一定に維持する第1の制御電圧VC1を生成する制御電圧生成部13と、を含む位相同期回路10と、出力する第2の出力信号Vf2の周波数を第2の制御電圧VC2で制御する第2の電圧制御発振器20と、第1の制御電圧VC1に基づき第2の出力信号Vf2の周波数を一定に維持する第2の制御電圧VC2を生成する制御電圧変換部30と、を含むパルス発生回路1。

(もっと読む)

クロック生成回路

【課題】電源電圧の変動等による出力クロックへの影響を低減する。

【解決手段】基準クロックを生成する自走発振器10と、この基準クロックに同期してカウントするカウンタを有し、外部より入力される入力クロックの周期毎のカウンタのカウント値を保持して並列出力するクロックカウンタ40と、クロックカウンタ40の出力値に応じたクロック周波数のシリアル信号を基準クロックに同期させて出力するクロック分周器70を備え、クロックカウンタ40とクロック分周器70との間に、クロックカウンタ40の出力値の瞬時的な変動を抑制するフィルタ60を備える。

(もっと読む)

発振回路及び半導体装置

【課題】本発明は、発振回路及び半導体装置に関し、電源投入後、リセット後、スタンバイ状態からの復帰後のMCUの処理の高速化と低消費電力化を両立することを目的とする。

【解決手段】第1の発振回路と、第1の発振回路より長い発振安定時間を有する第2の発振回路と、第2の発振回路の発振安定時間の経過を示す安定信号を出力する信号生成回路と、選択信号に基づいて第1及び第2の発振回路の出力の一方を選択出力するスイッチ回路と、抑止信号に基づいて第2の発振回路の起動を抑止する抑止回路とを備え、第1及び第2の発振回路が同時に起動されてスイッチ回路により第1の発振回路の出力が選択出力された後に第2の発振回路の出力に切り替えられるモードと、第1の発振回路が起動されて抑止回路により第2の発振回路が起動されずスイッチ回路により第1の発振回路の出力のみが選択出力されるモードを有するように構成する。

(もっと読む)

電圧制御発振器の位相雑音最適化方法および位相雑音最適化装置

【課題】電圧制御発振器から出力される発振信号の発振周波数にかかわらず電圧制御発振器の位相雑音を最適化する位相雑音最適化方法および位相雑音最適化装置を提供する。

【解決手段】電圧制御発振器の発振信号を平滑化した検出電圧値を生成する。電圧制御発振器から出力される発振信号の出力振幅と位相雑音との関係によって示される位相雑音が最適となる出力振幅に基づいて設定された基準電圧値の範囲と検出電圧値とを比較して、比較結果に応じた判定信号を出力する。判定信号に基づいて電圧制御発振器の電流源のスイッチの開/閉を制御する電流切り替え信号を生成して出力することで出力振幅が安定し、位相雑音が最適となる。

(もっと読む)

発振器

【課題】発振周波数変更機能を備えた発振器において、不揮発性メモリからデータを読み出す際に発振周波数が変更されることなく安定的に読み出すことができる。

【解決手段】LSIの外部に設けられた不揮発性メモリ15に、発振回路13から発振されるクロック信号の周波数を変更するための周波数設定値が記憶されており、その周波数設定値が、発振回路13から発振される初期設定された周波数のクロック信号によって読み出されると、ダミーレジスタ11に格納される。不揮発性メモリ15からデータが全て読み出されてロード動作完了信号が出力されると、ダミーレジスタ11から記憶レジスタ12へ周波数設定値が格納され、発振回路13の発振周波数が周波数設定値とされる。

(もっと読む)

半導体装置

【課題】第1の制御クロックに基づいて第1の制御を行う第1の制御部と、第2の制御クロックに基づいて第2の制御を行う第2の制御部とを有する半導体装置に関し、チップサイズの小型化が可能な半導体装置を提供することを目的とする。

【解決手段】本発明は、第1の制御クロックに基づいて第1の制御を行う第1の制御部と、第2の制御クロックに基づいて第2の制御を行う第2の制御部とを有する半導体装置であって、第1のクロックを生成する第1のクロック生成部と、第2のクロックを生成する第2のクロック生成部と、第1のクロック又は前記第2のクロックのいずれかを選択し、出力する選択部と、クロック選択部で選択されたクロックから第1の制御クロックを生成し、第1の制御部に供給するとともに、クロック選択部で選択されたクロックから第2の制御クロックを生成し、第2の制御部に供給する制御クロック生成部とを有することを特徴とする。

(もっと読む)

ワンショットパルス発生回路

【課題】 状況に応じて直ちにパルス幅を変えることができるワンショットパルス発生回路を提供する。

【解決手段】 レジスタ25にパルス信号OUTの立ち上がりのタイミングを設定し、レジスタ21,22には、このパルス信号OUTのそれぞれ異なる立ち下がりのタイミングを設定する。更に、レジスタ23には、レジスタ21,22のいずれを選択するかの選択信号を設定する。これにより、例えば、エンジン制御部40等の外部から与えられる状況が急変したときに、レジスタ23の選択信号を変更することで、出力部のレジスタ29〜31から出力されるパルス信号OUTのパルス幅を直ちに変えることができる。

(もっと読む)

クロック信号を生成する方法

本発明は、第1クロック信号(SFo)を使用して、受信信号(RS)内の基準イベント(EVT1)の特性を測定する段階と、前記第1クロック信号を使用して、受信信号(RS)内の第2イベント(EVT2、D0)の特性の変動を判定する段階と、前記第2イベントの特性の変動によって、前記測定値(NEVT1、NFC)を訂正する段階と、前記第1クロック信号を使用して、前記訂正する測定値(NFC)によって第2クロック信号(SFC)を生成する段階と、を具備するクロック信号を生成する方法に関する。非接触チップの送受信回路への応用。  (もっと読む)

(もっと読む)

半導体装置及び発振周波数補正方法

【課題】 本発明は、半導体装置の動作時の発振周波数の変動要因に対応できるとともに、特定の通信機能や通信相手を必要とすることなく、RC発振回路の発振周波数の補正が可能な半導体装置を提供することを目的とする。

【解決手段】 半導体装置は、第1の周期で発振する第1の発振信号を出力するRC発振器と、RC発振器の出力に結合され第1の発振信号の第1の周期の長さを第2の周期を有する第2の発振信号に基づき計測し、その計測値を出力する計測回路と、計測回路の出力とRC発振器の出力とに結合され計測値に応じた数で該第1の発振信号を分周する補正回路を含むことを特徴とする。

(もっと読む)

1 - 17 / 17

[ Back to top ]