Fターム[5J043GG00]の内容

パルス発生器 (3,485) | ヒステリシス回路要素、素子 (208)

Fターム[5J043GG00]の下位に属するFターム

比較回路 (37)

差動増幅器 (46)

ダイオード(電流ミラー回路のものを除く) (4)

フリップフロップ (12)

コンデンサ(周波数決定用を除く) (32)

電流ミラー回路 (15)

複数の比較器、差動増幅器(積分器を除く) (49)

Fターム[5J043GG00]に分類される特許

1 - 13 / 13

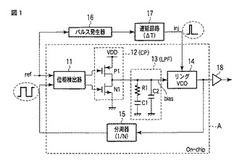

同期回路

【課題】小面積で広帯域特性及び低位相雑音特性を得ることが可能な同期回路を提供する。

【解決手段】位相検出器11は、参照信号と帰還信号との位相差を検出する。電圧生成器12,13は、位相検出器の出力信号に基づき電圧を発生する。パルス発生器16は、参照信号に基づきパルス信号を生成する。電圧制御発振器14は、パルス信号に同期して、発振信号を発振する。分周器15は、電圧制御発振器からの信号を分周し、帰還信号を生成する。電圧制御発振器14は、電圧発生回路から供給される電圧レベルをシフトするレベルシフト回路14cと、電圧発生回路からの電圧とレベルシフト回路からのレベルシフトされた電圧により駆動される複数のインバータ回路14a、14bからなるリング発振器とにより構成され、インバータ回路の1つにパルス信号が供給される。

(もっと読む)

シュミットトリガ型インバータ

【課題】さらに入力ノイズ耐性を有するシュミットトリガ型インバータを提供すること。

【解決手段】入力側ノードへの供給電圧が増加して第1の基準電圧に達するに従い出力側ノードから出る電圧が比較高電圧レベルから比較低電圧レベルに遷移し、入力側ノードへの供給電圧が減少して第1の基準電圧より低い第2の基準電圧まで減少するに従い出力側ノードから出る電圧が比較低電圧レベルから比較高電圧レベルに遷移するインバータと、インバータの入力側ノードに一方端が接続された第1の抵抗素子と、インバータの入力側ノードに一方端が接続された、該一方端の電圧が上昇するほどに抵抗値が減じる可変抵抗素子と、可変抵抗素子の他方端に一方端が接続された第2の抵抗素子と、ドレインが第2の抵抗素子の他方端に接続され、ゲートがインバータの出力側ノードに接続され、ソースが接地電位に接続されたnチャネルMOSトランジスタとを具備する。

(もっと読む)

ノイズ除去回路

【課題】少ない素子数のノイズ除去回路で、入力信号のノイズ除去を行う。

【解決手段】ノイズ除去回路30には、信号処理部1及びシュミットトリガ回路2が設けられる。信号処理部1には、2入力NOR回路NOR1、インバータINV1、Pch MOSトランジスタPT1、及びNch MOSトランジスタNT1が設けられ、クロック信号CLK及びイネーブル信号ENbを入力する。シュミットトリガ回路2には、インバータINV2、Pch MOSトランジスタPT2、Pch MOSトランジスタPT3、Nch MOSトランジスタNT2、及びNch MOSトランジスタNT3が設けられ、クロック信号CLK及び信号処理部1から出力される2つの信号を入力し、ノイズが除去されたクロック信号CLKを出力信号Soutとして出力する。

(もっと読む)

半導体集積回路装置

【課題】プロセス変動バラツキや外部環境の変化に影響されずに安定した発振周波数を出力する。

【解決手段】半導体集積回路装置30にはCR発振回路1及び基準電圧発生回路2が設けられる。CR発振回路1にはコンパレータCOMP1、コンデンサC1、インバータINV1、インバータINV2、及び抵抗R1が設けられる。コンデンサC1及び抵抗R1はCR発振手段として機能する。基準電圧発生回路2は電圧変動が少なく、且つ温度変化の少ない安定した基準電圧Vref1と基準電圧Vref1よりも高い基準電圧Vref2を生成し、CR発振回路1の発振出力信号が“High”レベルのときに基準電圧Vref2をコンパレータCOMP1の(+)の入力ポートに出力し、発振出力信号が“Low”レベルのときに基準電圧Vref1をコンパレータCOMP1の(+)の入力ポートに出力する。

(もっと読む)

周波数可変発振器及びそれを用いた通信回路

【課題】半導体装置における周波数可変発振器について、温度や電源電圧の変動や製造ばらつきによって生じる発振周波数の変動が大きいために、位相雑音と依存性のある制御電圧と発振周波数の変換比を小さくすることが困難であり、そのために位相雑音が大きい。

【解決手段】入力される制御電流ICNTの大きさに応じて遅延量が増減する遅延回路2a、2b、2c、2e、2fを複数段リング状に縦続接続して構成したリング発振器1に、入力された制御電圧VCNTをリング発振器の制御電流ICNTに変換する電圧電流変換回路3を接続して、電圧電流変換回路3の内部で温度と電源電圧とトランジスタのしきい値電圧のいずれかに依存した電流をICNTから増減することにより、発振周波数の変動を抑制し位相雑音の低減をする。

(もっと読む)

オシレータ回路及び半導体記憶装置

【課題】本発明は、閾値電圧Vthのばらつきによる容量特性のばらつきに影響されることなく、所定の周期の発振信号を生成可能なオシレータ回路を提供することを目的とする。

【解決手段】オシレータ回路は、容量と、容量の一端に電気的に結合可能な第1の定電流源と、容量の該一端に電気的に結合可能な第2の定電流源と、容量の該一端と第1及び第2の基準電位とに結合され、容量の該一端の電位と第1及び第2の基準電位との比較結果に応じて、第1の定電流源を容量の該一端に電気的に結合して容量を充電する第1の動作と第2の定電流源を容量の該一端に電気的に結合して容量を放電する第2の動作とを切り換える制御回路と、第1の動作と第2の動作との切り換えタイミングに応じてパルス信号を生成する回路を含む。

(もっと読む)

リング発振器

【課題】比較的簡単な構成で十分な発振周波数精度が得られるリング発振器を実現する。

【解決手段】複数の差動増幅回路(10A)がループ状に接続されてなるリング発振器において、各差動増幅回路(10A)は、第1及び第2のトランジスタ(111,112)からなる差動トランジスタ対(11)と、一端が第1及び第2のトランジスタ(111,112)の接続点に接続され、他端が第1の電圧ノードに接続された第1の抵抗(12)と、第1及び第2のトランジスタ(111,112)のそれぞれと第2の電圧ノードとの間に設けられた第2及び第3の抵抗(13,14)とを備えている。

(もっと読む)

広い周波数範囲にわたり安定した利得を有する電圧制御発振器

【課題】VCOにおいて広い周波数範囲にわたり安定した利得を与える装置及び方法を提供する。

【解決手段】VCOは、波形発生器を、周波数選択入力を有するバイアス発生器と共に用いる。周波数選択入力を用いて、バイアス発生器の出力電流及び/又は利得の量を調整する。バイアス発生器の出力電流は、波形発生器の出力の周波数を決定する。複数のバイアス及び波形の発生器を用いて、VCOの周波数範囲を拡大できる。PLLは、VCOの周波数選択入力を用いることにより様々な出力周波数のためにプログラムできる。

(もっと読む)

フィルタ較正

フィルタ(114、116)を較正することが開示される。フィルタ(114、116)は、較正中に発振器として再構成される。フィルタを再構成するスイッチ(sw1、sw2)および/または他の構成が使用されて、正のフィードバックループに対してフィルタの負のフィードバックループを再構成する。フィルタのコンポーネント(c1−c4)を調整して、所望のフィルタ特性に対応する発振を達成するために発振パラメータが次に測定される(106、300)。 (もっと読む)

リング発振器

【課題】 周波数を可変制御できるリング発振器において、回路パラメータ等のばらつきにより、高い発振周波数でのばらつきが顕著となる。

【解決手段】 高速パスを構成する増幅器22と低速パスを構成する増幅器24とからなる各増幅段20の遅延時間をインターポレータ28が増幅器22,24に供給する電流により制御し、多段接続された増幅段20からなるリング発振器の発振周波数を可変する。ここで、最大発振周波数のばらつき範囲の下限値が、発振周波数の目的可変範囲の上限値に応じた値となるように設定する。さらに、増幅段20相互間にRC回路からなるLPF26を挿入する。LPF26のカットオフ周波数は、最大発振周波数のばらつき範囲の下限値に応じて設定し、ばらつきが生じても、最大発振周波数は当該下限値近傍範囲内となるように高発振周波数を抑制する。

(もっと読む)

同調可能なリング発振器

位相ロックループ(PLL)回路などの通信システムにおいて、広く使用されている電圧制御発振器(VCO)のようなリング発振器で、入力周波数の範囲をロックするため、本発明は、粗同調回路網と微同調回路網とを有する1つ以上の遅延回路を有する同調可能なリング発振器を提供する。粗同調回路網は、粗同調入力の関数として、最小時間遅延または最大時間遅延の一方を設定するために使用される。微同調回路網は、微同調入力の関数として、最小時間遅延と最大時間遅延との間を調整するために使用される。  (もっと読む)

(もっと読む)

発振信号生成器及びその装置

【課題】

発振信号が歪んでしまうのを確実に回避することができるようにする。

【解決手段】

発振信号生成部P1の各遅延回路21においては、第1制御信号Sc1に応じた所定量の電流を供給する第1電流供給部P4を、電源電圧と差動対部P3との間に設けるようにしたことにより、この差動対部P3と第1及び第2伝送線L1、L2と可変抵抗部P6とを電源電圧からフローティングしたような状態にすることができる。この結果このフローティングしたような状態となっている部分に接続される電圧を調節することにより、発振信号Soの発振中心電圧を、遅延回路21の動作が線形領域から外れないように制御することができる。

(もっと読む)

スキュー制御を有するクロックジェネレータ

クロック発生をもたらすためのシステムおよび方法が開示される。一実施例によれば、構成可能でインシステムプログラマブルな、柔軟なスキュー制御アーキテクチャを含むクロックジェネレータチップが与えられる。クロックジェネレータチップはさらにプログラム可能な入力回路、プログラム可能な出力回路を与えることができ、JTAGバウンダリスキャンを可能にし得る。  (もっと読む)

(もっと読む)

1 - 13 / 13

[ Back to top ]