Fターム[5J043GG02]の内容

パルス発生器 (3,485) | ヒステリシス回路要素、素子 (208) | 差動増幅器 (46)

Fターム[5J043GG02]に分類される特許

1 - 20 / 46

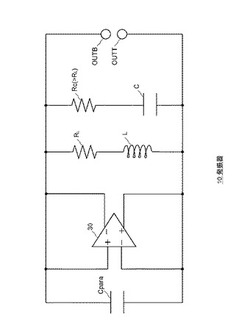

発振器及び半導体集積回路装置

【課題】発振器の出力端子間に直接寄生する容量Cparaの大きさが無視できない場合でも温度特性を補償する発振器及び発振器を内蔵する半導体集積回路装置を提供する。

【解決手段】インダクタンス素子Lと、容量素子Cと、増幅器30と、をそれぞれ第1の端子と第2の端子との間に並列に接続し、インダクタンス素子と容量素子とによって生じる共振を増幅器によって増幅し、第1の端子と第2の端子とから出力する発振器であって、第1の端子と第2の端子との間にインダクタンス素子の寄生抵抗RLより抵抗値の大きな第1の抵抗素子Rcが第1の端子と第2の端子との間に容量素子と直列に接続されている。

(もっと読む)

クロック発振回路及び半導体装置

【課題】起動時にTDCにキャリブレーション処理を加えることで、時間分解能のばらつきが発生することを防ぎ、合わせて、遅延用の素子の冗長度を減らすことで回路規模の増大を防ぐ手段を提供する。

【解決手段】電源投入時等に多相発振器型TDCであるPDC_c及びバーニア型TDCであるPDC_fのキャリブレーションを実行する。キャリブレーション時にはPDC_fに入力するタイミング入力を参照クロックCLK_REFからDCCOの出力信号のうち一つを選択する。またデータは、先のDCCOの出力信号に隣接し、位相が進んだ出力信号とし、その間の遅延を導出する。これを全出力信号繰り返すことで、DCCOの出力信号1周期を導出する。

(もっと読む)

電圧制御可変容量及び電圧制御発振器

【課題】集積回路上に構成可能で、容量可変比率が大きくかつQ値が高く、VCOを構成した時に直線性の高い制御電圧と発振周波数の関係を実現する電圧可変型容量を提供すること。

【解決手段】下部電極を共通接続した複数のMOS型容量素子(CM1〜CMn)と、該複数のMOS型容量素子の上部電極に一端を接続し、他端を共通接続する同数の非電圧可変型容量(C1〜Cn)と、これらのMOS型容量素子と非電圧可変型容量の接続点に夫々異なる固定バイアス電圧を与える手段(VB1〜VBn及び抵抗)により構成され、前記複数のMOS型容量の共通接続された下部電極に制御電圧を加える。

(もっと読む)

発振回路及びその動作電流制御方法

【課題】消費電力を低減する発振回路及びその動作電流制御方法を提供することを目的とする。

【解決手段】制御信号に応じてコンデンサC51,C12の充放電を切り替える充放電部M11〜M14と、コンデンサの電圧を基準電圧と比較して比較結果信号を出力するコンパレータ53,13と、比較結果信号でセット又はリセットされ、出力信号を制御信号として前記充放電部に供給すると共に発振信号として出力するフリップフロップ61と、コンデンサの電圧に応じてコンパレータの動作電流を制御する電流制御部16〜19と、を有する。

(もっと読む)

同期回路

【課題】小面積で広帯域特性及び低位相雑音特性を得ることが可能な同期回路を提供する。

【解決手段】位相検出器11は、参照信号と帰還信号との位相差を検出する。電圧生成器12,13は、位相検出器の出力信号に基づき電圧を発生する。パルス発生器16は、参照信号に基づきパルス信号を生成する。電圧制御発振器14は、パルス信号に同期して、発振信号を発振する。分周器15は、電圧制御発振器からの信号を分周し、帰還信号を生成する。電圧制御発振器14は、電圧発生回路から供給される電圧レベルをシフトするレベルシフト回路14cと、電圧発生回路からの電圧とレベルシフト回路からのレベルシフトされた電圧により駆動される複数のインバータ回路14a、14bからなるリング発振器とにより構成され、インバータ回路の1つにパルス信号が供給される。

(もっと読む)

PLL回路

【課題】ループフィルタの容量値を抑え、且つ動作を安定させることが可能なPLL回路を提供することを目的としている。

【解決手段】入力信号の位相と電圧制御発振回路の出力信号の位相とを比較し、位相差に応じた信号を出力する位相比較器と、前記位相比較器の出力信号に応じて充放電電流を生成するチャージポンプ回路と、前記チャージポンプ回路の出力を平滑し第一の制御電圧を生成するループフィルタと、前記ループフィルタから出力される前記第一の制御電圧を所定の電圧になるよう第二の制御電圧を生成する制御電圧生成回路と、を備え、前記第一の制御電圧と前記第二の制御電圧とが前記電圧制御発振回路に入力される。

(もっと読む)

パルス幅変調回路

【課題】レベルシフト回路を必要としない無安定バイブレータ回路を用いたパルス幅変調回路を提供する。

【解決手段】パルス幅変調回路1内のコンパレータCOMPaは上側のレベル変動範囲を決定する電圧Vcc,Va(<Vcc)で駆動され、コンパレータCOMPbは下側のレベル変動範囲を決定する電圧Vb,Vss(<Vb)で駆動される。コンデンサCaの一方端はスイッチ回路Swaにより電圧Vcc,Vaのいずれかに設定され、コンデンサCbの一方端はスイッチ回路Swbにより電圧Vb,Vssのいずれかに設定される。スイッチ回路SwaはコンパレータCOMPbの出力レベルが「Vb」のとき、コンデンサCaの一方端を電圧Vccに設定し、「Vss」のとき、電圧Vaに設定するように切り換えられる。スイッチ回路SwbはコンパレータCOMPaの出力レベルが「Vcc」のとき、コンデンサCbの一方端を電圧Vssに設定し、「Va」のとき、電圧Vbに設定する。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

半導体集積回路装置

【課題】リングオシレータ回路において、確実な発振動作を実現する。また、発振周波数の可変範囲の拡大を実現する。

【解決手段】例えば、リングオシレータ回路を複数段の差動増幅回路DAMP_Aで構成し、DAMP_Aの差動対(MN1およびMN2)の入力ノード(ITおよびIB)にそれぞれMOSトランジスタ(MN_LIM1およびMN_LIM2)を付加し、当該トランジスタのゲートをそれぞれ制御するゲート制御回路GCTL_T,GCTL_Bを設ける。GCTL_T,GCTL_Bは、モード3において、MN_LIM1,2を振幅制限用のリミッタ回路として機能させ、モード2において、当該リミッタ回路をオフに制御し、モード1において、当該リミッタ回路を利用して発振起動を行う。

(もっと読む)

差動リング発振器型電圧制御発振器

【課題】 発振周波数の可変幅が大きい電圧制御発振器を実現する。

【解決手段】 リング発振器を差動インバータで構成し、テイル電流と負荷電流を制御する。

差動インバータの出力をPMOSトランジスタとNMOSトランジスタでスイッチングし、出力電圧をクリッピングトランジスタで制限する。

出力振幅を反転増幅回路によって与えられる周波数制御電圧に応じて変化させる。

(もっと読む)

遅延回路及び電圧制御発振回路

【課題】電源ノイズにより遅延時間が影響を受けにくい遅延回路及び遅延回路を用いた電圧制御発振回路を提供する。

【解決手段】第1及び第2の電源端子と一対の差動信号入力端子と一対の差動信号出力端子とを備え、一対の差動信号入力端子から入力した信号を遅延させて一対の差動信号出力端子から出力する遅延部と、電流制御端子により制御された電源電流を遅延部の第1の電源端子と第2の電源端子との間に流すように制御する電流制御部と、第1及び第2の電源端子の電圧が一定の電圧になるように制御する電圧制御部と、を備える。

(もっと読む)

可変周波数多相発振器

【課題】簡単なデューティサイクル制御と、広い周波数レンジと、簡単な周波数調整構成と、低消費電力を備え、集積回路に組み込まれ、且つ、その集積回路を複雑にすることのない多相出力を有する可変周波数多相発振器を提供する装置および方法を提供すること。

【解決手段】多相信号を供給するための可変周波数多相発振器が開示される。この可変周波数多相発振器は、相関器、複数の遅延セル、およびNOR回路を備える。上記相関器のそれぞれは、電流供給部、キャパシタ、コンパレータ、スイッチ、及び論理ユニットを備える。上記複数の遅延セルは、大きな周波数レンジの範囲内で相が相関性を有する多相信号を発生させる。上記多相信号の周波数とデューティサイクルは調整可能である。

(もっと読む)

電圧制御発振回路

【課題】電圧制御発振回路の回路規模の増大を抑制する。

【解決手段】電圧制御発振回路は、発振信号を増幅する発振アンプ部32と、発振信号の発振周波数を制御するLC共振部33と、負性抵抗成分を有する負性抵抗部34と、を備える。LC共振部33は、ループ状に接続されたgmセル25,26と、ループ上のノードに一端が接続された容量28〜31と、を有し、gmセル25,26と容量28,29とに基づくインダクタンス値と、容量30,31の容量値と、に基づいて発振周波数を制御する。

(もっと読む)

2分周インジェクションロックリング発振器回路

【解決手段】周波数分周器は、複数のインジェクションロックリング発振器(ILRO)を含む。第1ILROは、クロスカップルされたNチャネルトランジスタの対、負荷抵抗の対、インテグレイトキャパシタ、及び電流注入回路を含む。各トランジスタのドレインは、他方のトランジスタのゲートに結合される。各負荷抵抗は、各トランジスタのドレインを回路電圧源に結合する。インテグレイトキャパシタは、各トランジスタのソースに結合する。電流注入回路は、第1周波数の発振入力信号に応答して、各トランジスタのソースから回路グランドへのパスを交互にオープン及びクローズする。これに応答して、各トランジスタのドレインの電圧状態は交互にラッチ及びトグルされて、2分周された発振信号の差動対が生成される。逆位相で駆動される第1及び第2ILROは、位相直交する2つの差動出力信号を生成する。 (もっと読む)

高周波信号生成回路

【課題】低電圧で広帯域の動作が可能であり、回路面積の縮小が可能な高周波信号生成回路を提供する。

【解決手段】信号発生回路13は、出力信号の周波数と同一の周波数の信号を発生する。遅延手段14は、複数の遅延回路17を有し、信号発生回路13により発生された信号を遅延する。選択手段15は、複数の遅延回路17の出力信号を選択する。合成手段19は、選択手段15により選択された信号を合成し、出力信号を出力する。制御手段12は、出力信号の波形形状を設定するデータ、及び出力信号の少なくとも振幅、位相及び周波数を設定する制御信号に基づき、選択手段15を制御する。

(もっと読む)

発振回路

【課題】コンデンサへの充放電及び差動対を使用した発振回路において、回路規模や消費電力の増大を抑制しつつ安定した発振を可能とする。

【解決手段】トランジスタM10は、トランジスタM1,M2からなる差動対に定電流i1を供給する。M1には直列に抵抗R1が接続され、M1とR1との接続点の電位VBがM2のゲートに印加される。一方、M1のゲートには、定電流i2を生じるトランジスタM4と抵抗R2及びコンデンサC1の並列接続体との接続点の電位VAが印加される。M4は、M2のオフ期間に定電流i2を供給し、オン期間に定電流の供給を停止する。抵抗R2,R1それぞれの抵抗値をr2,r1として、(r1・i1)=(r2・i2)を満たすように設定する。

(もっと読む)

電圧制御発振器

【課題】発振周波数のばらつきを抑えることができる電圧制御発振器を提供する。

【解決手段】本発明による電圧制御発振器は、直列に接続されたN(Nは2以上の整数)個の反転差動増幅器(9)を備えている。N個の反転差動増幅器(9)の各々は、所定の電圧値の定電圧(Vcn1)と制御電圧(Vcnt)とに応じて動作する。N個の反転差動増幅器(9)の各々の動作電流は、定電圧(Vcn1)に応じた電流と、制御電圧(Vcnt)に応じた電流とを加算した電流の値で直接定まる。

(もっと読む)

発振器

【課題】発振周波数が一定なパルス信号を出力可能な発振器を提供する。

【解決手段】コンデンサCの一方の電極に接続される第1スイッチ素子Q1の開閉状態と、コンデンサCの他方の電極に接続される第2スイッチ素子Q2の開閉状態とを、コンデンサCの充放電に応じて変化する端子間電圧に基づいて交互に切り替えて所定の周期を有するパルス信号を出力する発振器100は、第1スイッチ素子Q1の開閉状態を制御する制御信号を出力する制御信号出力部10と、第1スイッチ素子Q1の閉状態への移行に応じて、第1スイッチ素子Q1を閉状態にする制御信号の信号レベルを保持する閉信号レベル保持部11と、第2スイッチ素子Q2の閉状態への移行に応じて、第1スイッチ素子Q1を開状態にする制御信号の信号レベルを保持する開信号レベル保持部12と、を備える。

(もっと読む)

バッファ回路

【課題】可変容量ダイオードの最小サイズに制限を有する半導体集積化プロセスによる複数のバッファ回路を用いたVCOにおいて、制御電圧の変化に対する発振周波数の変化を必要に応じて小さくできるようにしたバッファ回路を提供すること。

【解決手段】カスコード接続されたトランジスタQ1〜Q4とL1、L2 インダクタL1、L2により形成されているバッファ回路において、時定数回路素子を構成する可変容量ダイオードD1、D2をトランジスタQ3、Q4のソース端子側に接続したもの。基本動作上でトランジスタQ3、Q4のソース端子の電圧変動が小さくなるので、電圧制御端子Vcont1に印加する電圧を変化させたときの可変容量ダイオードD1、D2による静電容量の変化が小さくなる。制御電圧の変化に対して静電容量の変化が小さくなれば、VCOに適用したときに制御電圧の変化に対する発振周波数の変化が抑制され、安定度が向上する。

(もっと読む)

高周波発振形近接センサ

【課題】金属製の外装に収容しても検出対象物(鉄およびアルミ)に対して実用的な検出距離を有する近接センサを提供する。

【解決手段】検出用コイル10とコンデンサ6と非線形増幅器12とを含む発振回路5を有し、導電性を有する検出対象物7の近接に伴って生じる検出用コイル10のQ値の変化によって検出対象物7の有無または/および距離を検出する近接センサ4において、比透磁率が実質的に1であり、かつ、20℃での体積抵抗率が45×10-8(Ω・m)以上の金属からなるステンレスカバー1が検出用コイル10と検出対象物7との間に配置されており、検出対象物7が検出用コイル10に近接したときに、検出対象物7が強磁性体の場合には検出対象物7が無いときよりもQ値が減少し、検出対象物7が非磁性体の場合には検出対象物7が無いときよりもQ値が増加するように発振回路5の発振周波数を設定する。

(もっと読む)

1 - 20 / 46

[ Back to top ]