Fターム[5J049CA00]の内容

パルス列発生器 (633) | ランダムパルス (111)

Fターム[5J049CA00]の下位に属するFターム

出現確率分布の設定 (6)

周期性の低減 (36)

複数出力の同時発生 (5)

スクランブル、デスクランブル (9)

高速化 (13)

M系列符号の利用 (13)

アナログ雑音の利用 (11)

異なる周期と発生系列を持つもの (13)

Fターム[5J049CA00]に分類される特許

1 - 5 / 5

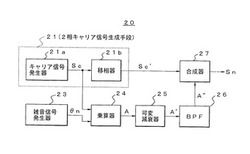

信号発生装置

【課題】所望の位相雑音が付加された信号を簡易な構成で生成できるようにする。

【解決手段】2相キャリア信号生成手段21により90゜位相が異なる2相のキャリア信号Sc、Sc′を生成し、その一方Scと雑音信号発生器23から出力される雑音信号θnとを乗算器24に入力し、その乗算器24の出力信号Aの大きさを可変減衰器25で調整しBPF26で帯域制限して、他方のキャリア信号Sc′とともに合成器27に与えて加算合成または減算合成する。この構成で、雑音信号θnの振幅がキャリア信号Scの振幅に対して十分小さければ、振幅雑音が極めて少なく、雑音信号θnに対応した位相雑音が含まれた信号Snを合成器27から出力することができる。

(もっと読む)

乱数発生回路

【課題】ランダム性が高く質のよい乱数を生成可能な乱数発生回路を提供する。

【解決手段】乱数発生回路は、リング発振器2と、基準クロック信号CK0を遅延させて遅延基準クロック信号CK1を生成する遅延制御回路3と、リング発振器2で生成された発振信号を遅延基準クロック信号CK1でラッチする第1のフリップフロップ4と、第1のフリップフロップ4の出力論理を均一化する第1のExOR回路5と、リング発振器2で生成された発振信号を遅延させる遅延回路6と、遅延回路6で遅延された発振信号を遅延基準クロック信号CK1でラッチする第2のフリップフロップ7と、第2のフリップフロップ7の出力論理を均一化する第2のExOR回路8と、第1および第2のExOR回路5,8の出力信号と基準クロック信号CK0とに基づいてランダムシリアルデータを生成する線形帰還レジスタ9とを備えている。

(もっと読む)

ランダムシーケンス発生器

ランダムなシーケンスのビット列を生成する機器(10)が開示される。その機器は、雑音信号でバイアスされたとき、ランダムなシーケンスのビット列を生成する発振手段(13)を有する。その発振手段は、負荷による干渉信号から保護されている少なくとも1つの発振器増幅器と、高い雑音干渉比を提供するテール電流源とを有する。さらに、本発明は、本発明に従うランダムなシーケンスを生成する機器を有する集積回路や電子装置に関するものである。  (もっと読む)

(もっと読む)

乱数発生装置及び乱数発生方法

【課題】読み出し毎に同じ乱数を得、0と1の出現割合の偏りを低減させ、かつ、製造コストを低くする。

【解決手段】1つの電気素子103が或る閾値以上の電気的ストレスを受けると絶縁状態から絶縁破壊状態に変化する。供給手段101が電気素子が絶縁状態を維持する確率と絶縁破壊状態になる確率とが同程度になる第1の電気的ストレス、又は、電気素子の絶縁状態を検出するための第2の電気的ストレスを電気素子に供給する。制御手段102、106が第1又は第2の電気的ストレスのうちのいずれか一方を電気素子に供給するように制御する。読出手段104が第1の電気的ストレスが電気素子に印加された後、第2の電気ストレスが電気素子に印加された場合に、電気素子が絶縁状態にあるか若しくは絶縁破壊状態にあるかを読み出す。対応付け手段105が電気素子が絶縁状態にあるか否かに基づいて、0又は1のデジタルデータを対応付ける。

(もっと読む)

ランダムビットストリームを提供するための装置

クロック信号(310)を提供するための第1の手段(302)と、サンプル信号(314)を提供するための第2の手段(306)と、サンプル信号(314)のサンプリングエッジがクロック信号のエッジに整列するように、第1および第2の手段(302・306)を起動するための第3の手段(322)と、を備える、ランダムビットストリームを提供するための装置は、サンプル信号(314)のサンプリングエッジに応答してクロック信号(310)をサンプリングし、サンプリング結果に応じてランダムビット(316)を生成するための第4の手段(308)をさらに備えている。また、この装置は、第1および第2手段(302・306)を停止するための第5手段(328)をさらに備えている。逐次的なランダムビット(316)は、ランダムビットストリームを生成する。  (もっと読む)

(もっと読む)

1 - 5 / 5

[ Back to top ]