Fターム[5J055DX74]の内容

電子的スイッチ (55,123) | 出力部 (8,827) | 慣用的な複合スイッチ (1,758) | 逆並列 (51)

Fターム[5J055DX74]に分類される特許

1 - 20 / 51

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

半導体装置、およびそれを用いた超音波診断装置

【課題】良好な線形性を有し、かつ電力損失の少ない双方向アナログスイッチの半導体装置を提供する。また、検出精度の高い超音波診断装置を提供する。

【解決手段】双方向にオンまたはオフ可能なスイッチ回路と、前記スイッチ回路の駆動回路を内蔵した双方向アナログスイッチの半導体装置であって、前記駆動回路は第一および第二の電源に接続され、前記第一の電源電圧は、前記スイッチ回路の入出力端子に印加される信号の最大電圧値以上であり、前記第二の電源電圧は、前記スイッチ回路の入出力端子に印加される信号の最小電圧値以下であり、さらに前記駆動回路は前記第一の電源と前記スイッチ回路との間に、直列に接続されたツェナダイオードとP型MOSFETを備えている。また、超音波診断装置であって、前記半導体装置を備える。

(もっと読む)

電力合成回路

【課題】 2つのパルス信号を増幅して合成するときの出力波形の乱れを低減することが可能な電力合成回路を提供する。

【解決手段】 入力端子11〜13と、第1の入力端子に接続される第1の増幅器15と、第2の入力端子12に接続される第2の増幅器16と、ソース端子およびドレイン端子の一方ならびにゲート端子が第1の増幅器15に接続される第1のトランジスタ17と、ソース端子およびドレイン端子の一方ならびにゲート端子が第2の増幅器16に接続される第2のトランジスタ18と、第1および第2のトランジスタ17,18におけるソース端子およびドレイン端子の他方がソース端子およびドレイン端子の一方に接続されるとともに、第3の入力端子13がゲート端子に接続される第3のトランジスタ19と、第3のトランジスタ19におけるソース端子およびドレイン端子の他方が接続される出力端子14とを備える電力合成回路とする。

(もっと読む)

半導体集積回路

【課題】消費電力を削減するために、クロック反転信号を用いることなくクロック信号に同期してデータの転送および保持を行わせる。

【解決手段】記憶ノードM、MBを持つ状態保持回路F11において、Pチャンネル電界効果トランジスタM1、M2のゲートおよびNチャンネル電界効果トランジスタM3、M4のゲートにはクロック信号CKを入力し、Pチャンネル電界効果トランジスタM1を介してデータ反転信号DBを記憶ノードMBに印加させ、Pチャンネル電界効果トランジスタM2を介してデータ信号DBBを記憶ノードMに印加させ、Nチャンネル電界効果トランジスタM3を介して出力信号Q1を記憶ノードSに印加させ、Nチャンネル電界効果トランジスタM4を介して出力反転信号QB1を記憶ノードSBに印加させる。

(もっと読む)

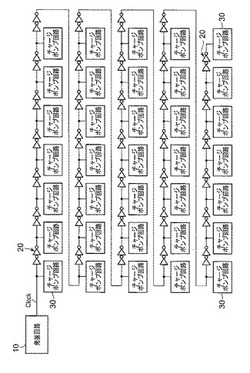

スイッチングボックス回路、スイッチングブロック回路、およびFPGA回路

【課題】高集積化および低消費電力化を可能にする。

【解決手段】第1乃至第4の方向にそれぞれ設けられた第1乃至第n(≧1)の信号線と、前記第1乃至第4の方向にそれぞれ設けられた第1乃至第nの入出力部であって、各方向における第i(1≦i≦n)の入出力部は、一端が対応する方向の第iの信号線に接続する第1乃至第nの入出力部と、第1乃至第2nの接続端子と、前記第1乃至第4の方向にそれぞれ設けられ、各方向において前記第1乃至第nの入出力部のそれぞれと、前記第1乃至第2nの接続端子のそれぞれを接続するためにそれらの間に1個ずつ設けられ、ゲートにクロック信号を受ける2n2個のスピンMOSFETと、を備えている。

(もっと読む)

アナログスイッチ回路

【課題】入力信号電圧が変化する場合にも、オン抵抗の変動によって入力信号波形に生ずる歪みを低減し、入力連続信号の広い周波数帯域に渡ってオン抵抗を一定に保つことができるアナログスイッチ回路を提供することを課題とする。

【解決手段】ソースが第1のスイッチ端子に接続され、ドレインが第2のスイッチ端子に接続される第1の電界効果トランジスタ(MN)と、電荷を充電するための第1の容量(CP)と、電荷を充電するための第2の容量(CA)と、直流電圧ノードと基準電位ノードとの間に第1の容量を接続するための第1のスイッチ回路(S1HP,S1LP)と、第1の容量及び第2の容量を並列に接続するための第2のスイッチ回路(S1HS,S1LS)と、第1の電界効果トランジスタのゲートとソースとの間に第2の容量を接続するための第3のスイッチ回路(S2HS,S2LS)とを有するアナログスイッチ回路が提供される。

(もっと読む)

プログラマブル配線の電源を安全にオンする方法および装置

【課題】プログラマブル配線を安全、単純かつスケーラブルな方法で電源をオンする、より良い方法およびデバイスを提供する。

【解決手段】プログラマブル配線のロード線を交差するプログラマブル配線の複数のドライバ線に接続する方法および装置であって、プログラマブル配線のロード線を交差する関連のドライバ線に接続するよう操作可能である接続セルを有し、この接続セルは、接続信号を受け取るために設けられた接続信号受け取り手段と、アクティベーション信号を受け取るために設けられたアクティベーション信号受け取り手段とを備える。さらに、プログラマブル配線のロード線を、プログラマブル配線の交差する関連のドライバ線に接続するために設けられた接続手段、一連のセルの次のセルへアクティベーション信号を伝播するアクティベーション信号伝播手段を備える。

(もっと読む)

サンプルホールド回路、ドライバ、電気光学装置、及び電子機器

【課題】演算増幅器の電源ラインの電位を安定化させる。

【解決手段】サンプルホールド回路は、演算増幅器OP1と、演算増幅器の出力端子と第1の入力端子のノードであるサミングノードNEGとの間に設けられた帰還用スイッチ素子SFと、帰還用スイッチ素子のオン・オフを制御するスイッチ信号生成回路80を含む。スイッチ信号生成回路を構成するN型トランジスタは第1のP型ウェルPW1に、スイッチ信号生成回路を構成するP型トランジスタは第1のN型ウェルNW1に、第1のP型ウェル及び第1のN型ウェルは第1のディープN型ウェルDNW1にそれぞれ形成される。演算増幅器のN型トランジスタは第2のP型ウェルPW2に、演算増幅器のP型トランジスタは第2のN型ウェルNW2に、第2のP型ウェル及び第2のN型ウェルは、第1のディープN型ウェルと分離された第2のディープN型ウェルDNW2にそれぞれ形成される。

(もっと読む)

サンプルホールド回路、ドライバ、電気光学装置、及び電子機器

【課題】回路の大規模化を抑えながら適正な位相補償を実現する。

【解決手段】演算増幅器OP1と、サンプルホールド回路の入力ノードNIと、接続ノードNSとの間に設けられたサンプリング用スイッチ素子SSと、接続ノードと、演算増幅器の第1の入力端子のノードであるサミングノードNEGとの間に設けられたサンプリング用キャパシタCSと、演算増幅器の出力端子とサミングノードとの間に設けられた帰還用スイッチ素子SFと、接続ノードと、演算増幅器の出力端子との間に設けられたフリップアラウンド用スイッチ素子SAと、サンプリング用キャパシタのサミングノード側の端子NCと演算増幅器の出力端子との間に設けられた位相補償用抵抗素子RPと、を含む。

(もっと読む)

リレー駆動装置

【課題】低コストで確実に同時オンを防止できる、リレー駆動装置における同時オン防止回路を提供すること。

【解決手段】2つの半導体リレー(一方向通電駆動型リレー)1,2が互いに逆方向となるように接続された両接続点に、それぞれ、制御部(駆動制御手段)3からのパルス制御信号が入力されるNANDゲート素子(第1および第2のロジック素子)6a、6bの出力端子が接続され、NANDゲート素子(第1および第2のロジック素子)6a、6bは、それぞれ、一方がハイレベルの時他方がローレベルとなる駆動出力信号を出力するように制御部(駆動制御手段)3で制御される。

(もっと読む)

分周器ユニットの同期化のための方法及び装置

【解決手段】一つまたはそれ以上の分周器ユニットの位相を同期させる方法装置は、参照信号を供給するためにマスター分周器ユニットをパワーオンすることを備える。スレーブ分周器ユニットの位相は、スレーブ分周器ユニットにパワーオンパルスを供給することと、デジタル制御発振器を用いて、参照信号にスレーブ分周器ユニットの位相を同期させることと、及びパワーオンパルスの立ち上がりエッジの後の第1の所定の遅延期間の後、スレーブ分周器ユニットをパワーオンすることにより、マスター分周器ユニットからの参照信号に同期される。スレーブ分周器ユニットをマスター分周器ユニットからの参照信号に同期させることで、任意の数のスレーブ分周器ユニットがパワーオンされ、互いに同相とされ得る。 (もっと読む)

マルチプレクサ

【課題】マルチプレクサの出力信号波形の歪みを低減する。また、大型化を抑制する。

【解決手段】マルチプレクサ1は、第1の容量素子を介して第1の入力信号を受けるCMOSスイッチ101と、第2の容量素子を介して第2の入力信号を受けるCMOSスイッチ102と、クランプ回路30と、クランプ回路40と、を備える。クランプ回路30は、CMOSスイッチ101を導通させる場合には、第1の入力信号に同期してVclp1で第1の入力信号をクランプし、CMOSスイッチ102を導通させる場合には、第2の入力信号に同期してVclp1で第2の入力信号をクランプする。クランプ回路40は、CMOSスイッチ101を導通させる場合には、第2の入力信号を検出しつつ検出された第2の入力信号をVclp2に近づけるようクランプし、CMOSスイッチ102を導通させる場合には、第1の入力信号を検出しつつ検出された第1の入力信号をVclp2に近づけるようクランプする。

(もっと読む)

出力回路、出力方法、および電子機器

【課題】 簡易な構造を有する出力回路等を提供する。

【解決手段】 出力回路(14)は、ゲートを有する出力トランジスタ(OD)と、画素データ(LT)に応じて、第1のストローブ信号(STB)の波形をゲートに伝えるスイッチング素子(42)と、を備える。出力回路(14)は、第2のストローブ信号(XSTB)を入力し、第2のストローブ信号に基づく第3のストローブ信号(STB)を生成する信号生成回路(44)を、さらに備えることができる。第3のストローブ信号(STB)の立ち上がり時間(72)は、第2のストローブ信号(XSTB)の立ち上がり時間より長く、かつ/または、第3のストローブ信号(STB)の立ち下がり時間(74)は、第2のストローブ信号(XSTB)の立ち下がり時間より長い。スイッチング素子(42)は、画素データ(LT)に応じて、第3のストローブ信号(STB)の波形をゲートに伝えることができる。

(もっと読む)

アナログスイッチおよびそれを用いたセレクタ回路

【課題】アナログスイッチの歪みを低減する。

【解決手段】入力端子P1にはアナログ信号INが入力される。出力端子P2からアナログ信号OUTが出力される。第1トランジスタM1はNチャンネルのMOSFETであって、入力端子P1と出力端子P2の間に設けられる。第1ダイオードD1は、第1トランジスタM1のゲートと第1固定電圧端子P3の間に、カソードがゲート側となる向きで配置し、ゲートをハイインピーダンス状態とする。

(もっと読む)

アナログスイッチおよびそれを用いたセレクタ回路

【課題】アナログスイッチの歪みを低減する。

【解決手段】入力端子P1にはアナログ信号INが入力される。出力端子P2からは、アナログ信号OUTが出力される。第1トランジスタM1はNチャンネルのMOSFETであって、入力端子P1と出力端子P2の間に設けられる。第1抵抗R1は、第1トランジスタM1のゲートと第1固定電圧端子(電源端子)P3の間に設けられ、第1トランジスタM1のゲートをハイインピーダンス状態とする。

(もっと読む)

デュアルレールセレクタ回路

【課題】 故障の有無を容易に認識し、故障時には、これを修復する。

【解決手段】 論理信号A,Bの一方を選択する正論理ゲート回路10の出力と、その反転信号Aバー,Bバーの一方を選択する負論理ゲート回路20の出力とが一致するか否かをXOR回路30で判定する。判定結果Fが1であれば正常、0であれば故障と認識できる。正常時には、選択回路40はインバータ11経由の信号を出力し、選択回路50はインバータ21経由の信号を出力する。判定結果が故障を示したときには、種々の論理パターンを入力として与えたときの出力パターンを解析し、ゲート回路10,20のいずれが故障したかを認識する。ゲート回路10の故障時には、選択回路40がインバータ22経由の信号を選択するように切り換え、ゲート回路20の故障時には、選択回路50がインバータ12経由の信号を選択するように切り換える。

(もっと読む)

半導体集積回路

【課題】電源の立ち上げ時に、迅速かつ確実に内部信号ノードの初期値を設定することができる半導体集積回路を提供すること。

【解決手段】入力信号を保持して出力するように構成された半導体集積回路において、前記入力信号が保持される信号ノードNDと電源VDDまたはグランドGNDとの間に、前記信号ノードNDの初期値を設定するための回路素子として、p型MOSトランジスタP2またはn型MOSトランジスタN2を選択的に接続する。この構成によれば、p型MOSトランジスタP2またはn型MOSトランジスタN2により信号ノードNDの信号レベルが電源VDDまたはグランドGNDに追従するため、この信号ノードNDの初期値が電源VDDまたはグランドGNDの何れかに対応した信号レベルに設定される。

(もっと読む)

半導体装置、電気光学装置及び電子機器

【課題】EMIノイズの低減を図れる半導体装置、電気光学装置及び電子機器等の提供。

【解決手段】半導体装置90は、ソース回路100と制御回路300を含む。ソース回路100は、複数のオペアンプOP1〜OP25と、各トランスミッションゲートの一端が対応するソース線に接続される複数のトランスミッションゲートTG1〜TG25と、スイッチ制御信号を出力するバッファ回路BF1A〜BF12Aを含む。各バッファ回路によりオン・オフされるトランスミッションゲートの個数をnとし、各トランスミッションゲートを構成するMOSFETのゲート幅、ゲート長をWb、Lbとし、各バッファ回路を構成するMOSFETのゲート幅、ゲート長をWa、Laとし、Kを定数とした場合に、n×Wb×Lb≧K×(Wa/La)の関係が成り立つ。

(もっと読む)

マルチプレクサ回路

【課題】信号経路に応じて信号伝搬遅延時間を選択できる再構成可能集積回路に用いて好適なマルチプレサ回路を提供する。

【解決手段】マルチプレクサ回路は、第一のマルチプレクサ回路と、第二のマルチプレクサ回路と、第一のマルチプレクサ回路と第二のマルチプレクサ回路のどちらかの出力信号を選択して出力する選択回路を有し、第一のマルチプレクサ回路と第二のマルチプレクサ回路のそれぞれの複数の制御信号のうち、少なくとも一つの制御信号を共有する。再構成可能集積回路のロジックブロックにより回路構成する場合にロジックエレメント回路間において、通常速度の信号と高速な信号の選択的出力を可能にし、面積の小さな再構成可能集積回路とするためのマルチプレクサ回路を提供する。第二のマルチプレクサ回路は、前記第一のマルチプレクサ回路とは信号伝搬遅延時間が異なる。

(もっと読む)

アナログスイッチ

【課題】アナログスイッチのオフ時のリーク電流を減らすことである。

【解決手段】アナログスイッチ31の第1の入力端子T1と第1の出力端子T2との間にnチャネルMOSトランジスタTR31が接続され、第1の入力端子T1と第2の出力端子T4との間にnチャネルMOSトランジスタTR32が接続されている。また、第2の入力端子T3と第2の出力端子との間にnチャネルMOSトランジスタTR33が接続され、第2の入力端子T3と第1の出力端子T2とのnチャネルMOSトランジスタTR34が接続されている。MOSトランジスタTR32とTR34のゲートは接地されている。

(もっと読む)

1 - 20 / 51

[ Back to top ]