Fターム[5J055FX09]の内容

電子的スイッチ (55,123) | 制御、帰還信号の発生 (8,841) | 帰還に用いられる素子、センサ等 (193) | モニター用トランジスタ (47)

Fターム[5J055FX09]に分類される特許

1 - 20 / 47

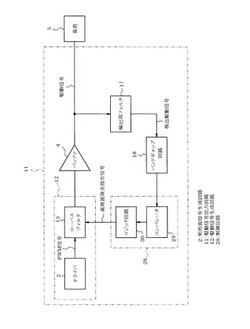

駆動信号出力回路

【課題】負荷、電源などの動作条件が変化しても、電磁妨害等を引き起こす周波数帯域の成分が除去された駆動信号を出力する。

【解決手段】負荷5に与えられる駆動信号をハイパスフィルタまたはバンドパスフィルタからなる検出用フィルタ17を介して検出し、その検出駆動信号をバンドギャップ回路18に入力する。バンドギャップ回路18は、固有の周波数特性を有し、検出駆動信号に固有の周波数帯域内の周波数成分が含まれていると出力電圧が低下する特性を持つ。制御回路28は、バンドギャップ回路18の出力電圧を基準電圧と比較し、検出駆動信号に固有の周波数帯域内の信号成分が含まれるか否かを判定する。含まれる場合には、ローパスフィルタ13により駆動信号から当該周波数帯域内の信号成分を除去する。

(もっと読む)

スイッチング素子の保護回路

【課題】窒化物FETを高速スイッチング動作させることができ、且つ、サージ電圧から窒化物FETを保護することができるスイッチング素子の保護回路。

【解決手段】直列に接続された高圧側素子M1及び低圧側素子M2と、高圧側素子をオンオフさせる信号を出力するハイサイドプリドライバ11と、高圧側素子と逆のオンオフ状態になるように低圧素子をオンオフさせる信号を出力するローサイドプリドライバ12と、高圧側素子と低圧側素子の接続点に制御端子が接続されたスイッチング素子Tr1と、スイッチング素子の一方の端子にカソードが接続されたダイオードD1と、ダイオードのアノードに入力端子が接続され、ダイオードのブレーク時にスイッチング素子の制御端子に電流を供給するとともに、低圧側素子のオフを指示する信号をローサイドプリドライバに供給する制御器21とを備える。

(もっと読む)

負荷駆動装置

【課題】オン時にパワー素子の立ち上がりが遅くなることを抑制し、負荷への電力供給のバラツキを抑制する。

【解決手段】スイッチ部13およびインピーダンス制御回路14とにより構成されたクランプ動作オフ固定回路を備える。このクランプ動作オフ固定回路により、駆動電圧がクランプオフ制御基準電圧に相当する参照電圧REF2以下のときには、インピーダンス制御回路14にてスイッチ部13を導通させることで、クランプ制御回路8によるクランプ動作をオフさせる。これにより、スイッチング時の基準電圧の変動などによって過渡的にノイズが発生しても、パワー素子5がオン動作を開始するときにクランプ制御回路8が誤動作することを防止することが可能となる。

(もっと読む)

電流駆動装置

【課題】駆動電圧を駆動回路へ安定的に供給しつつ、部品点数を少なくすることができる電流駆動装置を提供する。

【解決手段】パワートランジスタ3の主端子および制御端子が主端子接続端子13および制御端子接続端子14にそれぞれ接続されることにより、第1の電源4の電圧を所定の目標出力電圧に降圧する3端子レギュレータ10として機能する3端子レギュレータ構成回路12と、第1の電源4より低い電圧を出力する第2の電源6からの電力を用いて、3端子レギュレータ構成回路12がパワートランジスタ3の制御端子に印加する目標出力電圧に対応する制御電圧を設定する電圧設定回路18と、制御端子接続端子14に接続され、第1の電源4から電力が供給されると、3端子レギュレータ構成回路12の出力電圧VOUTが予め定められた電圧VC以下となるようにパワートランジスタ3の制御端子に印加される制御電圧を制御する電圧制限回路19とを備える。

(もっと読む)

閾値回路

【課題】閾値回路を低消費電力化する。

【解決手段】閾値回路は、ゲート端子が入力端子INに接続され、ソース端子が電源電位VDDに接続され、ドレイン端子が出力端子OUTに接続された第1のPMOSトランジスタQ1と、第1の端子が第1のPMOSトランジスタQ1のドレイン端子および出力端子OUTに接続され、第2の端子が接地された電流制限部I1と、第1の端子が第1のPMOSトランジスタQ1のドレイン端子および出力端子OUTに接続され、第2の端子が接地された電荷蓄積部C1とから構成される。電流制限部I1の電流値は、サブマイクロアンペア以下に設定される。

(もっと読む)

閾値回路

【課題】閾値回路を低消費電力化する。

【解決手段】閾値回路は、ゲート端子が入力端子INに接続され、ソース端子が電源電位VDDに接続された第1のPMOSトランジスタQ1と、ゲート端子が入力端子INに接続され、ソース端子がトランジスタQ1のドレイン端子に接続され、ドレイン端子が出力端子OUTに接続された第2のPMOSトランジスタQ2と、ゲート端子が出力端子OUTに接続され、ソース端子がトランジスタQ1のドレイン端子とトランジスタQ2のソース端子との接続点に接続され、ドレイン端子が接地電位に接続された第3のPMOSトランジスタQ3と、第1の端子が出力端子OUTに接続され、第2の端子が接地電位に接続された電流制限部I1とから構成される。

(もっと読む)

単位回路および電子回路

【課題】出力回路における各トランジスタのゲート・ソース間に印加される電圧を制限するための構成や単位回路へ入力される制御信号の振幅を小さくするための構成を簡素化する。

【解決手段】単位回路Jは、電源線101と接地線103との間に直列に接続された第1のPチャネルトランジスタ、第2のPチャネルトランジスタ、第1のNチャネルトランジスタ、および第2のNチャネルトランジスタとを備える。そして、第1のPチャネルトランジスタがオン状態のときにその電位がVDDとなり、第1のPチャネルトランジスタがオフ状態のときにその電位がVREF+Vtp2となる第1出力信号V1を第1出力端子から出力し、第2のNチャネルトランジスタがオン状態のときにその電位がGNDとなり、第2のNチャネルトランジスタがオフ状態のときにその電位がVREF−Vtn1となる第2出力信号V2を第2出力端子から出力する。

(もっと読む)

半導体集積回路、半導体集積回路の駆動方法、表示装置および電子機器

【課題】高耐圧化可能な半導体集積回路を提供する。

【解決手段】本発明に係る半導体集積回路は、電源電位と接続された出力ノードと、出力ノードと電源電位より低電位である接地電位との間に直列に接続された第1のnチャネル型トランジスター、第2のnチャネル型トランジスターおよび第3のnチャネル型トランジスターを有し、第1のnチャネル型トランジスターの一端は、接地電位に接続され、他端は、第2のnチャネル型トランジスターの一端に接続され、ゲート端子は、入力ノードに接続され、第2のnチャネル型トランジスターの他端は、第3のnチャネル型トランジスターに接続され、ゲート端子は、電源電位と接地電位との間に位置する第1中間電位に接続され、第3のnチャネル型トランジスターの他端は出力ノードに接続され、ゲート端子は電源電位に接続されている。

(もっと読む)

アナログスイッチ回路

【課題】切替え時のノイズを低減したアナログスイッチ回路を提供する。

【解決手段】入力信号をn個(nは、1以上)の出力信号としてそれぞれ出力するn個のスイッチ素子と、前記n個のスイッチ素子を制御するスイッチ制御回路と、前記入力信号の負荷となるインピーダンス素子と、前記インピーダンス素子を制御するインピーダンス制御回路と、を備え、前記スイッチ制御回路は、前記n個のスイッチ素子のすべてがオフ、またはいずれか1つがオンとなるように制御し、前記インピーダンス制御回路は、前記n個のスイッチ素子のいずれか1つがオンのときは、前記インピーダンス素子を最大のインピーダンスに制御し、前記n個のスイッチ素子がすべてオフのときは、前記インピーダンス素子を前記最大のインピーダンスよりも小さい第1のインピーダンスに制御する、ことを特徴とするアナログスイッチ回路が提供される。

(もっと読む)

誘導負荷制御装置

【課題】本発明は、誘導負荷に流れる負荷電流を止めなくても、負荷電流の電流検出部のオフセットを検出して補正をすることができる、誘導負荷制御装置の提供を目的とする。

【解決手段】誘導負荷30に流れる負荷電流の電流検出値を出力する電流検出回路12と、電流検出値に電流検出回路12のオフセットを反映することにより電流検出値を補正した補正検出値を出力する補正回路13と、負荷電流の電流値がその指示値に一致するように、補正検出値に基づいて、誘導負荷30を駆動するためのPWM信号のデューティ比を制御する制御回路14とを備えており、制御回路14は、負荷電流の電流値が安定した状態での制御方式を、閉ループ制御からその閉ループ制御で制御されていたデューティ比を維持するように制御する開ループ制御に切り替え、開ループ制御に切り替えられた状態で電流検出回路12のオフセットが検出される、誘導負荷制御装置。

(もっと読む)

二重ゲート電界効果トランジスタを用いたMOSトランジスタ回路およびCMOSトランジスタ回路

【課題】回路を構成する二重ゲート電界効果トランジスタの動作モードを、回路組み上げ後に適宜変更できるようにした二重ゲート電界効果トランジスタを用いたMOSトランジスタ回路およびCMOSトランジスタ回路を提供する。

【解決手段】二重ゲート電界効果トランジスタを用いたMOSトランジスタ回路は、二重ゲート電界効果トランジスタX1(21)の第1ゲートG1に第1の入力信号in1を加え、第2ゲートG2に選択回路11aを接続し、その選択回路11aに第1の入力信号in1と第2の入力信号in2を加え、選択回路11aにより第1の入力信号in1または第2の入力信号in2を選択して第2ゲートG2に加える。第2ゲートG2に切り替えて入力される入力信号に応じて、3端子動作又は4端子動作を行わせる。

(もっと読む)

過電流保護回路

【課題】従来の過電流保護回路では、トランジスタの特性ばらつきにより高精度の過電流検出ができないという問題があった。

【解決手段】本発明にかかる過電流保護回路は、負荷2に供給する電流に応じた検出用電流を生成する検出用MOSトランジスタQ2と、バイアス信号1に基づいて電流Iref1を生成するトランジスタ9と、バイアス信号1と異なるバイアス信号2に基づいてIref2を生成し、トランジスタ9と同一サイズのトランジスタ10と、電流Iref1と、電流Iref2と、検出用電流と、に基づいて過電流検出信号を出力するカレントミラー回路と、を備える。このような回路構成により、高精度の過電流検出が可能な過電流保護回路を提供することができる。

(もっと読む)

複数供給電圧の電力増加/減少検出器

複数供給電圧デバイスは、第1の供給電圧で動作する入出力(I/O)回路網と、I/O回路網に結合され、第2の供給電圧で動作するコア回路網と、I/O回路網およびコア回路網に結合された電力投入制御(POC)回路網とを含む。POC回路網は、I/O回路網へPOC信号を伝送するように構成され、コア回路網の電力状態を検出するように構成された調整可能な電流電力増加/減少検出器を含む。POC回路網はまた、調整可能な電流電力増加/減少検出器に結合され、電力状態を処理してPOC信号にするように構成された処理回路と、1つまたは複数のフィードバック回路とを含む。漏れ電流を低減させながら、電力増加/減少検出速度を改善するために、フィードバック回路は、調整可能な電流電力増加/減少検出器に結合され、フィードバック信号を提供して調整可能な電流電力増加/減少検出器の電流容量を調整するように構成される。  (もっと読む)

(もっと読む)

出力回路、及びそれを用いた車載用通信システム

【課題】回路面積が小さく、製造バラツキによる出力特性の劣化を修正できる出力回路を提供することにある。

【解決手段】本発明による出力回路は、差動入力信号DIに応じた差動出力信号BP、BNを出力端子対31、32から出力するメインバッファ回路1と、制御信号CSに応じて出力端子対31、32のインピーダンスを調整するトリミング回路2とを具備する。トリミング回路2は、第1電源VDDと出力端子対31、32との間に、メインバッファ回路1内の第1トランジスタ対MP1、MP2及び第1抵抗対R1、R2に対して並列に接続された少なくとも1つの第2トランジスタ対MP11、MP21を備える。

(もっと読む)

スイッチング電源回路

【課題】ソフトスタート機能を備えている場合でも、出力する電源電圧をより早く立ち上げることができるスイッチング電源回路を提供する。

【解決手段】スイッチング電源回路21に電源バイパス回路22を設け、電源バイパス回路22は、電源+Bが投入されてからその電圧が基準電圧Vref1に相当する所定の閾値に達するまでの間に、FET7及びπ型フィルタ14をバイパスさせて電源+Bを入力端子SWPINに供給する。従って、ソフトスタート回路19の機能によりFET7がスイッチング動作を開始するタイミングが遅れても、スイッチング電源回路21を経由して負荷に供給するメイン電源の電圧をより早く立ち上げることができる。

(もっと読む)

シュミットトリガ型インバータ

【課題】さらに入力ノイズ耐性を有するシュミットトリガ型インバータを提供すること。

【解決手段】入力側ノードへの供給電圧が増加して第1の基準電圧に達するに従い出力側ノードから出る電圧が比較高電圧レベルから比較低電圧レベルに遷移し、入力側ノードへの供給電圧が減少して第1の基準電圧より低い第2の基準電圧まで減少するに従い出力側ノードから出る電圧が比較低電圧レベルから比較高電圧レベルに遷移するインバータと、インバータの入力側ノードに一方端が接続された第1の抵抗素子と、インバータの入力側ノードに一方端が接続された、該一方端の電圧が上昇するほどに抵抗値が減じる可変抵抗素子と、可変抵抗素子の他方端に一方端が接続された第2の抵抗素子と、ドレインが第2の抵抗素子の他方端に接続され、ゲートがインバータの出力側ノードに接続され、ソースが接地電位に接続されたnチャネルMOSトランジスタとを具備する。

(もっと読む)

初期化信号出力回路、初期化信号出力制御方法

【課題】入力電源が複数ある場合において、複数の入力電源に対応した初期化信号出力回路において、回路規模の増大や消費電力の増大等を抑えること。

【解決手段】VDDAとVDDDとを含む複数の入力電源に基づいて、PORを出力するパワーオンリセット回路1であって、VDDAに基づいてPORの出力判断の基準となるCPinmを出力する基準電圧発生回路101と、VDDDの供給に応じてVDDAの電圧に応じたCPinpを出力する比較用電圧発生回路103と、CPinm及びCPinpの供給状態に応じてPORを生成する電圧比較器102と、VDDA及びVDDDの供給状態に応じてPORの出力を制御するパワーオンリセット制御回路104とを有することを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】ESD保護回路を共通化してチップ面積を低減し且つESD保護回路が故障しても保護される複数の被保護回路が同時に動作不能となることを回避する。

【解決手段】点火回路4とダイアグ回路5の各ノードを同一極性のダイオード10〜12を通して共通ノード31に接続し、共通ノード31とESD保護回路6との間に切り離し回路23を備える。ESD保護回路6が短絡故障していないときには、ダイオード41は非導通、分圧電圧Vb>基準電圧Vrとなり、FET35がオフ、FET34がオン可能となる。ESD保護回路6が短絡故障すると、ダイオード41は導通、分圧電圧Vb<基準電圧Vrとなり、FET35がオン、FET34がオフとなり、共通ノード31とESD保護回路6とを電気的に切り離す。

(もっと読む)

バッファ回路、トライステートバッファ回路、および半導体装置

【課題】接地電圧と電源電圧の電位差を規定値に保ち、誤動作を防止することができるバッファ回路及びその制御方法を提供する。

【解決手段】出力制御信号に応じて入力信号に対応する信号を出力する場合、第1スイッチング素子により出力スイッチング素子を導通状態に駆動し、第2および第3スイッチング素子により出力スイッチング素子を非導通状態に駆動する。一方、出力制御信号に応じてハイインピーダンス状態を出力する場合、第3スイッチング素子は非導通に制御されるので、出力スイッチング素子は、第2スイッチング素子のみにより非導通状態に駆動される。

(もっと読む)

分配装置及び録画装置

【課題】本発明は、入力端子に入力された信号を増幅して複数の出力端子に分配する状態と、入力端子に短絡した一の出力端子に出力する状態とを、一の出力端子から出力される信号が途切れないよう切替える分配装置及び当該分配装置を備えた録画装置を提供する。

【解決手段】MCU201は、分配回路から短絡回路に切替える場合、FET202をオン状態にして入力端子21を第3出力端子24に短絡する短絡回路を接続し、所定時間経過後にダイオードD1、D2をオフ状態にして増幅器AMP、分配器203及び減衰器ATT等からなる分配回路から入力端子21及び第3出力端子24を開放する。MCU201は、短絡回路から分配回路に切替える場合、ダイオードD1、D2をオン状態にして分配回路に入力端子21及び第3出力端子24を接続し、所定時間経過後にFET202をオフ状態にして短絡回路を開放する。

(もっと読む)

1 - 20 / 47

[ Back to top ]