Fターム[5J055GX10]の内容

Fターム[5J055GX10]に分類される特許

1 - 18 / 18

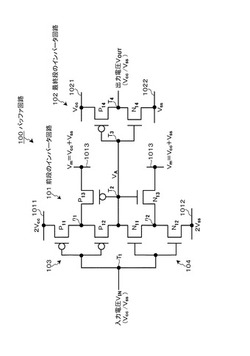

バッファ回路、走査回路、表示装置、及び、電子機器

【課題】回路を構成するトランジスタのソース−ドレイン耐圧を維持したまま、最終段のインバータ回路の入力電圧の振幅を増大させることが可能なバッファ回路を提供する。

【解決手段】第1導電型のトランジスタから成る第1トランジスタ回路と第2導電型のトランジスタから成る第2トランジスタ回路とが、第1固定電源と第2固定電源との間に直列に接続され、且つ、各入力端同士及び各出力端同士がそれぞれ共通に接続されており、第1,第2トランジスタ回路の少なくとも一方のトランジスタ回路がダブルゲートトランジスタから成るバッファ回路において、第1,第2トランジスタ回路の一方のトランジスタ回路が動作状態のとき、他方のトランジスタ回路のダブルゲートトランジスタの共通接続ノードに第3固定電源の電圧を与えるスイッチ素子を設ける。

(もっと読む)

半導体装置

【課題】消費電力を小さくでき、トランジスタ数が少ない半導体装置を提供する。

【解決手段】ソース及びドレインの一方が第1の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース及びドレインの一方が第1の配線と電気的に接続され、ゲートが第1のトランジスタのゲートと電気的に接続された第2のトランジスタと、一方の電極が第3の配線と電気的に接続され、他方の電極が第2のトランジスタのソース及びドレインの他方と電気的に接続された容量素子と、を有する。

(もっと読む)

半導体装置

【課題】しきい値電圧のばらつきの影響を低減する。

【解決手段】トランジスタのゲート・ソース間に設けられた容量素子に電荷を充電し、その後容量素子に充電された電荷を放電することで該トランジスタのしきい値電圧を取得し、その後負荷に電流を流す半導体装置において、容量素子の一方の端子の電位は、ソース線の電位より大きく設定し、ソース線の電位は電源線の電位及び負荷のカソード側の電位よりも小さい電位に設定する。

(もっと読む)

表示装置、表示モジュール及び電子機器

【課題】回路を構成するトランジスタ数を少なくし、且つレベルシフタを配置することな

くシフトレジスタとして正確に動作を行う半導体回路の提供することを課題とする。

【解決手段】第1端子が高電位電源に接続されたpチャネル型トランジスタと、第1端子

が低電位電源に接続されたnチャネル型トランジスタと、を含む回路群と、インバータ回

路と、をm段(mは任意の正の整数であり、m≧3)有し、第2n−1段目(nは任意の

整数であり、m≧2n≧2)の回路群の前記nチャネル型トランジスタのゲートにはクロ

ック信号が入力され、第2n段目(nは任意の整数であり、m≧2n≧2)の回路群の前

記nチャネル型トランジスタのゲートには反転クロック信号が入力される。

(もっと読む)

半導体装置

【課題】本発明は、信号線駆動回路におけるトランジスタの特性のばらつきの影響を抑制

する技術に関する。

【解決手段】信号線駆動回路には、各々容量手段と供給手段とを有する第1電流源回路(

437)及び第2電流源回路(438)を設ける。シフトレジスタ(418)から供給さ

れるサンプリングパルスと外部から供給されるラッチパルスに従って、前記容量手段は、

n個のビデオ信号用定電流源(109)の各々から供給される電流を加算した電流を電圧

に変換し、前記供給手段は変換された電圧に応じた電流を供給することで、トランジスタ

の特性によらず、ビデオ信号に応じた電流出力を行うことを特徴とする。前記n個のビデ

オ信号用定電流源から供給される電流値は、20:21:・・・:2nに設定されて、階

調を表現することが可能となる。

(もっと読む)

半導体チップおよびそれを用いた画像表示装置

【課題】画像表示装置の昇圧回路の高効率化を図ることが可能な半導体チップと、それを用いた画像表示装置を提供する。

【解決手段】この携帯電話機では、昇圧回路8のトランジスタ12の前段にバッファ14を設け、バッファ14の入力ノードの寄生容量値をトランジスタ12のゲートの寄生容量値よりも小さく設定し、トランジスタ12およびバッファ14を1つの半導体チップ21に搭載する。したがって、トランジスタ12のゲートにおけるPWM信号φPのレベル変化の鈍りを抑制することができ、昇圧回路の高効率化を図ることができる。

(もっと読む)

レベル変換回路および表示装置、並びに電子機器

【課題】回路構成の複雑化、消費電流の増加、特性低下を防止することができ、レイアウト面積の削減を図れるレベル変換回路および表示装置、並びに電子機器を提供する。

【解決手段】バイアス部12は、第5のNMOSトランジスタNT15と、抵抗素子R11を含む降圧部16と、電圧源15に接続された電流源I11と、を含み、第5のNMOSトランジスタNT15のソースが第1電圧源14に接続され、ドレインが抵抗素子R11の一端に接続され、抵抗素子R11の他端が電流源I11に接続され、第5のNMOSトランジスタNT15のゲートが抵抗素子R11の他端側に接続され、第1電圧から第1および第2のNMOSトランジスタNT11,NT12のしきい電圧分高く、または第1電圧より高くこのしきい値電圧より低いバイアス電圧を抵抗素子の一端側に生成し、レベル変換部11の第1および第2のNMOSトランジスタNT11,NT12のゲートに供給する。

(もっと読む)

液晶表示装置及び電子機器

【課題】 一導電型のTFTのみを用いて回路を構成することにより工程削減が

可能であり、かつ出力信号の電圧振幅が正常に得られる表示装置の駆動回路を提

供する。

【解決手段】 出力ノードに接続されているTFT203のゲート−ソース間に

容量205を設け、TFT201、202からなる回路は、ノードαを浮遊状態

とする機能を有する。ノードαが浮遊状態のとき、容量205によるTFT20

3のゲート−ソース間の容量結合を利用してノードαの電位をVDDよりも高い

電位とし、これによって、TFTのしきい値に起因する振幅減衰が生ずることな

く、正常にVDD−GND間の振幅を持った出力信号を得ることが出来る。

(もっと読む)

半導体集積回路、半導体集積回路の駆動方法、電子機器および電子機器の駆動方法

【課題】高耐圧化可能な半導体集積回路を提供する。

【解決手段】本発明に係る半導体集積回路は、第1電位ノード〔VDD〕と接続された第1ノード〔VOUT〕と、第1ノード〔VOUT〕と第1電位ノードより低電位である第2電位ノード〔VSS〕との間に直列に接続された第1のnチャネル型トランジスタ〔NT1〕および第2のnチャネル型トランジスタ〔NT2〕を有し、第1のnチャネル型トランジスタ〔NT1〕の一端は、第2電位ノード〔VSS〕に接続され、他端は、第2のnチャネル型トランジスタの一端に接続され、ゲート端子は、第2ノード〔VIN〕に接続され、第2のnチャネル型トランジスタ〔NT2〕の他端は、第1ノード〔VOUT〕に接続され、ゲート端子は、第1電位ノード〔VDD〕と第2電位ノード〔VSS〕との間に位置する第1中間電位〔VM1〕に接続されている。第2のnチャネル型トランジスタにより分圧され、各トランジスタに印加される電圧を低減できる。

(もっと読む)

半導体デバイス、表示パネル及び電子機器

【課題】使い勝手の良い単一チャネル型のバッファ回路を提案する。

【解決手段】単一チャネルの薄膜トランジスタで形成されるバッファ回路を、(a)第1及び第2の薄膜トランジスタの直列接続で構成される第1の出力段と、(b)一方の主電極が第1の薄膜トランジスタの制御配線(第1の制御配線)に接続され、他方の主電極が第2の薄膜トランジスタの電源に接続され、制御電極が第2の制御配線に接続される第7の薄膜トランジスタと、(c)一方の主電極が第2の薄膜トランジスタの制御配線(第2の制御配線)に接続され、他方の主電極が第2の薄膜トランジスタの電源に接続され、制御電極が第1の制御配線に接続される第8の薄膜トランジスタと、(d)第1の出力段と並列に接続される第2の出力段の出力端が制御電極に接続され、一方の主電極が第1の制御配線に接続される第11の薄膜トランジスタで構成される。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の駆動方法

【課題】ヒステリシス特性を示すインバータ回路の構成を簡素化しながら消費電力を低減する。

【解決手段】インバータ回路Q1は、Pチャネル型のトランジスタTR1と、Nチャネル型のトランジスタTR2とで構成される。信号供給点R1とトランジスタTR1のチャネルコンタクト領域Aとの間には容量C1が介在し、信号供給点R1とトランジスタTR2のチャネルコンタクト領域Aとの間には容量C2が介在する。信号供給点R1には閾値制御信号SC1が供給される。閾値制御信号SC1は、インバータ回路Q1からの出力信号SOUT1のレベルが低下し始める時点にてローレベルに設定されるとともに当該時点の経過後にハイレベルに設定され、かつ、出力信号SOUT1のレベルが上昇し始める時点にてハイレベルに設定されるとともに当該時点の経過後にローレベルに変化する。

(もっと読む)

電気回路、電気光学装置、電子機器、および電気回路の駆動方法

【課題】ヒステリシス特性を示すインバータ回路の構成を簡素化しながら消費電力を低減する。

【解決手段】インバータ回路Q1は、Pチャネル型のトランジスタTR1とNチャネル型のトランジスタTR2とで構成される。トランジスタTR1およびトランジスタTR2の各々のバックゲートには閾値制御信号C1が供給される。閾値制御信号C1は、インバータ回路Q1からの出力信号SOUT1のレベルが低下し始める時点にてローレベルに設定されるとともに当該時点の経過後にハイレベルに設定され、かつ、出力信号SOUT1のレベルが上昇し始める時点にてハイレベルに設定されるとともに当該時点の経過後にローレベルに変化する。

(もっと読む)

データ受信回路とデータドライバ及び表示装置

【課題】低消費電力で、高データ転送レートの差動信号を受信可能なデータ受信回路(レシーバ回路)の提供。

【解決手段】差動形式でデータ転送される2値信号を第1、第2の入力に受ける、第1導電型の第1、第2のトランジスタ(M81、M82)を含む差動対と、前記差動対の第1、第2の出力に接続され、ダイオード接続された、第2導電型の第1、第2のトランジスタ(M83、M84)よりなる負荷回路と、前記第2導電型の第1、第2のトランジスタ(M83、M84)に流れる電流(Ia、Ib)のそれぞれに対応した電流(Ic、Id)にて、出力端子(6)を充電、放電する出力回路(M87、M88)と、出力電流が、前記第2導電型の第1、第2のトランジスタの少なくとも1つに入力される電流供給回路(M11、M12)を備えている。

(もっと読む)

階調制御用出力回路及びその検査用装置,階調制御用出力回路の検査方法

【課題】 表示装置や出力装置に用いられ、良好な階調表示を実現する階調制御用出力回路を提供する。また、電流駆動用の階調制御用出力回路を検査するための手段を提供する。

【解決手段】 階調制御用出力回路は、ロー側カレントミラー部55と、ロー側階調制御回路59と、ハイ側カレントミラー部56と、ハイ側階調制御回路60と、電流嵩上げ制御回路61と、選択プリチャージ制御回路62とを備えている。階調信号を出力するための階調制御回路がハイ側とロー側に分かれていることで、出力電流の特性を発光素子のγ特性に近似させることができる。また、多段式カレントミラーを用いることで、出力部ごとの電流のばらつきも抑えられている。

(もっと読む)

電源回路ならびにそれを使用したマトリックス基板

【課題】 DC−DCコンバータ回路の初期化回路において、前記DC−DCコンバータ回路内で生成した電圧を自己電源として、電圧発生回路の駆動用バッファ回路電源として使用する構成の場合、電源立遮断時に出力電圧を確実に立ち下げ、貫通電流が流れることを防止する

【解決手段】 電源回路において、電圧発生回路4の出力15に接続され、初期化時に外部電源入力1と前記出力を導通するPchトランジスタ13と、前記出力に接続され、前記出力立ち下げ時に前記出力と接地電位間を導通するNchトランジスタ14と、スイッチ17と、前記電圧発生回路から前記スイッチを経由して電源電圧を供給され、前記Pchトランジスタのゲート12を駆動する駆動回路7とを有し、前記スイッチは、前記電圧発生回路の出力電圧が所定値以下のときに非接続状態となるよう構成された電源初期化回路60を含む。

(もっと読む)

レベルシフタ回路

【課題】信号のレベル切り替え時に生じる貫通電流を防止することで、低消費電力のレベルシフタ回路を提供する。

【解決手段】入力101の信号レベルが切り替わる際に流れる貫通電流を防ぐため、Pチャネル型TFT110,109,Nチャネル型TFT108または、Pチャネル型TFT116,115,NチャネルTFT104が同時にオンしないように、Pチャネル型TFT109,115を制御する。NチャネルTFT117のゲートにハイレベル信号が入力し、NチャネルTFT117がオンする瞬間にはPチャネル型TFT109をオフしておく。同様に、NチャネルTFT114がオンする瞬間にはPチャネル型TFT115をオフさせておく。Pチャネル型TFT110,109,Nチャネル型TFT108または、Pチャネル型TFT116,115,NチャネルTFT104を同時にオンさせないことにより、貫通電流の流れる経路を遮断する。

(もっと読む)

レベルシフタ回路及びそれを用いた表示素子駆動回路

【課題】回路規模の小さなレベルシフタ回路を実現する。

【解決手段】Pチャネル型のMOSトランジスタMP1を制御信号CTL1で、Nチャネル型のMOSトランジスタMN1を制御信号CTL2で、それぞれ制御する。制御信号CTL1と制御信号CTL2とは互いに独立している。制御信号CTL2を、データ信号DATA及び制御信号CTL3を入力とするNOR回路2により生成する。第1の電位及びGND電位をサンプリングする負荷容量C1を、MOSトランジスタMP2・MN2のゲート容量で構成する。

(もっと読む)

ブートストラップ回路及びその駆動方法並びにシフトレジスタ回路、論理演算回路、半導体装置

【課題】 ブートストラップ回路において、ブートストラップ効果によって上昇もしくは低下する電圧に、トランジスタの閾値電圧のばらつきに依存したばらつきが発生するため、半導体装置の信頼性が落ちる。これを解決する。

【解決手段】 ブートストラップ回路として、電圧を出力するトランジスタ1と、このトランジスタ1のゲートソース間に設けられたブートストラップ用の容量4と、電源VMと、トランジスタ1のゲート電極に対して電源VMの供給のオンオフ制御を行う回路3とにより構成する。ブートストラップ効果が生じる前の初期電圧を、トランジスタ1の閾値電圧に依存しない独立した電源VMの電位にできるため、ブートストラップ効果によって上昇もしくは低下する電圧(トランジスタ1のソース出力OUT)は、トランジスタ1の閾値電圧に依存したばらつきには影響されない。

(もっと読む)

1 - 18 / 18

[ Back to top ]