Fターム[5J056BB59]の内容

Fターム[5J056BB59]に分類される特許

1 - 20 / 99

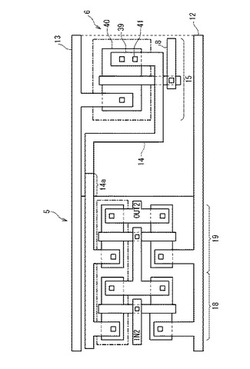

半導体集積回路の製造方法

【課題】常時動作領域と電源遮断可能領域とが混在する半導体集積回路を提供する。

【解決手段】半導体基板に設けられ、複数の基本セル(10)の配置が可能なセル配置領域と、空間的に前記セル配置領域と重なって設けられた基本電源配線(11)と、前記基本電源配線(11)から前記セル配置領域への電源供給を停止するスイッチセル(6)と、前記スイッチセル(6)に隣接して前記セル配置領域に配置され、前記スイッチセル(6)が前記セル配置領域への電源供給を停止した場合においても、前記スイッチセル(6)から電源供給を受ける常時動作セル(5)とを具備する。

(もっと読む)

論理回路

【課題】安定した高速動作を実現しつつ、製造工程も簡素化することが可能な論理回路を提供すること。

【解決手段】この論理回路1は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2のFET2A,2Bを備える論理回路であって、第1及び第2のFET2A,2BのうちのFET2Aは、ゲート端子が接続されるゲート電極膜17と、半導体材料からなるチャネル層12と、ゲート電極膜17とチャネル層12との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層16と、を有する。

(もっと読む)

半導体装置

【課題】製造プロセスによる閾値電圧の変動に起因する歩留まりの悪化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、複数のトランジスタが並列に接続された所定並列回路と、複数のトランジスタのオンオフ状態を制御しつつ所定並列回路のインピーダンスが所定値になったかを検出し、該インピーダンスが所定値になったときの複数のトランジスタのオンオフ状態に応じた制御値を生成する制御値生成部と、電源電圧を生成する電圧発生部と、電源電圧で動作する動作トランジスタと、制御値に基づいて電源電圧を制御する制御部と、を含む。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

信号出力回路

【課題】トランジスタ製造工程をnpn型の製造工程のみとして、使用可能な化合物半導体の自由度を高め、単相のデジタル信号により外部から出力透過/遮断を切替制御する。

【解決手段】トランジスタとしてnpn型を用いて構成し、入力バッファ11で、外部入力された単相切替指示信号10Sを、互いの位相が反転している差動切替指示信号11Sに変換し、発生制御回路13で、差動切替指示信号11Sに基づいて、制御電圧発生回路14における制御電圧VCSの発生を制御するための発生制御信号13Sを出力し、制御電圧発生回路14で、発生制御信号13Sに基づいて、単相切替指示信号10Sの論理に応じて電圧値が変化する制御電圧VCSを発生させて出力し、出力回路15で、入力された差動入力信号INをインピーダンス変換し差動出力信号OUTとして出力し、制御電圧VCSに基づいて当該差動入力信号INの出力透過/遮断を切り替える。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えることの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】5Tr1Cで構成されるインバータ回路1において、トランジスタT2のゲートと高電圧線L3との間に接続されたトランジスタT4,T5と、トランジスタT2のゲートと低電圧線L1との間に接続されたトランジスタT3とのオンオフ動作により、全期間に渡ってトランジスタT1,T2が同時にオンしないようになっている。

(もっと読む)

入力回路及び入力装置

【課題】入力端子をシンク型又はソース型に切換える場合に、基板を交換する必要がなく、また入力端子に誤って電源を接続してもスイッチング素子の破損を防止することができる入力回路及び該入力回路を備える入力装置を提供する。

【解決手段】ディップスイッチ70にてシンク型入力対応モードを選択した場合に、FET31をオフし、FET32をオンする。作業者が第2入力端子22に外部電源80を誤って接続した場合、FET32に大電流が流れる。定格電流よりも大きな電流がFET32に流れた場合、ヒューズ92は即時に切断される。そのためFET32の破損を防止することができる。またディップスイッチ70にてソース型入力対応モードを選択した場合に、FET31をオンし、FET32をオフするので、基板の交換を行うことなく、入力回路1をシンク型又はソース型に切換えることができる。

(もっと読む)

半導体集積回路装置

【課題】保護対象の回路ブロックの上に配置された導電パターンに加えられた改変の検出精度を向上するための技術を提供することを目的とする。

【解決手段】半導体基板に配置された回路ブロックと、回路ブロックのうち保護対象の部分の上層に配置された導電パターンと、導電パターンの第1部分の電位を基準電位にリセットするリセット部と、第1部分を電流供給ラインに接続する接続部と、第1部分の電位を基準電位にリセットした後に第1部分を電流供給ラインに接続してから一定時間経過後の第1部分の電圧が事前に設定された範囲に含まれるか否かを判定し、一定時間経過後の電圧が事前に設定された範囲に含まれない場合に導電パターンに改変が加えられたことを検出する検出回路とを有する半導体集積回路装置が提供される。第1部分の電圧の変化は、導電パターンの回路定数に依存する。

(もっと読む)

半導体集積回路装置

【課題】半導体基板の表側に配置された回路が半導体基板の裏側から解析されることを検出する技術を提供することを目的とする。

【解決手段】回路ブロックが配置された第1面と、第1面の反対側の第2面とを有する半導体基板と、半導体基板を搭載する実装基板と、実装基板のうち、回路ブロックの保護対象の部分と重なる領域に配置された導電パターンと、導電パターンに改変が加えられたことを検出する検出回路とを有する半導体集積回路装置が提供される。半導体基板の第2面と実装基板とが対向するように、半導体基板が実装基板に搭載されている。

(もっと読む)

半導体装置

【課題】しきい値が従来例では動作しないような値でも動作させることが可能な半導体装置である。

【解決手段】第1乃至第3のN型トランジスタと、第1乃至第3のP型トランジスタと、アナログスイッチと、容量手段とを有し、容量手段の一方は、アナログスイッチ、第3のN型トランジスタのソース又はドレインの他方、及び第3のP型トランジスタのソース又はドレインの他方と電気的に接続され、容量手段の容量は、第1のP型トランジスタ及び第1のN型トランジスタで発生する容量より大きく、アナログスイッチには、第1のラッチ信号、第2のラッチ信号、及びデータ信号が入力され、第1のラッチ信号は、第2のP型トランジスタのゲート、及び第3のN型トランジスタのゲートに入力され、第2のラッチ信号は、第2のN型トランジスタのゲート、及び第3のP型トランジスタのゲートに入力される半導体装置である。

(もっと読む)

半導体装置のトリミング方法、及びトリミング制御回路

【課題】スイッチ素子の製造バラツキを排除し、より均一で確実な溶断が行える半導体装置のトリミング方法、及びトリミング制御回路を提供すること。

【解決手段】電位が異なる第1電源(電源端子c)と第2電源(接地端子d)との間にて直列接続された第1スイッチ素子S1〜S3およびフューズF1〜F3を内蔵した半導体装置101における第1スイッチ素子S1〜S3をオン制御することでフューズF1〜F3に電圧を印加してフューズF1〜F3を溶断する半導体装置101のトリミング方法であって、第1スイッチ素子S1〜S3をターンオン制御することにより、第1電源(電源端子c)からフューズF1〜F3を溶断させない第1電圧値を所定時間印加するステップと、第1電圧値の印加が完了した後、第1電源(電源端子c)からフューズF1〜F3を溶断させる第2電圧値を印加するように切り替えるステップと、を含む。

(もっと読む)

インバータ回路および表示装置

【課題】消費電力を抑えつつ、出力電圧のばらつきをなくすことの可能なインバータ回路、およびこのインバータ回路を備えた表示装置を提供する。

【解決手段】3Tr2Cで構成されるインバータ回路において、トランジスタTr2のゲートと低電圧線L1との間、さらにトランジスタTr2のソースと低電圧線L1との間に、入力電圧Vinと低電圧線L1の電圧との電位差に応じてオンオフ動作するトランジスタTr1,Tr2が設けられている。トランジスタTr2のゲートには、容量素子C1,C2が直列接続されており、トランジスタTr2のソースには、容量素子C1,C2が並列接続されている。

(もっと読む)

半導体装置及び情報処理システム

【課題】FETの閾値電圧の変動に起因するアンプのセンスマージンの低下を防止可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、信号線(BL)に信号を出力する第1の回路(MC)と、FET(Q1、Q2、Q3)と、信号線に基準電位を与える第2の回路(Q5)を備えている。FETQ1はノードN1の電位と駆動信号SETの電位との間の電位差に応じてゲート容量が制御されるゲーテッドダイオードとして機能し、FETQ2は制御信号TGに応じて信号線とノードN1との間の接続を制御し、FETQ3はゲートがノードN1に接続されノードN1の信号電圧を増幅する。導通状態のFETQ2を非導通に制御した後、駆動信号SETの電位は第1の電位から第2の電位に遷移する。FETQ1の閾値電圧の変動量に対応して少なくとも第1の電位をオフセット制御し、FETQ3のセンス増幅時にFETQ1の閾値電圧の変動を補償する。

(もっと読む)

ディプレッション型FET用バイアス印加回路

【課題】単電源駆動の構成において常に所望のバイアス条件が得られると共に、生産性の向上、コストの低減を図ることができるようにする。

【解決手段】N−chディプレッション型FET1を単一の正電源3で駆動する構成において、FET1のソースと接地との間に、ソース電圧を制御するための第1(NPN)トランジスタQ1 が接続され、この第1トランジスタQ1 のベースには、このベースにFET1のドレイン電流の大きさに応じた調整用電流を供給するための第2(PNP)トランジスタQ2 が接続される。また、FET1のドレインと正電源3との間に、ドレイン電流検出用の抵抗R3が接続され、上記第1トランジスタQ1 によりFET1のソース電圧を制御することで、FET1のドレイン電流が常に一定となるように自動調整を行う。

(もっと読む)

波形発生装置および半導体試験装置

【課題】複数のタイミングエッジ発生回路のそれぞれのタイミング補正を行うときに、タイミング補正を行うための設定内容を単純化させることを目的とする。

【解決手段】波形を発生する波形発生装置1であって、波形のタイミングを規定するタイミングエッジデータTEDを生成する複数のタイミングエッジデータ生成部3と、タイミングエッジデータTEDを入力して、この入力したタイミングエッジデータTEDのタイミングでタイミングエッジTEを発生する複数のタイミングエッジ発生部4と、タイミングエッジに基づいて波形を発生するフリップフロップ7と、タイミングエッジデータTEDの出力先を任意のタイミングエッジ発生部4に変更可能にした出力変更部14と、を備えている。

(もっと読む)

半導体装置

【課題】複数の入力信号が、競合回路を経由してメモリセルアレイに入力される半導体装置において、記憶容量の異なる複数のメモリマクロに対してそれぞれ異なる基本セルを用意することなく、データ・セットアップタイム、データ・ホールドタイムを変えずに、メモリマクロを自動設計できる半導体装置を提供する。

【解決手段】各々の入力信号は、それぞれ遅延回路を経由して競合回路に接続され、遅延回路はPチャンネル及びNチャンネルのクロックゲートを備えたクロックインバータで構成され、Pチャンネルクロックゲートのゲートは抵抗を経由して電源に、Nチャンネルクロックゲートのゲートは抵抗を経由して接地に、Pチャンネルクロックゲートのゲートは全てノードAに接続され、ノードAから抵抗を経由して接地に接続され、Nチャンネルクロックゲートのゲートは全てノードBに接続され、ノードBから抵抗を経由して電源に接続されたことを特徴とする。

(もっと読む)

半導体集積回路の設計方法及びプログラム

【課題】タイミング制約を満たすためにセルの物理的な位置やRTL(Register Transfer Level)を変更する必要がなく、回路の最適化を短時間に行うことができ、半導体集積回路の設計期間を短縮することができる半導体集積回路の設計方法、設計プログラムを提供する。

【解決手段】半導体集積回路のネットリストに対して静的タイミング解析を行うことにより、所定のタイミング制約を満たさないタイミングエラーパスを検出し、前記タイミングエラーパスを含む第1の論理ブロックと、フリップフロップを介して前記第1の論理ブロックに接続され、所定のタイミング制約を満たす第2の論理ブロックとを抽出し、前記第1の論理ブロックと前記第2の論理ブロックとの間のフリップフロップが正相/逆相フリップフロップである場合は、当該正相/逆相フリップフロップを逆相/正相フリップフロップに変更する。

(もっと読む)

可変駆動電圧により動作するオシレータ

【課題】安定した発振周期の信号を出力することができるオシレータを提供すること。

【解決手段】複数の論理素子がリング状に接続され、所定の周期の発振信号を出力する可変駆動電圧により動作するオシレータであって、複数の論理素子に選択的に印加される第1及び第2の駆動電圧を発生させる内部電圧発生手段を備え、発振信号の周期が正常状態である場合には、第1の駆動電圧が複数の論理素子に印加され、発振信号の周期が正常状態より短いか又は長い場合には、第2の駆動電圧VOSCが複数の論理素子に印加され、発振信号の周期が一定に維持されるように構成されている。

(もっと読む)

液晶表示装置及び電子機器

【課題】 一導電型のTFTのみを用いて回路を構成することにより工程削減が

可能であり、かつ出力信号の電圧振幅が正常に得られる表示装置の駆動回路を提

供する。

【解決手段】 出力ノードに接続されているTFT203のゲート−ソース間に

容量205を設け、TFT201、202からなる回路は、ノードαを浮遊状態

とする機能を有する。ノードαが浮遊状態のとき、容量205によるTFT20

3のゲート−ソース間の容量結合を利用してノードαの電位をVDDよりも高い

電位とし、これによって、TFTのしきい値に起因する振幅減衰が生ずることな

く、正常にVDD−GND間の振幅を持った出力信号を得ることが出来る。

(もっと読む)

走査駆動部及び有機電界発光表示装置

【課題】PMOSトランジスタのみで論理和を実現することのできる論理ゲートを提供する。

【解決手段】本発明の論理ゲートは、複数の入力信号に対応して第1ノードN1の電圧を制御する第1駆動部10と、第1ノードN1の電圧値を制御する第2駆動部12と、第1ノードN1に印加される電圧値に対応して第1電源VDDと出力端子Voutとの接続要否を制御する第3駆動部14と、第3駆動部14と第2電源VSSとの間に接続される制御トランジスタM8と、制御トランジスタM8のゲート電極と第2電源VSSの接続要否を制御する第4駆動部16とを具備し、第1駆動部〜第4駆動部を構成するトランジスタ及び制御トランジスタM8はPMOSのみで形成されていることを特徴とする。

(もっと読む)

1 - 20 / 99

[ Back to top ]