Fターム[5J056CC26]の内容

Fターム[5J056CC26]に分類される特許

1 - 10 / 10

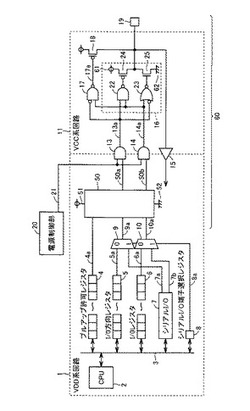

半導体装置

【課題】小面積化、低コスト化を図ることが可能な半導体装置を提供すること。

【解決手段】制御回路50は、I/O方向レジスタ5から出力される値を信号50aとして出力し、信号50aに応じて、プルアップ許可レジスタ4から出力される値とI/Oレジスタ6から出力される値とのいずれかを選択して信号50bとして出力する。AND回路13は、電源制御部20から出力される信号21と制御回路50から出力される信号50aとの論理和を演算して出力する。AND回路14は、電源制御部20から出力される信号21と制御回路50から出力される信号50bとの論理和を演算して出力する。トライステートバッファ16は、AND回路13および14から出力される値に応じて、電極19に接続される外部のデバイスを駆動する。したがって、レベル変換(AND)回路の数を削減することができ、半導体装置の小面積化、低コスト化を図ることが可能となる。

(もっと読む)

回路装置及び回路装置の制御方法

【課題】プルアップ電流を増加することなく、オープンドレイン接続の信号ラインのスルーレートを向上させる。

【解決手段】オープンドレイン若しくはオープンコレクターの出力端子を駆動する出力回路と、前記出力回路を制御する制御回路と、を含み、前記制御回路は、前記出力回路が前記出力端子にローレベルを出力しない期間において、前記出力端子がローレベルからハイレベルに遷移する場合に前記出力回路が前記出力端子にハイレベルを出力する制御を行うことを特徴とする。

(もっと読む)

出力回路、システム、及び出力回路の制御方法

【課題】信号波形の変異を抑制すること。

【解決手段】第1のトランジスタT1は、信号S5に応答してオンオフし、オンしたトランジスタT1は外部端子P2に接続された伝送路27をプルダウンする。第1のトランジスタT1のゲート端子には、伝送路27の波形を整形するためのキャパシタC1の第1端が接続され、キャパシタC1の第2端はクランプ回路46に接続されている。クランプ回路46は、プルダウン用のトランジスタT1と同様に、キャパシタC1の第2端が接続されたノードNDの電位を制御する。

(もっと読む)

CML信号の論理ファミリ間の変換を行うシステムおよび方法

【課題】CML信号論理ファミリ間の変換を行うシステムおよび方法を提供すること。

【解決手段】システムは、第1のバイアス信号および第1のCML論理ファミリの第1のCML信号を受け取るように構成される第1のCMLバッファを備える。第1のCMLバッファは、第1のCML信号および第1のバイアス信号に基づいて、第1のCML論理ファミリの第2のCML信号を生成する。第1の結合コンデンサ・モジュールは、第1のCMLバッファに結合している。第1の結合コンデンサ・モジュールは、第2のCML信号を受け取り、第2のCML信号に基づいて第3のCML信号を生成する。第2のCMLバッファは、結合コンデンサ・モジュールに結合しており、第2のバイアス信号および第3のCML信号を受け取って、第2のCML論理ファミリの第4のCML信号を生成する。帰還モジュールは、第2のCMLバッファに結合しており、第4のCML信号を受け取って第5のCML信号を生成する。第2のCMLバッファは、第2のバイアス信号、第3のCML信号、および第5のCML信号に基づいて第4のCML信号を生成する。

(もっと読む)

オープンドレイン出力回路

【課題】I2Cバスインターフェース規格に対応した出力信号の立ち下がり特性及び立ち上がり特性を備えながら、入力信号の遷移に対する遅延を揃えた出力信号を出力可能とするI2Cバスインターフェースに使用して好適なオープンドレイン出力回路を提供する。

【解決手段】入力信号INの遷移に基づいて、出力ノードN1の電位を急峻に立ち下げる第一の動作と、緩やかに立ち上げる第二の動作とを行う入力部4と、出力ノードN1がゲートに接続されて、入力部4の第一の動作に基づいてオフ動作し、第二の動作に基づいてオン動作して出力電流を緩やかに増大させるとともに、ドレインが出力端子に接続されるオープンドレイン構成の出力トランジスタTr3を備えたオープンドレイン出力回路で、入力部4には、入力信号INの遷移から出力トランジスタTr3が動作するまでの遅延時間の差を縮小する遅延時間調整回路R3,Tr4を備えた。

(もっと読む)

駆動回路

【課題】ターンオン及びターンオフでスルーレート制御できる駆動回路を提供する。

【解決手段】トランジスタP1のゲート電圧と閾値電圧との比較結果を出力する閾値電圧検出回路S1の出力によって動作しトランジスタP1のゲート−ソース間電圧をプルアップするプルアップスイッチN14と、抵抗R11と並列に接続される電流バイパス手段P13からなるスルーレート制御回路C11と直列をなして入力信号と逆相でオン/オフするプルダウンスイッチP12と、プルアップスイッチN14と並列に接続されて入力信号に従ってオン/オフするスイッチ手段N13と第2の抵抗R12との直列構成からなる第2のスルーレート制御回路C12を備え、ターンオン及びターンオフでスルーレート制御できる。

(もっと読む)

レベルシフタ回路、およびレベルシフタ回路を組込んだ表示パネル

【課題】製造コストを抑えたレベルシフタ回路、及び、そのレベルシフタ回路を備えた表示パネルを提供することを目的とする。

【解決手段】入力信号をレベルシフトするために表示パネルDP上に設けられるレベルシフタ回路C1であって、入力信号の電圧振幅よりも大きい電源電圧が印加される一対の電源端子と、その一対の電源端子間に接続されるスイッチング素子W2と、スイッチング素子W2の閾値Vthに対応するバイアス電位に設定され、入力信号が容量結合により入力されたときにバイアス電位を入力信号に重畳してスイッチング素子W2のゲートに供給する入力端子ITとを備え、スイッチング素子W2は表示パネルDP上の画素スイッチング素子W1と同一の導電型であるレベルシフタ回路。

(もっと読む)

オープンドレイン出力回路

【課題】入力電源電圧が出力段のトランジスタの閾値電圧以下の低い領域にあっても、出力電圧の不要な持ち上がりを抑圧し、確実な回路動作を実現する。

【解決手段】出力用NMOSトランジスタ11のバックゲートは、定電流源25が接続されたバックゲート駆動用NMOSトランジスタ12のドレインに接続されており、出力用NMOSトランジスタ11が未だオンとならない入力電源電圧が低い領域にあっては、バックゲートに正の電圧が印加される一方、入力電源電圧が上昇すると、出力用NMOSトランジスタ11と共にバックゲート駆動用NMOSトランジスタ12がオンとされることで、バックゲートはグランドレベルとされるため、出力用NMOSトランジスタ11の閾値電圧の引き下げと、出力電圧の持ち上がりが抑制されるようになっている。

(もっと読む)

半導体装置

【課題】高速で信号/データを転送することのできる小占有面積の終端回路を内蔵する出力回路を提供する。

【解決手段】パッド(5)を駆動する出力トランジスタ(2a、2b、4a、4b)をドレイン不純物領域(PDa、NDa)を共有する単位トランジスタの並列体で構成し、また、終端抵抗(12、14)を介してパッドを終端する終端トランジスタ(11a、11b、15a、15b)も、それぞれ、ドレイン不純物領域を共有する単位トランジスタの並列体で構成する。また、終端トランジスタの各単位トランジスタのドレインコンタクト-ゲート間距離(Lpt,Lnt)は、出力トランジスタの各単位トランジスタのドレインコンタクト-ゲート間距離(Lpo,Lno)よりも短くする。サージに対する信頼性を確保しつつ終端回路の面積を低減する。

(もっと読む)

ドライバ回路

【課題】 高速動作と低消費電力を両立させることが可能なドライバ回路を提供する。

【解決手段】 低電位側電源を基準とした論理信号Xが入力されて、高電位側電源Vccを基準とした論理信号Yを生成するドライバ回路であり、レベルシフト回路10、出力回路20、第1の検出制御回路30、および第2の検出制御回路40から構成される。ここでは、レベルシフト回路10に入力する論理信号Xおよび反転された論理信号X*によって、プルダウン回路21とトランジスタQ11,Q21とを相補的にオンオフ駆動し、第1の検出制御回路30からの制御信号out1に基づいて駆動回路11を流れるドレイン電流I1を制御するとともに、第2の検出制御回路40からの制御信号out2に基づいてプルダウン回路21を流れるドレイン電流I2を制御している。

(もっと読む)

1 - 10 / 10

[ Back to top ]