Fターム[5J056DD38]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | バイポーラトランジスタとFETの組合せ (147) | FETはN型のみ (17)

Fターム[5J056DD38]に分類される特許

1 - 17 / 17

半導体装置

【課題】消費電力を小さくでき、トランジスタ数が少ない半導体装置を提供する。

【解決手段】ソース及びドレインの一方が第1の配線と電気的に接続され、ソース及びドレインの他方が第2の配線と電気的に接続された第1のトランジスタと、ソース及びドレインの一方が第1の配線と電気的に接続され、ゲートが第1のトランジスタのゲートと電気的に接続された第2のトランジスタと、一方の電極が第3の配線と電気的に接続され、他方の電極が第2のトランジスタのソース及びドレインの他方と電気的に接続された容量素子と、を有する。

(もっと読む)

液晶表示装置

【課題】動作を不安定にすることなく、各トランジスタの特性劣化を抑制することが可能

な半導体装置を提供することを課題とする。

【解決手段】非選択期間において、トランジスタが一定時間毎にオンすることで、シフト

レジスタ回路の出力端子に電源電位を供給する。そしてシフトレジスタ回路の出力端子は

、該トランジスタを介して電源電位が供給される。該トランジスタは非選択期間において

常時オンしていないので、該トランジスタのしきい値電位のシフトは、抑制される。また

、シフトレジスタ回路の出力端子は、該トランジスタを介して一定期間毎に電源電位が供

給される。そのため、シフトレジスタ回路は、ノイズが出力端子に発生することを抑制で

きる。

(もっと読む)

通信ドライバ回路

【課題】外乱ノイズが侵入した場合でも、通信線の信号レベルの変動をより確実に防止できる通信ドライバ回路を提供する。

【解決手段】通信ドライバ部11は、信号バス17にノイズが印加されると、信号レベル変化阻止回路14が、出力段がオープンコレクタタイプで構成される反転増幅回路13の出力信号がローレベル側に変化することを阻止するように動作する。

(もっと読む)

信号出力回路

【課題】より簡単な構成で、正弦波と同様に緩やかに変化する波形でスイッチング素子を制御できる信号出力回路を提供する。

【解決手段】NチャネルMOSFET8Tは、ゲートに与えられるPWM信号のレベル変化に応じてカレントミラー回路7の動作を制御し、カレントミラー回路7が動作すると電流源6が発生した電流がミラー電流として流れ、NチャネルMOSFET1のゲートを介してゲート−ソース間の容量成分に充電されている電荷を放電させる電流が流れる。カレントミラー回路7の動作が停止すると、カレントミラー回路5より電流源6を介して流れる電流が、NチャネルMOSFET1のゲートに充電電流として供給される。

(もっと読む)

ディプレッション型FET用バイアス印加回路

【課題】単電源駆動の構成において常に所望のバイアス条件が得られると共に、生産性の向上、コストの低減を図ることができるようにする。

【解決手段】N−chディプレッション型FET1を単一の正電源3で駆動する構成において、FET1のソースと接地との間に、ソース電圧を制御するための第1(NPN)トランジスタQ1 が接続され、この第1トランジスタQ1 のベースには、このベースにFET1のドレイン電流の大きさに応じた調整用電流を供給するための第2(PNP)トランジスタQ2 が接続される。また、FET1のドレインと正電源3との間に、ドレイン電流検出用の抵抗R3が接続され、上記第1トランジスタQ1 によりFET1のソース電圧を制御することで、FET1のドレイン電流が常に一定となるように自動調整を行う。

(もっと読む)

回路装置、電子機器及び電源供給方法

【課題】回生により消費電力を抑制する回路装置、電子機器及び電源供給方法等を提供すること。

【解決手段】回路装置は、第1の電源電圧VPと第2の電源電圧VMを供給する電源回路100と、第1の電源電圧VPと第2の電源電圧VMが供給されることで断熱的回路動作を行う論理回路200と、を含む。電源回路100が供給する第1の電源電圧VPは、第1の基準電圧を基準電圧として周期的に変化する。電源回路100が供給する第2の電源電圧VMは、第2の基準電圧を基準電圧として周期的に変化する。電源回路100は、第1の電源電圧VPと第2の電源電圧VMの電圧差が小さくなっていく第1の期間と大きくなっていく第2の期間を繰り返す第1の電源電圧VPと第2の電源電圧VMを共振により供給する。

(もっと読む)

データ通信回路、送信機器、受信機器、送受信システム

【課題】データ通信回路において電圧緩和トランジスタの耐圧破壊を抑制する。

【解決手段】ドライバ(101)は、供給ノード(N101)を介してデータ信号を供給する。電圧緩和トランジスタ(102)は、ドライバの供給ノード(N101)に接続されたソースと、信号線に接続される信号ノード(N1)に接続されたドレインと、信号ノード(N1)の電圧(V1)が与えられるゲートとを有する。

(もっと読む)

レベルシフト回路

【課題】消費電流を低減することができ、信号伝達に必要な電源電圧を低減することができ、電源電圧が揺れても正確に信号を伝達することができるレベルシフト回路を得る。

【解決手段】本発明のレベルシフト回路は、インバータ回路INV2、レベルシフト素子MOS1、第1の抵抗R1及びカレントミラー回路CM1を備える。インバータ回路INV2は、入力信号を反転して出力する。レベルシフト素子MOS1は、インバータ回路INV2の出力信号をゲート信号として動作する。第1の抵抗R1の一端は、インバータ回路の出力に接続されている。カレントミラー回路CM1は、第1の抵抗R1を介してインバータ回路INV2の出力から入力した電流に対応する電流をレベルシフト素子MOS1のソースから接地点に流す。

(もっと読む)

半導体集積回路

【課題】電源起動時のリーク電流によるトランジスタの誤作動を防止することが可能な半導体集積回路を提供すること。

【解決手段】発明にかかる半導体集積回路は、第1の制御信号を駆動回路120を介して出力する論理回路209と、コレクタが高電位側の電源電圧VCCに接続され、エミッタが出力端子VOUTに接続され、ベースに入力される第1の制御信号に応じてオンオフが制御されるNPN型バイポーラトランジスタ201をそなえる。また、一方の端子がベースと駆動回路210との間のノードに接続され、他方の端子が電源電圧及び接地電圧のいずれか一方に接続されたトランジスタスイッチ203と、第1のトランジスタスイッチに並列に接続された抵抗素子205とを備える。このような回路構成により、電源起動時のリーク電流によるトランジスタの誤作動を防止することができる。

(もっと読む)

信号伝達回路

【課題】2次側回路のGNDの電位の立上りタイミングと1次側回路から2次側回路へ信号を送るタイミングとが重なっても、トランスを介して1次側回路から2次側回路へ信号を正しく伝達することが可能な信号伝達回路を提供することを目的とする。

【解決手段】電源部54、55のnpnバイポーラトランジスタ60のON抵抗を小さくしてC点又はD点の電位と基準電圧V3とをコンパレータ2で比較しC点又はD点の電位が基準電圧V3よりも大きくなったらON抵抗が十分に小さいNチャネルのMOSFET3を立下り遅延回路4により設定される一定時間オンさせることによって、2次側回路のGNDの電位の立上りタイミングに流れるトランス53の結合静電容量を充電する電流をMOSFET3を介して1次側回路51のGNDに流す。

(もっと読む)

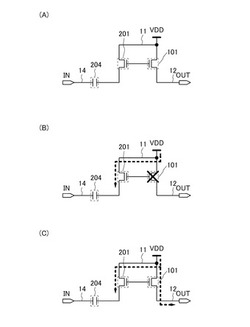

半導体装置および表示装置

【課題】 単極性のトランジスタを用いたデジタル回路であっても、出力信号の振幅が小さくなってしまうことを防ぎ、正常に動作する手段を有する半導体装置を提供する。

【解決手段】 ダイオード接続されたトランジスタ101がオフすることによって、トランジスタ102のゲートが、フローティング状態となる。そのとき、トランジスタ102は、オン状態にあり、そのゲート・ソース間には電位差が生じている。

トランジスタ102がオン状態にあるため、トランジスタ102のソースの電位は上昇するが、トランジスタ102のゲート・ソース間の容量によって、ゲート・ソース間の電位が保持されており、かつトランジスタ102のゲートはフローティングとなっているため、容量結合効果によってトランジスタ102のゲートの電位も上昇する。その結果、出力信号の振幅が小さくなることを防ぐことが出来る。

(もっと読む)

バス用出力回路

【課題】電流の逆流防止用のショットキ・ダイオードを無くし、一般的なプロセスを用いて制御部とバス用出力回路を一体化してIC化できるようにする。

【解決手段】電流制御回路(3)は、参照電圧と出力ノード(6)の電圧を比較し、半導体スイッチング素子(2)を制御する。半導体スイッチング素子(2)は、出力ノード(6)の電圧が参照電圧より低いとき電流源(1)を出力ノード(6)に接続し、出力ノード(6)の電圧が参照電圧より高いとき電流源(1)と出力ノード(6)の接続を切り離す。電流制御回路(3)と半導体スイッチング素子(2)によって、ショットキ・ダイオードと等価な機能を実現する。

(もっと読む)

差動信号振幅の自動調整回路

【課題】外部の測定装置を必要とすることなく、差動信号の振幅を自動的に調整することが可能な差動信号振幅の自動調整回路を提供する。

【解決手段】差動信号振幅の自動調整回路100は、差動信号を送信する差動信号トランシーバ1と、差動信号の振幅を設定するための複数の設定値が格納された振幅設定レジスタ2と、差動信号の振幅を制御する振幅コントロール回路3と、テスト用パターンを出力するパターン生成回路4と、マルチプレックサ5と、スケルチ判定レシーバ6と、テスト用ループバック回路7と、スケルチ信号の変化の期待値を格納するスケルチ変化検出期待値メモリ8と、スケルチ信号の変化をカウントするスケルチ変化検出カウンタ9と、期待値とカウント値とを比較し、その差分値を出力する比較回路10と、この差分値を格納する比較結果メモリ11と、コントローラ12と、を備える。

(もっと読む)

レベル変換回路

【課題】チップ面積の増大がなく低消費電力でありながら高速動作が可能なレベル変換回路を提供する。

【解決手段】駆動電流増加のためのトランジスタとHIGHレベルからLOWレベルへの遷移時間を短縮するためのGND端子へ接続された抵抗と蓄積された電荷を放電させるためのGNDに接続された抵抗とHIGHレベルからLOWレベルへの遷移時に微分的に蓄積電荷を放電させる容量からなる構成によりチップ面積の増大がなく低消費電力でありながら高速動作が可能となる。

(もっと読む)

半導体集積回路装置及び情報システム

【課題】動作時に機能ブロックの一部をきめ細かく電源遮断し、リーク電流を削減する半導体集積回路技術を提供する。

【解決手段】クロックツリー、組み合わせ回路、フリップフロップ7,8、電源スイッチ9を有する機能ブロック1において、フリップフロップ7,8のクロックが停止する際にフリップフロップ7,8の内容を失うことなく、組み合わせ回路の一部領域11とフリップフロップ7,8の一部回路の電源遮断を行う。クロックツリーの上位側の制御信号を加工した信号を電源スイッチ9の制御信号に用いることで、電源制御のない場合に比べ、タイミング悪化を押さえつつ、広範囲の組み合わせ回路とフリップフロップ7,8の電源制御が可能となる。フリップフロップ7,8のクロックが再開されると、組み合わせ回路とフリップフロップ7,8の一部回路の電源が供給され、動作が再開される。

(もっと読む)

入出力回路装置

【課題】動作電圧が異なる半導体装置同士を接続する入出力回路装置を高電圧で且つ十分なホットキャリア耐性を持たせられるようにする。

【解決手段】入出力回路装置10は、半導体基板101に形成されており、ゲート105が入力信号を受け、ソース拡散層106が接地され、ドレイン拡散層107が内部ノードVcと接続されたプルダウントランジスタQ1と、ゲート115が電源電圧VDDを受け、ソースドレイン拡散層116の一方が入出力ノードV0と接続され、ソースドレイン拡散層116の他方が内部ノードVcと接続されたカスケードトランジスタQ2とを有している。カスケードトランジスタQ2の基板電位は、電気的にフローティング状態にされている。

(もっと読む)

終端回路、および終端回路を備える半導体装置

【課題】

配線層抵抗およびトランジスタのオン抵抗の抵抗値のばらつきに対し、所望の終端抵抗値になるように調整する。

【解決手段】

入力回路18を接続する入力端子30と第1のノードとの間に配線層抵抗10を、第1のノードと接地との間にトランジスタ群12を、第1のノードと第2のノードとの間に配線層抵抗11を、第2のノードと接地との間にトランジスタ群13を、接続する。さらに、入力端子30と第3のノードとの間に配線層抵抗14を、第3のノードと電源VDDとの間にトランジスタ群16を、第3のノードと第4のノードとの間に配線層抵抗15を、第4のノードと電源VDDとの間にトランジスタ群17をさらに接続する。トランジスタ群12、13、16、17は、それぞれ制御信号BN1〜4、BN5〜8、BP1〜4、BP5〜8によってオンオフされる1または複数のトランジスタから構成される。

(もっと読む)

1 - 17 / 17

[ Back to top ]