Fターム[5J056DD43]の内容

論理回路 (30,215) | 構成要素(素子) (5,667) | トランジスタ(UJT、IGBT他) (4,294) | トランジスタの組合せ (2,266) | しきい値の異なる同種トランジスタの組合せ (66)

Fターム[5J056DD43]の下位に属するFターム

2種類のしきい値の組合せ (16)

3種類以上のしきい値の組合せ (8)

Fターム[5J056DD43]に分類される特許

1 - 20 / 42

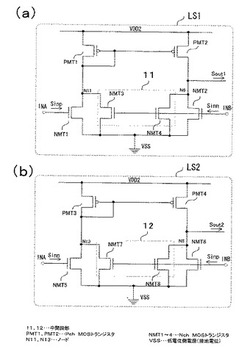

レベルシフト回路

【課題】レベルシフト回路のデータレートの変化時に発生するスキューを抑制する。

【解決手段】一つの実施形態によれば、レベルシフト回路には第1及び第2のレベルシフタが設けられる。第1のレベルシフタは、第1乃至4のトランジスタが設けられ、レベルシフトされた第1の出力信号を出力する。第2のレベルシフタは、第5乃至8のトランジスタが設けられ、レベルシフトされた第1の出力信号とは逆位相の第2の出力信号を出力する。第1の入力信号が入力される第1のトランジスタと差動対をなす第2のトランジスタに、第1の入力信号とは逆位相のハイレベルの第2の入力信号が入力されると第3及び4のトランジスタも同時にオンする。第2の入力信号が入力される第5のトランジスタと差動対をなす第6のトランジスタに、ハイレベルの第1の入力信号が入力されると第7及び8のトランジスタも同時にオンする。

(もっと読む)

半導体装置

【課題】小型化、低電圧・低電力化ならびに高速化が可能なセンスアンプを提供する。

【解決手段】増幅作用をする交差結合された第1のMOSトランジスタと第2のMOSトランジスタのそれぞれのソースに直列に第3のMOSトランジスタと第4のMOSトランジスタを接続し、第3及び第4のMOSトランジスタの電流供給能力を第3及び第4のMOSトランジスタの制御電極に与える制御電圧で制御する。データ保持期間において、制御電圧により第3及び第4のMOSトランジスタに、データ保持に必要な最小限のサブスレッショルド電流を流し、ビット線電位を保持する。

(もっと読む)

パルス信号出力回路およびシフトレジスタ

【課題】開示する発明の一態様は、安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供することを課題の一とする。

【解決手段】開示する発明の一態様のパルス信号出力回路は、第1乃至第10のトランジスタを有し、第1のトランジスタおよび第3のトランジスタのチャネル長Lに対するチャネル幅Wの比W/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは、第6のトランジスタのW/Lよりも大きく、第5のトランジスタのW/Lは、第7のトランジスタのW/Lと等しく、第3のトランジスタのW/Lは、第4のトランジスタのW/Lよりも大きくする。これによって、安定して動作することが可能なパルス信号出力回路及びそれを含むシフトレジスタを提供することができる。

(もっと読む)

半導体装置

【課題】スタンバイ時のサブスレッショルドリーク電流およびゲートリーク電流を低減させ、スタンバイモードからの復帰時の貫通電流の発生を防ぐことのできる半導体装置を提供する。

【解決手段】クロックゲート信号Gにより出力レベルが固定されるNANDゲート1およびインバータ2〜6と高電位電源線VDDとの間に接続された高閾値のPMOSトランジスタPH1〜PH6、および低電位電源線VSSとの間に接続された高閾値のNMOSトランジスタNH1〜NH6のスイッチングを、スタンバイ制御信号SB1、SB2およびそれぞれの反転信号SB1N、SB2Nで制御する。

(もっと読む)

炭化珪素絶縁ゲート電界効果トランジスタを用いたインバータ回路および論理ゲート回路

【課題】動作速度を高速化できる SiC MISFETで構成された論理ゲート回路デバイスを得る。

【解決手段】nチャネルエンハンスメント型SiC MISFET(22)と、nチャネルデプリーション型SiC MISFET(22、22b)とでインバータ、NAND/NOR論理ゲート回路を構成する。

(もっと読む)

半導体集積回路

【課題】トランジスタの特性ばらつきによる遅延回路の遅延時間の変動を抑制することが可能で、更に、製造工程における加工ばらつきに強く、レイアウト拡張性に優れた半導体集積回路を小面積に提供する。

【解決手段】第1の電源VDDと第2の電源(接地電源)との間に直列に接続されたP型MOSトランジスタMP11と2以上のN型MOSトランジスタMN11、MN12とが備えられる。入力端子INは前記P型MOSトランジスタMP11のゲート端子と前記N型MOSトランジスタMN11、MN12のゲート端子とに接続される。更に、P型MOSトランジスタMP11とN型MOSトランジスタMN11の接点である出力端子OUTに接続した1以上の容量素子C1を有し、P型MOSトランジスタMP11の駆動能力を、2以上に直列接続したN型MOSトランジスタMN11、MN12の総駆動能力よりも大きく構成する。

(もっと読む)

半導体装置

【課題】出力バッファのインピーダンス調整を行う半導体装置を提供する。

【解決手段】制御回路1は、外部からの読み出しまたは書き込みコマンドに応じてDQイネーブル信号を発生する。コマンドラッチ回路2Aは、外部からのコマンド信号(ZQコマンド)に応じて、ZQEnable信号を発生する。ZQ調整回路3は、ZQEnable信号が入力されると、内部に設けられたレプリカ回路のインピーダンス調整を始める。ZQ調整回路3は、DQイネーブル信号が入力される期間中は、インピーダンス調整結果であるドライバコードのDQ回路4への出力を禁止する。

(もっと読む)

半導体装置

【課題】イネーブル信号の伝播時間に変動があっても後段回路に貫通電流を発生させることないSMTセルを有する半導体装置を提供する。

【解決手段】データ保持回路1は、データ保持部11が入力データDを保持し、クロックバッファ部12がデータ保持部11へクロック信号を供給し、低閾値のトランジスタで構成された出力部13と電源線VDDとの間に接続された高閾値のPMOSトランジスタP1および出力部13と接地線との間に接続された高閾値のNMOSトランジスタN1を遮断制御部14が制御し、イネーブル信号Eがイネーブルを示すときは、PMOSトランジスタP1およびNMOSトランジスタN1をともにオンさせ、イネーブル信号Eがディセーブルを示すときは、データ保持部11に保持されたデータの値に応じて、PMOSトランジスタP1あるいはNMOSトランジスタN1のいずれかのみをオフさせる。

(もっと読む)

電源遮断制御回路および電源遮断制御方法

【課題】リーク電流の大きさに基づいた集積回路の電源遮断の制御をする電源遮断制御回路および電源遮断制御方法を提供する。

【解決手段】集積回路の基本回路をモデル化したモデル回路を含むモデル回路部と、前記モデル回路で生じたリーク電流によって充電される出力電圧と予め設定された基準電圧とを比較する電圧比較回路部と、前記比較結果から前記出力電圧が前記基準電圧に達するまでの到達時間を計測し、該計測結果から前記リーク電流の大きさを判定する判定回路部と、前記判定されたリーク電流の大きさに基づいて、前記集積回路の電源遮断を制御する電源遮断制御回路部と、を備える、電源遮断制御回路。

(もっと読む)

半導体装置

【課題】集積回路を構成するMISFETの処理速度の向上とリーク電流の低減を両立させ、かつ、半導体装置の小型化を達成することができる技術を提供する。

【解決手段】単体のMISFETから構成される回路素子に代えて、しきい値電圧の異なる複数のMISFETからなる同一ノードトランジスタから回路素子を構成する。例えば、図2に示すように、nチャネル型MISFET1aとnチャネル型MISFET1bを並列接続しかつ、それぞれのゲート電極Gを電気的に接続する。このとき、例えば、nチャネル型MISFET1aを高VthMISFETから構成し、nチャネル型MISFET1bを低VthMISFETから構成する。

(もっと読む)

半導体装置

【課題】レベル変換の振幅差が大きい場合にも高速に信号レベルを変換する回路を提供することを目的とする。

【解決手段】第1信号を受けて、それよりも大きな振幅の第2信号を出力する差動型レベル変換回路を含む半導体装置であって、前記差動型レベル変換回路は、前記第1信号を受けるための第1MISFET対(MN1-2)と、前記第1MISFET対に対する耐圧緩和のための第2MISFET対(MN3-4)と、出力すべき前記第2信号をラッチするためのものであって、交差結合されたゲートを持つ第3MISFET対(MP1-2)とを有し、前記第2及び第3MISFET対のゲート絶縁膜の膜厚を前記第1MISFET対よりも厚くし、前記第2及び第1MISFET対のしきい値電圧を前記第3MISFET対よりも小さくする。レベル変換の振幅差が4倍以上にも大きいような場合でも、高速なレベル変換が行える。

(もっと読む)

パワーゲーティングCMOS回路及びスーパーカットオフCMOS回路におけるチャージリサイクリング

【課題】MTCMOS回路やSCCMOS回路等のパワーゲーティングされた回路におけるモード移行時のパワー消費の低減や、ウェークアップ時間や、パワーゲーティング構成により生じるノイズを低減する。

【解決手段】第1の回路ブロックと第1のスリープトランジスタとの間の第1の仮想グラウンドノードと、第2の回路ブロックと第2のスリープトランジスタとの間の第2の仮想グラウンドノードと、第1の仮想グラウンドノードを第2の仮想グラウンドノードに接続し、第1の回路ブロックによるアクティブモードからスリープモードへの移行、及び第2の回路ブロックによるスリープモードからアクティブモードへの移行、またはその逆の間に第1の回路ブロックと第2の回路ブロックとの間のチャージリサイクリングを可能とするトランスミッションゲート(TG)またはパストランジスタとを有する回路である。

(もっと読む)

シュミットトリガ回路

【課題】本発明は、単純な構成のシュミットトリガ回路を提供することを目的とする。

【解決手段】シュミットトリガ回路は、第1の入力及び第2の入力が双方ともに第1の入力レベルの時に出力が第1の出力レベルであり、第1の入力及び第2の入力が双方ともに第2の入力レベルの時に出力が第2の出力レベルであり、第1の入力及び第2の入力の一方が第1の入力レベルで他方が第2の入力レベルである時に出力が第1の出力レベルである2入力1出力の論理回路と、共通の入力信号を第1の入力及び第2の入力に入力する際に第1の入力への入力タイミングと第2の入力への入力タイミングとを異ならせる遅延素子とを含み、論理回路の第1の入力に対する第1の閾値電圧と第2の入力に対する第2の閾値電圧とが互いに異なるように構成されていることを特徴とする。

(もっと読む)

半導体記憶装置の出力回路、および半導体記憶装置の出力回路のデータ出力方法

【課題】待機時の漏れ電流の抑制と動作時の低消費電流化をともに実現することができる、半導体記憶装置の出力回路を提供する。

【解決手段】PMOSトランジスタQ11とNMOSトランジスタQ21とが直列に接続されて構成され、メモリセルからの読み出しデータOUTHBを論理反転して、出力用PMOSトランジスタQ51のゲート信号を出力するインバータINV(1)を設ける。そして、待機時には、PMOSトランジスタQ81をONし、インバータINV(1)の回路電源として電源VDD(1.8V)を選択し、出力用PMOSトランジスタQ51のゲートレベルをVDDレベルに設定する。動作時には、NMOSトランジスタQ71をONし、電源VDDQ(1.2V)を選択し、PMOSトランジスタQ51のゲートレベルをVDDQレベルに設定する。

(もっと読む)

信号レベル変換回路、平面表示装置

【課題】 低振幅の入力信号に対しても正常に信号レベル変換が可能であり、動作信頼性が高く、かつ構成が簡素な信号レベル変換回路を提供する。

【解決手段】 互いに同じ極性チャネルのトランジスタであって、低振幅の入力信号INを高振幅の出力信号に変換するための第1及び第2の入力トランジスタ1,2と、第1及び第2の入力トランジスタと同じ極性チャネルのトランジスタであって、電流を供給する第1の電流源15に接続され、入力信号に第1のオフセット電圧を加えて第1の入力トランジスタのゲートに印加する第1のオフセットトランジスタ17と、第1及び第2の入力トランジスタと同じ極性チャネルのトランジスタであって、電流を供給する第2の電流源16に接続され、入力信号に重畳する第1のバイアス電圧VREF’に第2のオフセット電圧を加えて第2の入力トランジスタのゲートに印加する第2のオフセットトランジスタ18とを備える信号レベル変換回路である。

(もっと読む)

半導体集積回路およびその動作方法

【課題】MTCMOSの適用回路の高速起動と非適用回路への影響排除を両立する。

【解決手段】動作停止時にオフし起動時にオンするトランジスタ(パワーゲートトランジスタPGTr)を含み、このトランジスタを介してVss線の一部である第1電源線41に内部回路が接続されている第1回路ブロックCB11と、Vss線の他の一部である第2電源線42に内部回路が直接接続されている第2回路ブロックCB2と、第1,第2電源線41と42間に接続されている電源線スイッチ部SWrcc1と、制御回路(制御回路ブロック2内の一部)とを有する。制御回路は、パワーゲートトランジスタPGTrオンより遅れた開始タイミングで、または、当該オンより長い時間かけて徐々に、第1,第2電源線41と42を接続するように電源線スイッチ部SWrcc1を制御する。

(もっと読む)

半導体装置の出力回路及びこれを備える半導体装置、並びに、出力回路の特性調整方法

【課題】 出力回路のキャリブレーション動作に必要な回路規模及びキャリブレーション動作にかかる時間を低減する。

【解決手段】 データピンDQに接続された第1及び第2の出力バッファ110,120と、キャリブレーション用ピンZQに接続されたキャリブレーション回路130を備える。第1及び第2の出力バッファ110,120は、それぞれ複数の単位バッファ111〜113及び121〜123によって構成されており、各単位バッファは、互いに同一の回路構成を有している。これにより、キャリブレーション回路130を用いたキャリブレーション動作によって、第1及び第2の出力バッファ110,120のインピーダンスを共通に設定することが可能となることから、キャリブレーション動作に必要な回路規模及びキャリブレーション動作にかかる時間を低減することができる。

(もっと読む)

スイッチング回路

【課題】安定したスイッチング特性を有するスイッチング回路を提供する。

【解決手段】コレクタが定電流源11を介して電源Vccに接続され、エミッタが基準電位GNDに接続されたトランジスタ12と、コレクタの電位に基づき、トランジスタ12のゲートに信号を出力してオンとオフを切換え、オフからオンに切り換えるときには、入力電圧Vinがトランジスタ12の閾値電圧Vthより高い第1の電圧V1のときにトランジスタ12を切換え、オンからオフに切り換えるときには、入力電圧Vinがトランジスタ12の閾値電圧Vthより低い第2の電圧V2のときにトランジスタ12を切換えるドライブ手段とを具備する。

(もっと読む)

半導体集積回路装置

【課題】回路動作速度を犠牲にすることなく、待機時の消費電力を小さくすることが可能な半導体集積回路装置を提供する。

【解決手段】同一Si基板上に少なくともソース・ゲート間又はドレイン・ゲート間に流れるトンネル電流の大きさが異なる複数種類のMOSトランジスタを設け、当該複数種類のMOSトランジスタの内、トンネル電流が大きい少なくとも1つのMOSトランジスタで構成された主回路と、トンネル電流が小さい少なくとも1つのMOSトランジスタで構成され、主回路と2つの電源の少なくとも一方の間に挿入した制御回路を有し、制御回路に供給する制御信号で主回路を構成するソース・ゲート間又はドレイン・ゲート間に電流が流れることの許容/不許容を制御し、待機時間中に主回路のINとOUTの論理レベルが異なる際のIN−OUT間リーク電流を防止するスイッチを主回路のIN又はOUTに設ける。

(もっと読む)

半導体集積回路装置

【課題】インバータのレイアウト面積の増加を防止しながら、電源電圧などの電源変動があっても安定して動作させる。

【解決手段】CMOS構成からなるインバータ1は、PチャネルMOSのトランジスタ2,3、およびNチャネルMOSのトランジスタ4からなり、これら電源電圧VCCと基準電位VSSとの間に直列接続されている。これにより、PチャネルMOSトランジスタのON抵抗が大きくなり、電源電圧VCCに依存しないほぼ一定のロジックレベルのインバータを実現することができる。

(もっと読む)

1 - 20 / 42

[ Back to top ]