Fターム[5J065AF01]の内容

Fターム[5J065AF01]の下位に属するFターム

高精度化(信頼性向上) (100)

Fターム[5J065AF01]に分類される特許

1 - 20 / 75

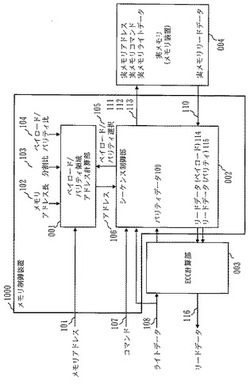

メモリ制御装置

【課題】H/Wの無駄が生じることがなく、高速に処理可能なメモリ制御装置を実現する。

【解決手段】メモリ制御装置1000は、ペイロードをペイロード領域に格納し、パリティデータをパリティ領域に格納する実メモリ004を制御する。ペイロード/パリティ領域アドレス計算部001は、ペイロードとパリティデータのビット数の比をペイロード/パリティ比104として入力し、実メモリ004の領域をペイロード/パリティ比に近似させてペイロード領域とパリティ領域とに分類した結果ペイロード領域に分類される領域の数を分割比103として入力し、実メモリ004のメモリアドレス長102を入力し、ペイロードのメモリアドレス101を入力し、これらを用いて、当該ペイロードに対応するパリティデータのパリティ領域でのメモリアドレスを算出する。

(もっと読む)

誤り訂正処理回路および誤り訂正処理方法

【課題】通信の大容量化を図ること。

【解決手段】誤り訂正処理回路は、入力データ蓄積バッファと、演算器と、出力データ蓄積バッファと、を備えている。入力データ蓄積バッファは、入力されたデータを所定のデータ長ごとに分割する。演算器は、並列に設けられ、入力データ蓄積バッファによって分割された複数のデータに対してそれぞれ誤り訂正の演算を行う。出力データ蓄積バッファは、演算器によって演算が行われた複数のデータを多重する。

(もっと読む)

CRC演算回路

【課題】並列CRC計算を行う場合の回路規模の増大を抑え、かつ、CRC算出を速やかに開始することのできるCRC演算回路を得る。

【解決手段】CRC演算範囲計算回路1は、可変長の入力データのCRC演算範囲を計算する。データ順番調整回路2は、可変長の入力データをNバイト並列に展開した場合、先頭バイト位置を含むデータの演算範囲がNバイト未満の場合、先頭バイト位置より前のデータを0とし、かつ、終了バイト位置を含むデータの演算範囲がNバイト未満の場合は、終了バイト位置より後のデータを0に置き換えると共に、置き換えたデータをNバイトの前側にシフトする。並列CRC計算回路3は、データ順番調整回路2の出力に対してNバイト並列にCRC演算を行う。

(もっと読む)

巡回冗長検査符号生成回路及び巡回冗長検査符号生成方法

【課題】並列データのCRC符号を演算する演算回路において、論理演算回路が1クロックサイクルで行う論理演算の段数を低減する。

【解決手段】巡回冗長検査符号生成回路1は、1個以上の並列データを逐次入力し、各並列データについて、並列データと、初期値又は先行して演算された巡回冗長検査符号と、に基づいて巡回冗長検査符号を算出する所定演算を反復する。巡回冗長検査符号生成回路1は、上記の所定演算を並列データの桁方向に分割した部分演算のそれぞれを、異なるパイプライン段において、初期値と並列データとに基づいて実行する複数の部分演算部200、201と、初期値と前記先行して演算された巡回冗長検査符号とに基づいて、部分演算部200、201によって演算された巡回冗長検査符号を補正する補正部3と、を備える。

(もっと読む)

レート調整装置、レート調整方法及びレート調整プログラム

【課題】処理量及び回路面積の増大を抑制しつつ、レート調整の高速化を図ること。

【解決手段】基本パラメータ算出部121は、レートマッチング処理に用いられる基本パラメータを算出する。先頭パラメータ算出部122は、漸化式を用いて、i番目のブロックの先頭判定値E(i)を順次算出する。ブロック分割部123は、符号化データを複数のブロックに分割する。ビット処理部124−0〜124−nは、基本パラメータ算出部121によって算出された増分値及び減分値と、先頭パラメータ算出部122によって算出されたブロックごとの先頭判定値E(i)とを用いて、パンクチャ又はレペテションの対象となるビットを決定する。ブロック結合部125は、ビット処理部124−0〜124−nによってそれぞれパンクチャ又はレペテションされた各ブロックを結合し、レートが調整された調整データとして出力する。

(もっと読む)

光通信用推定受信機

【課題】更新されたヒストグラムセットの収束時間を短縮できるとともに、最尤系列検出器が出力するデジタルデータの推定誤りを軽減できる光通信用推定受信機を提供する。

【解決手段】ヒストグラムセットに基づき最尤系列推定処理を行うように構成された光通信用推定受信機において、前記ヒストグラムセットに対して所定量の補正を行うヒストグラム補正手段を設けたことを特徴とするもの。

(もっと読む)

符号化装置および方法

【課題】符号化に係る処理を高速化する。

【解決手段】組み合わせ回路253では、(NK)段レジスタ251の上位2pシンボルから逐次qj(x2p)の係数を得て、これらの2p個の係数と生成多項式を乗算した値を、レジスタ出力および新たな2p個の情報シンボルからなる値より減算することによって、次のレジスタ入力値に用いる。レジスタから得られる2pシンボル分の係数qj(x2p)は同時に得られるため、係数と生成多項式の乗算は同時に行なうことができる。本発明は、符号化を行う装置のパリティを生成する回路に適用することができる。

(もっと読む)

バス内のクロストークを低減する方法及び装置、並びにデータワードをコードワードに符号化する方法

【課題】本発明の実施形態は、符号化/復号器(コーデック)を使用して禁止パターンなし(FPF)コードワードを生成する方法を説明する。

【解決手段】まず、本方法は、データワードをフィボナッチ記数法空間にマッピングすることによって、データワードを符号化してFPFコードワードを生成する。さらに、FPFコードワードはバスの隣接するラインを介して送信され、バスから受信されると復号されてデータワードが復元され、バス上のすべてのクロストークがなくなる。

(もっと読む)

記録再生装置および記録再生方法

【課題】LDPC符号の復号器を用いたシステムにとって好適で、リードアフターライトのための記録エラーのブロックの検出をより高速に行うことのできる記録再生装置を提供する。

【解決手段】データ処理部39内のリライト判定モジュール44は、リードアフターライト時にLDPC復号部41より出力されたエラーブロックフラグおよび反復回数に基づいて記録エラーの発生を検出した場合、記録モジュール43に対して、その記録エラーとなったデータをリライトするように制御する。また、データ再生時に過去のリライトによりバッファメモリ23に既に再生データが保持されているブロックと同一のブロックのデータが再度読み出された場合に、エラーブロックフラグおよび反復回数をもとに、リライトされたブロックの再生データでバッファメモリ23上の同一のブロックの再生データを上書きするかどうかを判定する。

(もっと読む)

演算処理装置

【課題】受信データのデータ長によらず高速に演算処理ができる演算処理装置を提供。

【解決手段】受信データ長30に基づいてパラレル演算回数およびシリアル演算回数が演算回数生成部32にて生成され、これら演算回数を制御するためにパラレルイネーブル信号20またはシリアルイネーブル信号16が演算イネーブル生成部40から入力制御部14に与えられると、パラレルイネーブル信号20の入力期間に受信データ12がパラレルにて演算処理部24に入力され、シリアルイネーブル信号16の入力期間に受信データ12がシリアルにて演算処理部24に入力され、演算処理部24ではそれぞれ入力データをパラレル演算処理およびシリアル演算処理をしてその処理結果を出力26に出力する。

(もっと読む)

誤り訂正装置及びデスクランブル回路

【課題】内蔵メモリ容量の増大による回路規模の増大を抑制しつつも、外部メモリへのアクセス量を低減することのできる誤り訂正装置を提供することにある。

【解決手段】デスクランブル回路20は、復調回路からECCクラスタが分割されて格納される内蔵メモリ部から、スクランブルデータsDuが入力されるEOR回路21を備える。デスクランブル回路20は、入力されたスクランブル値を、生成多項式Φ(x)に従って1バイト分シフトさせて新たなスクランブル値を生成する1シフト演算器24と、生成多項式Φ(x)に従って209バイト分シフトさせて新たなスクランブル値を生成する209シフト演算器25とを備える。デスクランブル回路20は、EOR回路21に入力されるスクランブルデータsDuのスクランブル処理時の処理順序に応じて、EOR回路21に出力するスクランブル値を選択する選択回路28及びセレクタ27を備える。

(もっと読む)

エラー訂正処理装置の制御方法

【課題】訂正前データと訂正後データを記憶するメモリの規模を小さくでき、オーバーフローの発生を未然に防止することができるエラー訂正処理装置の制御方法を提供することにある。

【解決手段】訂正処理能力制御回路25は、負荷検出回路37と能力制御回路38を有している。負荷検出回路37はエラー訂正処理回路部24にかかる負荷を検出する。能力制御回路38は、その負荷検出回路37が検出した負荷が大きい場合に、エラー訂正処理回路部24の訂正処理速度を速くする。

(もっと読む)

データ圧縮/伸張と暗号化/復号と誤り制御とを行う統合符号化及び復号装置、並びに方法

【課題】統合的に、圧縮、暗号化及び誤り制御符号化処理することができる統合符号化及び復号装置を提供する。

【解決手段】本発明は、前処理を施した入力情報と予め設計した行列との積をとることにより、情報源符号化、暗号化及び通信路符号化を行って符号語を生成する符号化手段と、情報伝送中に誤りが発生した符号語を受信語として入力して通信路誤り訂正・検出、暗号復号及び圧縮データ伸長を行い復号語を生成する復号手段とからなる。典型的には、符号化手段は、前処理によりエントロピー1未満を有する2元列ベクトルmが生成されていることを前提とし、2元非正則行列Aと2元列ベクトルmとの積をとり、c = A・m の関係により2元符号語cを生成し、復号手段は、非正則行列Aに対する因数分解により得られる線形誤り制御符号の生成行列及び検査行列を用いて、受信語を入力として線形誤り制御符号の復号アルゴリズム及び行列演算を実行して復号語を出力する。

(もっと読む)

通信ネットワークシステムおよび通信方法

【課題】通信の信頼性を確保しつつ、通信資源を有効かつ柔軟に利用できる通信ネットワークシステムおよび通信方法を提供する。

【解決手段】パケット生成手段11は、同一の通信パケットを複数生成する。送信手段12は、パケット生成手段11により生成された複数の上記同一の通信パケットを受信局2に向けて送信する。推定手段21は、送信手段12により送信されてきた上記複数の通信パケットに基づき、所定のアルゴリズムを用いて通信パケットの正しいデータを推定する。訂正手段22は、推定手段21による推定結果に基づいて、受信された通信パケットの誤りを訂正する。

(もっと読む)

受信装置および受信方法

【課題】並列干渉キャンセラの処理遅延を短縮する受信装置を提供すること。

【解決手段】受信装置2は、データ系列を受信する複数の受信アンテナ104A、104Bと、あらかじめ定められた並び替え規則に従って、チャネル推定値の書き込みまたは読み出しの順番を変換するアドレス発生部632と、変換した順番にチャネル推定値を書き込むチャネル推定記憶部634と、並び替え規則に従って、データ系列の書き込みまたは読み出しの順番を変換するアドレス発生部638と、変換した順番にデータ系列を書き込みまたは読み出す信号記憶部639と、チャネル推定値に基づき、データ系列を再変調してレプリカ信号を生成するレプリカ生成部636と、チャネル推定値とデータ系列とを順番に取り出し、チャネル推定値、データ系列およびレプリカ信号を用いて、データ系列の干渉信号をキャンセルしたストリーム信号を生成するキャンセル部642と、ストリーム信号に基づき、誤り訂正復号を行う誤り訂正復号部650とを含む。

(もっと読む)

復調装置および符号化装置、並びに復調方法および符号化方法

【課題】繰り返し復調における通信路値の更新にかかる処理時間の短縮を図る。

【解決手段】繰り返し復号の過程で得られた事後値と尤度とを用いて通信路値を作る通信路値更新部51−1,51−2と、シンボル尤度メモリから読み出された尤度212を通信路値更新部の各々に、該通信路値更新部の使用規則に従って振り分けるDMUX54−1と、繰り返し復号の過程で得られた事後値213を通信路値更新部の各々に、該通信路値更新部の使用規則に従って振り分けるDMUX54−2と、通信路値更新部51−1,51−2の各々で作られた通信路値系列を多重するMUX55とを備える。

(もっと読む)

低密度パリティ検査符号データを復号する復号方法、装置及びプログラム

【課題】低密度パリティ(LDPC)符号データに対するSum-Product復号について、チェックノードの計算量を低減させることにより、復号装置全体の計算量を低減させ、高速で且つ消費電力が小さい復号方法、装置及びプログラムを提供する。

【解決手段】検査行列H(n列m行)を有し、Gallagerの関数f(x)を反復計算するSum-Product復号を用いる。検査行列Hにおけるm行毎の非零の変数ノード集合A(m)の中で、最小の引数xminと、その他の引数xとの距離distanceを算出する。次に、最小の引数xminと、他の複数の引数xとの距離distanceに応じて、閾値dを決定する。距離distanceが閾値d以下となる引数xのみを選択し、変数ノード集合A(m)に対する部分集合C(m)を導出する。その後、変数ノード部分集合C(m)について関数f(x)を反復して、チェックノード処理における対数外部値比αmnを更新する。

(もっと読む)

通信装置、ターボ符号器および通信方法

【課題】従来よりも高速処理が可能でかつ誤り訂正後の誤り率特性の向上を実現可能な通信装置を得ること。

【解決手段】本発明の通信装置は、情報ビット系列を符号化する符号化器101と、インタリーブ処理後の前記情報ビット系列を符号化する符号化器103と、を備えるターボ符号器を採用し、たとえば、前記ターボ符号器が、M×Nの入力バッファ内に前記情報ビット系列を格納し、N−1個のランダム系列を行数分だけ異なるものを用意し、M種類のランダム系列を生成し、さらに、すべてのランダム系列における各行のN個目に最小値をマッピングし、M×Nのマッピングパターンを生成し、前記M×Nのマッピングパターンにインタリーブ長の情報ビット系列をマッピングし、前記マッピング後の情報ビット系列を列単位に読み出し、符号化器103に対して出力するインタリーバ102、を備えることとした。

(もっと読む)

ヘッダ圧縮パケット処理方法及び装置

【課題】圧縮ヘッダのパケットを処理する方法及び装置における、処理効率向上及びメモリ削減を実現できる技術を提供する。

【解決手段】本ヘッダ圧縮パケット通信装置101は、ヘッダ圧縮パケット処理部102、UDP/IPプロトコル処理部103、アプリケーション処理部104、セッション情報記憶部106などを有する。本装置は、圧縮ヘッダをフルヘッダに展開せずに、ヘッダ圧縮パケットの送受信処理を行う。セッション情報記憶部106に、チェックサム計算に係わる固定部チェックサム値を含ませたセッション情報が格納される。固定部チェックサム値は、フルヘッダの固定部情報から計算される。本装置内の各処理部でセッション情報を共用する。

(もっと読む)

ターボ復号器及びターボ復号方法

【課題】ターボ復号の過程で行なわれるインタリーブ処理及びデインタリーブ処理に要するメモリへのアクセス競合の発生を回避する。

【解決手段】複数の要素復号器12−i(i=1〜M)と、それぞれの要素復号結果を行列状メモリ空間において記憶するメモリ部15と、前記行列状メモリ空間において、要素復号器12−i毎に、要素復号結果を異なる行に属するアドレスを書き込み開始アドレスとして当該行又は列方向にそれぞれ書き込んだ後、異なる行に属するアドレスを読み出し開始アドレスとして当該列又は行方向へそれぞれ読み出すメモリ制御部19とをそなえて構成する。

(もっと読む)

1 - 20 / 75

[ Back to top ]