Fターム[5J065AH01]の内容

Fターム[5J065AH01]に分類される特許

81 - 100 / 451

誤り検出訂正方法および半導体メモリ装置

【課題】効率のよい誤り検出訂正方法を提供する。

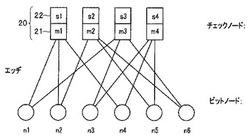

【解決手段】実施形態の誤り検出訂正方法は、低密度パリティ検査符号の検査行列のタナーグラフに対応して設定されたチェックノード20からチェックノード20に接続されている複数のビットノードに向け信頼度αを伝搬する処理と、ビットノードからビットノードに接続されている複数のチェックノード20に向け信頼度βを伝搬する処理と、を繰り返す、サムプロダクトアルゴリズムを用いた復号処理において、チェックノード20が2ビット以上のパリティを備える。

(もっと読む)

送信装置

【課題】LDPC−CCを用いた符号化器及び復号化器において、複数の符号化率を低回路規模で実現し、かつ、高いデータ受信品質を得る。

【解決手段】符号化率設定部250は、符号化率(s−1)/s(s≦z)を設定し、情報生成部210は、情報Xs,iから情報Xz−1,iまでの情報をゼロに設定する。第1情報演算部220−1は、時点iの情報X1,iを入力しX1(D)項を算出し、第2情報演算部220−2は、時点iの情報X2,iを入力しX2(D)項を算出し、第3情報演算部220−3は、時点iの情報X3,iを入力しX3(D)項を算出し、パリティ演算部230は、時点i−1のパリティPi−1を入力しP(D)項を算出し、これら演算結果の排他的論理和を時刻iのパリティPiとして得る。 (もっと読む)

(もっと読む)

送信装置及び送信方法

【課題】LDPC−CCを用いた符号化器及び復号化器において、ターミネーションを行う場合においても、誤り訂正能力を劣化させず、かつ、情報の伝送効率の低下を回避すること。

【解決手段】ターミネーション系列長決定部631は、情報系列の情報長(情報サイズ)及び符号化率に応じて、情報系列の後尾に付加して送信されるターミネーション系列の系列長を決定し、パリティ計算部632は、情報系列、及び、決定されたターミネーション系列長分のターミネーション系列を生成するために必要な既知情報系列に対しLDPC−CC符号化を施し、パリティ系列を計算する。

(もっと読む)

誤り訂正復号装置及び誤り訂正復号方法

【課題】回路を共有化して回路規模の増大を抑えつつ、複数の符号化率に対応したLDPC(Low-Density Parity-Check)復号を行うこと。

【解決手段】設定符号化率が第1の符号化率より符号化率が大きい第2の符号化率の場合、列処理行処理演算部120Aは、第2の符号化率に対応する第2検査行列に応じた分散検査行列から第1の部分行列が構成される列数と同数の列を選択して組み合わせた分散部分行列を用いる。ここで、分散検査行列は、第2検査行列の行数を拡張して、第2検査行列のうち第2検査行列の行重みが大きい行の要素が当該行と拡張した行とに分散して配置された行列である。このとき、列処理行処理演算部120Aは、行重みが第1の部分行列の行重み以下となる分散部分行列を用いる。

(もっと読む)

復号装置および復号方法

【課題】処理量の増加を抑制しながら、復号速度を向上させる技術を提供する。

【解決手段】復調データメモリ32は、CRC符号の付加とLDPCによる符号化とがなされたデータを入力する。LDPC復号部34は、入力したデータに対して、LDCPでの検査行列による復号処理を繰り返し実行する。推定部40は、繰り返し実行される復号処理の各結果に対して、復号の収束の程度を推定する。検査部38は、繰り返し実行される復号処理の各結果に対して、CRC符号によるパリティチェックを実行する。復号制御部42は、ひとつの回の復号処理が終了するごとに、推定した復号の収束の程度と、パリティチェックの結果とをもとに、復号処理を継続させるかあるいは停止させるかを決定する。

(もっと読む)

デジタル伝送方式の復号器及び受信装置

【課題】複数の振幅レベルを有する多様な変調方式に対して、伝送特性を改善する。

【解決手段】復号器(26)は、伝送路を通過した信号から既知情報である伝送信号点配置信号の信号点を抽出する伝送信号点配置信号抽出部(252)と、前記伝送信号点配置信号の信号点を平均化した伝送信号点配置信号の平均点を生成する伝送信号点配置信号平均化部(253)と、前記伝送路を通過した信号を、前記伝送信号点配置信号の平均点を目標集束点として、伝送路で生じる波形歪みを抑圧した適応等化信号を生成する適応等化部(256)と、前記適応等化信号の誤りを訂正する誤り訂正復号部(251)とを備える。

(もっと読む)

誤り訂正復号装置

【課題】復号化器への入力のための信号配線の数を極端に大きくせず、かつ復号化器への入力速度が極端に低速化しないように調整された誤り訂正復号装置、または、復号化器からの出力のための信号配線の数を極端に大きくせず、かつ復号化器の出力速度が極端に低速化しないように調整された誤り訂正復号装置を提供する。

【解決手段】復号化器5は、N個の入力データを並列に復号処理して、K個の復号データを生成する。S/P変換器6は、直列に入力されるN個の入力データを複数回に分けて第1の配線L1〜L64を通じて復号化器5に出力する。P/S変換器7は、復号化器5からK個の復号データを複数回に分けて第2の配線R1〜R60を通じて受けて、K個の復号化データを直列で外部に出力する。

(もっと読む)

符号化方法および符号化装置

【課題】Rate-CompatibleなLDPC(low-density parity-check)符号において、低い符号率と高い符号率の両方で良好なBER性能を有することができるようにする。

【解決手段】符号化部121は、全てのパリティ検査行列が複数の巡回行列から構成される、複数の符号率を有するLDPC符号を符号化する際に、その中で符号率が最低値でない、ある符号の検査行列を構成する巡回行列の最大列重みをw0とし、かつそれよりも低い符号率を有する符号の検査行列を構成する巡回行列の最大列重みをw1とした時、1 < w0かつw1 < w0となるように符号化する。

(もっと読む)

データ処理装置、及びデータ処理方法

【課題】エラーに対する耐性を向上させる。

【解決手段】符号長が4320ビットのLDPC符号がメモリ31のカラム方向に書き込まれ、ロウ方向に読み出される。メモリ31から読み出された2,4又は6ビットの符号ビットは、1シンボルとされ、22個、24個又は26個の信号点にマッピングされる。カラムツイストインターリーバは、LDPC符号の検査行列の任意の1行にある1に対応する複数の符号ビットが、1個のシンボルに含まれないように、LDPC符号の符号ビットを並び替える並び替え処理として、メモリ31のカラム方向に、符号ビットが書き込まれるときの書き始めの位置を、メモリ31のカラムごとに変更するカラムツイストインターリーブを行う。本発明は、例えば、LDPC符号を伝送する場合に適用できる。

(もっと読む)

ソフト・ビット判定を使用してSPSデータのDPSK復調を改善する

【課題】衛星測位システム(SPS)で使用される信号を正確に復調する。

【解決手段】伝送データのワードを含む第一の入力信号を受取るための入力、ワードにおけるビット指数位置に対応する第一のソフト判定情報値の第一の集合を第一の入力信号から取得するために、第一の入力信号に差分位相シフトキー復調を実行する差分位相シフトキー復調器と、さらに第二の入力信号を受取るように構成され、そして差分位相シフトキー復調器はさらに、伝送データのワードにおけるビット指数位置に対応する第二のソフト判定情報値の第二の集合を第二の入力信号から取得するために、第二の入力信号に差分位相シフトキー復調を実行するように構成され、伝送データのワードにおけるそれぞれのビット指数位置に対応する代替ソフト判定情報値の第三の集合を取得するために、対応する第一及び第二のソフト判定情報値の第一及び第二の集合に数学関数を実行するように構成される。

(もっと読む)

データ処理装置、及びデータ処理方法

【課題】データのエラーに対する耐性を向上させる。

【解決手段】LDPCエンコーダ115は、符号長が4320ビットで、符号化率が1/4,1/3,5/12,1/2,7/12,2/3、及び、3/4の7種類のうちのいずれかのLDPC符号による符号化を行う。LDPC符号の検査行列Hは、検査行列Hの、符号長及び符号化率に応じた情報長に対応する情報行列の1の要素の位置を60列ごとに表す検査行列初期値テーブルによって定まる情報行列の1の要素を、列方向に60列ごとの周期で配置して構成される。検査行列初期値テーブルは、例えば、携帯端末向けのディジタル放送用のものになっている。本発明は、LDPC符号化を行う場合に適用できる。

(もっと読む)

データ処理装置、及びデータ処理方法

【課題】エラーに対する耐性を向上させる。

【解決手段】符号長が4320ビットのLDPC符号の2,4又は6ビットの符号ビットが1又は2個のシンボルとされ、24個又は26個の信号点にマッピングされる場合において、カラムツイストインターリーバ24は、LDPC符号の検査行列の任意の1行にある1に対応する複数の符号ビットが、1個のシンボルに含まれないように、LDPC符号の符号ビットを並び替える並び替え処理として、メモリのカラム方向に、符号ビットが書き込まれるときの書き始めの位置を、メモリのカラムごとに変更するカラムツイストインターリーブを行う。本発明は、例えば、LDPC符号を伝送する場合に適用できる。

(もっと読む)

低密度パリティ検査符号の復号装置及び復号方法

【課題】min−sumアルゴリズムの処理サイクル数を少なくすることのできる低密度パリティ検査符号の復号装置及び復号方法を提供する。

【解決手段】本発明の実施形態によれば、行処理演算部3は、検査行列の行ごとに、列処理演算結果が書き込まれるβメモリ2から読み出された列処理演算結果に対して行処理演算を行う。列処理演算部4は、検査行列の列ごとに、行処理演算結果が書き込まれるαメモリ1から読み出された行処理演算結果に対して列処理演算を行う。制御手段5は、検査行列の要素が零ブロックであるか非零ブロックであるかに応じて、αメモリ1およびβメモリ2の読み出しおよび書き込み、ならびに行処理演算部3および列処理演算部4を制御し、前行の行処理演算結果に対する列処理演算と現在行の行処理演算を並行に実行する。

(もっと読む)

符号化装置および符号化プログラム

【課題】従来よりも少ない計算量でパリティを計算することができる符号化装置および符号化プログラムを提供する。

【解決手段】行列記憶部18は、行列Ui、Li(i=1〜m)、Aのデータを記憶する。行列積計算部は、要素数kの情報ベクトルXから式(Y≡U1U2・・・Um-1UmLmLm-1・・・L2L1AX)で表わされるパリティ生成式にしたがって2を法とする演算を行なうことによって、要素数mのパリティベクトルYを生成する。パリティ検査行列Hは、H(X,Y)T=0を満たし、行列Aは、パリティ検査行列Hの第1列目〜第k列目からなり、行列Bは、パリティ検査行列Hの第(k+1)列目〜第n列目からなり、行列Li(i=1〜m)は、行列BをLU分解した下三角行列Lの基本下三角行列であり、行列Ui(i=1〜m)は、行列BをLU分解した上三角行列Uの基本上三角行列である。

(もっと読む)

データ復号システムにおける動的スケーリングのためのシステムおよび方法

【課題】本発明の様々な実施形態は、データ処理のためのシステムおよび方法を提供する。

【解決手段】一例として、デコーダ回路およびスカラ回路を含むデータ処理回路が開示される。デコーダ回路は、少なくとも1つのデコーダ・メッセージを処理することによってデータ復号アルゴリズムを実行するように動作可能であり、スカラ回路は、デコーダ・メッセージに可変スカラ値を掛けるように動作することが可能である。

(もっと読む)

同一チャンネル干渉を最小にするための方法および装置

【課題】通信システムの同一チャンネル干渉を最小にする方法を提供する。

【解決手段】第1のフレームのヘッダ401は第1の特有のワード411、413に基づいてスクランブルされ、第2のフレームのヘッダ401は第2の特有のワード411、413に基づいてスクランブルされる。対応するスクランブルされたヘッダ401を含む第1のフレームと、対応するスクランブルされたヘッダ401を含む第2のフレームがそれぞれ、通信システムの隣接する同一チャンネルによって送信される。各フレームはさらに、ペイロード403とパイロットブロック405を含む。第1のフレームのペイロード403とパイロットブロック405は、第1のスクランブリングシーケンスに基づいてスクランブルされる。第2のフレームのペイロード403とパイロットブロック405は、第2のスクランブリングシーケンスに基づいてスクランブルされる。

(もっと読む)

誤り訂正符号化装置、誤り訂正復号装置、受信装置及び伝送システム

【課題】HD−SDI信号の伝送システムにおいて、HD−SDI信号を識別する。

【解決手段】誤り訂正符号化装置10の誤り訂正符号化対象データ抽出手段102は、HD−SDIデータから符号化対象データを抽出し、誤り訂正符号化手段105は、符号化対象データを短縮化RS符号により符号化し、パリティデータを生成する。誤り訂正パリティ並び替え手段106は、所定の禁止ワードを回避するため、パリティデータ及び識別符号のビット並び替えを行い、並び替えデータを生成する。誤り訂正パリティ挿入手段103は、並び替えデータを、HD−SDI信号の補助データ領域に挿入する。このようにして多重化されたHD−SDI信号は受信装置2へ送信される。受信装置2は、HD−SDI信号の補助データ領域から識別符号を抽出し、識別情報を生成してHD−SDI信号識別情報表示手段209に表示する。

(もっと読む)

符号化装置、復号化装置、符号化・復号化システム、及び、プログラム

【課題】間引き(抽出)処理を行うための計算量を軽減させる。

【解決手段】複数の転送レートRに対応する間引きパターンを規定する間引きテーブルTに基づいてビット順序を予め指定しておき、情報ビット列(情報ビットS1)が入力された場合に、情報ビット列を誤り訂正符号化して誤り訂正符号を生成し、ビット順序に従って、誤り訂正符号の各ビットを順序指定誤り訂正符号ECC1として出力する順序指定誤り訂正符号化部11と、順序指定誤り訂正符号化部から出力される順序指定誤り訂正符号の先頭ビットから間引き転送レート分のビットを抽出して抽出後誤り訂正符号ECC2を生成し、抽出後誤り訂正符号を復号化装置20に出力する符号抽出部12とを備える。

(もっと読む)

符号化装置、および符号化方法

【課題】必要なパラレル度を確保しつつ、符号化回路の構成を簡略化する。

【解決手段】符号化回路51に対しては、1クロックサイクル毎に情報ビットがqビット単位で入力される。入力パラレル変換回路62においては、qビット単位で入力される情報ビットがバッファに蓄積され、蓄積量がmpビットを超えたタイミングで、蓄積された情報ビットのうち、蓄積された順にmpビット分の情報ビットが出力される。パリティ生成回路63においては、mpビット単位で入力された情報ビットに基づいてパリティビットが生成され、qビット単位で出力される。マルチプレクサ64においては、遅延回路61において遅延された情報ビットに、パリティビットが付加されて符号ビットが生成される。本発明は、LDPC符号化を行う装置に適用することができる。

(もっと読む)

データ処理装置、及びデータ処理方法、並びに、受信システム

【課題】データのエラーに対する耐性を向上させる。

【解決手段】符号長が16200ビットで、符号化率が2/3の、DVB-T.2の規格のLDPC符号への符号化を行うLDPCエンコーダ122は、360ビットのデータに、10440ビットのダミーのデータを付加して、10800ビットの情報ビットを生成し、その10800ビットの情報ビットをLDPC符号化することにより、5400ビットのパリティビットを求め、その5400ビットのパリティビットのうちの、360×3ビットを、360ビットのデータのパリティビットとして採用することにより、360ビットのデータを、符号長が360×4ビットで、符号化率が1/4のLDPC符号にLDPC符号化する。本発明は、例えば、LDPC符号を伝送する伝送システム等に適用できる。

(もっと読む)

81 - 100 / 451

[ Back to top ]