Fターム[5J098GA03]の内容

能動素子を用いた回路網 (5,588) | インピーダンスの変換と擬似回路の機能と構成 (102) | インピーダンス回路 (58) | リアクタンス回路 (41)

Fターム[5J098GA03]の下位に属するFターム

誘導性リアクタンス回路 (23)

容量性リアクタンス回路 (13)

Fターム[5J098GA03]に分類される特許

1 - 5 / 5

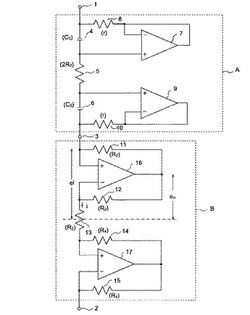

浮動アクティブインダクタ

【課題】回路構成を複雑にすることなしに、そのインダクタンス値及びその内部抵抗値を個別に設定することが可能な浮動アクティブインダクタを提供する。

【解決手段】第1及び第2入力端子1、2間に直列接続された浮動インダクタ回路A及び浮動負性抵抗回路Bと、それらの回路A、Bの直列接続点3を備え、第1及び第2入力端子1、2間に浮動アクティブインダクタが形成されるもので、浮動インダクタ回路Aは、第1入力端子1と直列接続点3間に直列接続された第1キャパシタ4、第1抵抗5、第2キャパシタ6と、第1キャパシタ4の両端に第1低抵抗8を介して接続された第1電圧フォロワ8と、第2キャパシタ6の両端に第2低抵抗を介して接続された第2電圧フォロワ8からなり、浮動負性抵抗回路Bは、直列接続点3と第2入力端子2間に直列接続された第2乃至第6抵抗11〜15と、第2及び第3抵抗11、12に接続された第1オペアンプ16と、第5及び第6抵抗14、15に接続された第2オペアンプ17からなる。

(もっと読む)

浮動アクティブリアクタ

【課題】既知の浮動アクティブリアクタに比べ用いるオペアンプの数が少なく、内部の回路構成を極限まで簡素化した浮動アクティブリアクタを提供する。

【解決手段】第1及び第2入力端子1、2、インピーダンス3(1)〜3(4)をブリッジ接続したブリッジ回路3、電圧フォロワ4、5、低抵抗値の第1及び第2抵抗6、7からなり、ブリッジ回路3の入力端a、cを各別に第1及び第2入力端子1、2に、ブリッジ回路3の出力端b、dを各別に電圧4、5の入力端に、電圧フォロワ4、5の出力端を各別に第1及び第2抵抗6、7を通して第1及び第2入力端子1、2に接続した構成を有し、ブリッジ回路3の相対する一辺に配置するインピーダンスを同種のリアクタ素子で等リアクタンス値の素子に、相対する他辺に配置するインピーダンスを抵抗素子で等抵抗値の素子に選び、第1及び第2入力端子1、2に信号電圧の供給時、第1及び第2入力端子1、2間に浮動アクティブリアクタが形成される。

(もっと読む)

インピーダンス変換回路及びそれを用いた電力増幅装置

【課題】複数の周波数帯のインピーダンス条件に対するインピーダンス変換を低損失に行なうことができるようにする。

【解決手段】インピーダンス変換回路10Aは、入力された高周波信号の位相を調整する位相調整用伝送線路4と、その出力側に接続された第1のスイッチ素子6Aと、該第1のスイッチ素子6Aの出力側に設けられ、高周波信号を第1の高周波信号として出力する第1の出力端子7Aと、位相調整用伝送線路4の出力側に接続され、高周波信号を反射可能な第1の反射量調整用伝送線路5と、その出力側に接続された第2のスイッチ素子6Bと、該第2のスイッチ素子6Bの出力側に設けられ、高周波信号を第2の高周波信号として出力する第2の出力端子7Bとを有している。第1のスイッチ素子6A及び第2のスイッチ素子のbうちの一方がオン状態とされる。

(もっと読む)

負荷回路及びこれを用いた同調回路

【課題】同調回路の同調周波数を大きく変化させても、同調周波数に対し負性抵抗の値を調整する回路が不要で、かつ常に帯域一定で利得一定の特性を持つ同調回路に用いる負荷回路を提供する。

【解決手段】同調回路に用いる本発明の負荷回路10は、インダクタ14と、上記インダクタ14に直列に接続され、上記インダクタ14の直列抵抗成分を打ち消し、インダクタのQを増大させるための負性抵抗回路12とを備える。上記構成の上記負荷回路10を用いて同調回路を構成すると、インダクタ14のもつQよりも、Qの高い同調回路が実現でき、かつ同調周波数を大きく変化させても、常に一定の帯域で利得一定の特性を持つ同調回路を構成できる。

(もっと読む)

同調制御装置

複数の入力印加信号に対する依存性を有する出力リアクタンスを有し、前記印加信号の一つが入力同調信号であるところの共振回路の同調構成は、その出力リアクタンスが前記共振回路の共振周波数を制御する回路網に接続され、各同調回路が制御入力を有すると共に前記制御入力に印加される制御信号の値に依存して変化するリアクタンスを有する同調回路のアレイと、前記同調回路の制御入力に印加する複数の異なる制御信号を生成する手段を備える。各制御信号は、その制御信号に固有の所定範囲にわたって前記入力同調信号と実質的に線形的に変化し、それにより前記入力同調信号に対する前記共振回路の周波数応答は入力同調信号の所望の範囲にわたって実質的に線形となる。前記同調回路は、好ましくはMOSバラクターのような可変リアクタンス要素であり、制御信号は高次の成分を制御するために印加される。  (もっと読む)

(もっと読む)

1 - 5 / 5

[ Back to top ]