Fターム[5J500AC31]の内容

Fターム[5J500AC31]に分類される特許

1 - 17 / 17

差動増幅器

【課題】非反転入力端子の電圧が変化した場合でも、出力トランジスタに流れる電流を一定にすることができる、差動増幅器を提供する。

【解決手段】非反転入力端子143と、反転入力端子144と、P型MOSトランジスタ107及び108とN型MOSトランジスタ101及び102と定電流源121とからなる差動増幅回路と、P型MOSトランジスタ103及び104とN型MOSトランジスタ113及び114と定電流源122とからなる差動増幅回路と、P型MOSトランジスタ107及び108に電流を流す定電流源124とで構成される相補型フォールデッドカスコード増幅回路に、さらにP型MOSトランジスタ107及び108に電流を流す電流制御回路である、定電流源123とN型MOSトランジスタ105を備え、相補型差動対の負荷であるカスコード増幅回路に流れる電流を、非反転入力端子の電圧によって制御する構成とした。

(もっと読む)

帰還線の分散制御を備えるトランスインピーダンス増幅器

装置は、電子増幅器および電気的帰還線、複数の電気的ソース、ならびに電子コントローラを含む。電気的帰還線は、電子増幅器の出力をその入力に接続する。電気的ソースは、電気的帰還線上のノードに接続する。電子コントローラは、電気的帰還線に入力される電流に応答する形で電気的ソースを調節するように構成される。  (もっと読む)

(もっと読む)

信号増幅装置、及び磁気センサ装置

【課題】磁気センサ等の微少な検出対象信号を入力信号とする信号増幅装置において、入力信号のオフセットが大きいため、ダイナミックレンジを確保できない。

【解決手段】差動入力信号の一方を入力される増幅部30と、他方を入力される増幅部32と、増幅部30,32から得られる差動出力信号の中点電位を検出して当該差動出力信号のオフセット電位をフィードバック制御するコモンモード検出回路28とを備える。増幅部30,32は差動増幅回路34a,34bから出力される中間差動信号をドライバ回路38a,38bに印加するバイアス信号に変換するバイアス回路36a,36bを有する。バイアス回路36a,36bは、コモンモード検出回路28からの制御信号に応じて抵抗値が変化する抵抗可変素子を有し、分圧比を調節してバイアス信号を調節する。

(もっと読む)

前置増幅器

【課題】光受信器における前置増幅回路においては、PDの電流の一部をバイパスして増幅回路の過大入力を防止する必要があるが、このような目的で付加されるバイパス回路は抵抗およびトランジスタなどの能動素子もしくはダイオードなどの非線形素子を用いて構成されているため、信号帯域内における周波数平坦性が損なわれてしまうという問題点があった。

【解決手段】電流信号と、上記電流信号が片側の入力端子に入力される差動増幅器と、上記差動増幅器のもう一方の入力端子に接続され差動増幅器の閾値電圧を発生させる閾値電圧発生手段とからなる前置増幅器において、上記差動増幅器と上記閾値電圧発生手段との間に、2つ以上の異なった時定数をもつ多重フィルタ回路を接続した。

(もっと読む)

半導体装置

【課題】増幅回路の利得を補償するためにGm補償バイアス電圧を与えても、増幅回路の出力電流電圧の変動が少なく、出力信号の歪み特性が良好な半導体装置を提供する。

【解決手段】半導体装置において、利得制御回路と、前記利得制御回路により利得が一定に制御された第1の回路と、前記第1の回路に対するバイアス回路とを備え、前記第1の回路は、第1のトランジスタと負荷抵抗とを有し、前記第1の回路の増幅率又は減衰率は前記第1のトランジスタの相互コンダクタンスと前記負荷抵抗の抵抗値との積に比例し、前記負荷抵抗に印加される電圧を前記半導体装置の出力とし、前記バイアス回路は、前記第1のトランジスタに流れるドレイン電流に比例した電流と前記負荷抵抗値に反比例した電流との差分電流を生成して出力し、前記バイアス回路の出力は前記第1の回路の出力ノードに接続される。

(もっと読む)

電圧−電流コンバータ及びこれを備えたオーディオアンプ

【課題】負荷が平衡又は不平衡にかかわらず安定した電流を負荷に供給する。

【解決手段】本願発明の電圧−電流コンバータは、平衡入力される電圧信号を電流信号に変換し、負荷Lが接続される一対の出力端の一方から出力するための第1の電流−電圧変換部3と、電圧信号の位相を反転した電圧信号を電流信号に変換し、一対の出力端の他方から出力するための第2の電流−電圧変換部4と、一対の出力端間の電圧に含まれる、第1の電流−電圧変換部3及び第2の電流−電圧変換部4の出力に含まれるコモンモード成分に応じた電圧成分を第1の電流−電圧変換部3及び第2の電流−電圧変換部4の各入力端側にそれぞれ帰還させる帰還部5とを備える。

(もっと読む)

半導体回路

【課題】従来の差動クロック信号を多段でバッファリングする回路では、自身の構成するトランジスタのバラツキにより生じるデューティ比の劣化等の補正がされなかった。また、できるだけデューティ補正効果を大きくしようとすると、回路規模やそれに伴う消費電流が大きくなってしまう。

【解決手段】本発明にかかる半導体回路は、入力差動信号が入力される差動入力部と、前記差動入力部に入力される電圧に応じて、出力差動信号を出力する差動信号出力端子と、前記差動信号出力端子から出力された信号の直流成分を抽出するローパスフィルタと、前記差動入力部に接続され前記ローパスフィルタが抽出した信号の直流成分に基づいて、抵抗値が設定される負荷抵抗部とを有する。

(もっと読む)

ドライバ回路

【課題】 従来のドライバ回路では、CML回路の出力振幅や中点電圧等の出力電圧を制御することが困難であった。さらに、従来のドライバ回路では、CML回路における出力電圧のハイレベルが電源電圧からドロップしていた。

【解決手段】 ドライバ回路は、差動入力信号の振幅を変換して差動出力信号を出力する振幅変換部と、前記差動出力信号の振幅を設定する振幅設定部と、前記差動出力信号の振幅の中心値を設定するコモン電圧設定部とを有する。

(もっと読む)

増幅回路、及び、ビデオアンプ

【課題】入力信号を、所定の直流バイアス電圧で、かつ、所定のゲインとなるように増幅する増幅回路及びビデオアンプに関し、入力信号を、所定の直流バイアス、かつ、所定のゲインで増幅できる増幅回路を提供することを目的とする。

【解決手段】本発明は、入力信号を、所定の直流バイアス電圧で、かつ、所定のゲインとなるように増幅する増幅回路であって、入力信号を増幅する第1の増幅回路(112)と、第1の増幅回路(112)の出力信号を増幅する第2の増幅回路(113)とを有し、第1の増幅回路(112)は入力信号の直流バイアス電圧が所定の直流バイアス電圧となる第1のゲインで増幅し、第2の増幅回路(113)は所定の直流バイアス電圧でバイアスされており、入力信号に対するゲインを所定のゲインとする第2のゲインで増幅することを特徴とする。

(もっと読む)

多段差動増幅器

【課題】高出力増幅器のような高飽和特性が要求される差動増幅器において、入力信号の同相成分を除去する機能を改善し、差動利得特性の劣化を防止する。

【解決手段】半導体増幅素子から構成されるエミッタ接地形多段差動増幅器において、少なくとも最前段増幅器の入力バイアス回路には該増幅器を構成する半導体増幅素子の入力インピーダンスの絶対値の1/2以上のインピーダンスを有するフィード素子を用いる。

(もっと読む)

入力コモンモードフィードバックを用いた光学検出器におけるダミー検出器の排除

参照電圧は増幅器への入力において定電圧を印加する。その結果、増幅器の非アクティブな入力上のダミー検出器の必要性を排除する。  (もっと読む)

(もっと読む)

光通信装置

【課題】光パケット通信のような常にマーク率変動があるような信号でもシステムでの光信号の認識に使用できるような、PD−TIAのモジュールを提供する。

【解決手段】光信号を電流信号に変換する光電変換素子と、該光電変換素子に接続され、前記電流信号を電圧信号に変換する電流/電圧変換手段と、該電流/電圧変換手段で電圧変換された電気信号を入力し増幅すると共にこの増幅した電気信号を所定の閾値と比較して0又は1の信号を出力するリミッティングアンプを具備した。

(もっと読む)

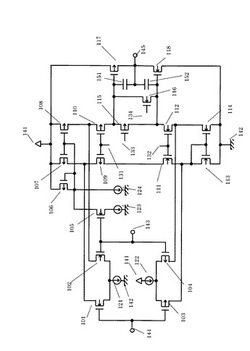

差動増幅回路、レシーバ回路、発振回路及びドライバ回路

【課題】立ち上がり時の遅延時間と立下り時の遅延時間との差を小さくすることができる差動増幅回路と、これを用いたレシーバ回路、発振回路及びドライバ回路を提供する。

【解決手段】差動入力信号の極性が正負の何れに変化する場合でも、ノードN31及びN32bに発生するバイアス電圧がほぼ一定になり、各カスコード部のNチャンネル側の負荷トランジスタ(MN21,MN22,MN21b,MN22b)には常に電流が流れた状態になる。これにより、ノードN31及びN32bの充放電に要する時間が非常に短くなるため、非反転出力信号O(+)及び反転出力信号O(−)の立ち上がり時の遅延時間と立下り時の遅延時間をほぼ等しくすることができる。これにより、入力信号のパルス幅と出力信号のパルス幅がほぼ同じになり、高速な回路への適用が可能になる。

(もっと読む)

交流増幅器及び圧電振電子発振器

【課題】

交流増幅器の低電圧動作を損なうことなく、消費電流を低減でき、かつ出力信号波形のデュティーのずれが少なく、更に十分な増幅特性を有する交流増幅器を提供する。

【解決手段】 連結配線Ndで結ばれた増幅回路AP1とバイアス回路VS1を有し、バイアス回路VS1は前記連結配線Ndを介して前記増幅回路AP1の前記交流信号を入力し、増幅回路AP1の交流信号の振幅に応じたバイアス回路VS1の直流電圧を連結配線Ndを介して増幅回路AP1へ供給する交流増幅器とした。

(もっと読む)

半導体装置

【課題】DCオフセットの除去及びゲイン制御を可能とし、カットオフ周波数を上昇し、動作周波数帯域制限を緩和する。

【解決手段】入力端子101と、VDDとGNDとの間に、バイアス電流供給回路102と、PMOSトランジスタ103と、NMOSトランジスタ104及びNMOSトランジスタ105を直列に接続し、NMOSトランジスタ105のゲートに最適電圧を供給するDCオフセット補正回路106とからなるCMOSインバータ回路107を有し、PMOSトランジスタ103のドレインとNMOSトランジスタ104のドレインの接続点と、ゲートに制御電圧Vg1が供給されるNMOSトランジスタ113と、ゲートに制御電圧Vg2が供給されソースがNMOSトランジスタ113のドレインに接続されたNMOSトランジスタ111とからなるゲート接地回路115のNMOSトランジスタ113ドレインとNMOSトランジスタ114ソースの接続点との間にコンデンサ108が接続された回路構成とする。

(もっと読む)

差動出力ドライバ及びこれを備えた半導体装置

【課題】差動出力ドライバ及びこれを備えた半導体装置を公開する。

【解決手段】この回路は、差動出力部(12)と、第1ドライバ(N1)に並列に接続され、第1制御信号(con2)に応答して第1ドライバの駆動能力を変化させる反転出力信号駆動可変部(N3−1・・・N3−n)と、第2ドライバ(N2)に並列に接続され、第2制御信号(con1)に応答して第2ドライバの駆動能力を変化させる出力信号駆動可変部(N4−1・・・N4−n)を備えるドライバと、反転出力信号(DQB)及び出力信号(DQ)のそれぞれと基準電圧(VREF)との間の電圧差を検出し、電圧差に基づいてエラー平均値を発生し、エラー平均値によって前記第1及び第2制御信号を発生する制御部とで構成されている。よって、工程、電圧及び温度の変化によって素子の値に変化が発生しても反転出力信号と出力信号との間のスイング幅を所望の範囲内で作ることができる。

(もっと読む)

差動増幅回路

【課題】線路間の結合を抑制しバランスのとれた差動動作を実現させることができる差動増幅回路を得る。

【解決手段】入力電圧の差を増幅して出力する1対のトランジスタ53,54を備え、各トランジスタのコレクタまたはベース端子が少なくとも線路を用いて接続され、接続された後の電源端子60,64までが少なくとも他の線路を用いて接続されている差動増幅回路において、各トランジスタのコレクタまたはベース端子が接続されるまでの線路の線路幅を、接続された後の電源端子までの他の線路の線路幅よりも太くした。

(もっと読む)

1 - 17 / 17

[ Back to top ]