Fターム[5J500AC93]の内容

増幅器一般 (93,357) | 目的、効果 (9,357) | 回路の簡素化、小型軽量化 (745) | コンデンサの不要化 (39)

Fターム[5J500AC93]に分類される特許

1 - 20 / 39

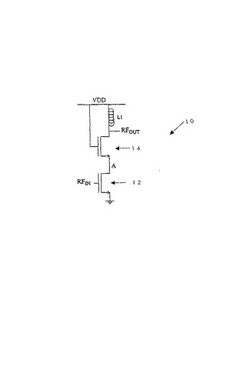

集積されたパワー増幅器を有するCMOSトランシーバ

【課題】通信信号を増幅する絶縁破壊に耐えるトランジスタ構造を提供する。

【解決手段】入力無線周波数信号を受信するため接地点と第1のゲートに接続されたソースを有する第1のNMOSトランジスタ12は、第1のトランスコンダクタンスと第1の破壊電圧とを有する。また第2のNMOSトランジスタは、第1のNMOSトランジスタのドレインに接続されたソースと、基準DC電圧に接続されたゲートと、増幅された無線信号の出力を与えるドレインと、基準DC電圧と第2のNMOSトランジスタのドレインとの間に配置された負荷とを有する。第2のNMOSトランジスタ14は第2のトランスコンダクタンスと第2の破壊電圧とを有し、第2の絶縁体は第1の絶縁体よりも厚い。この結果、第1のトランスコンダクタンスは第2のトランスコンダクタンスよりも大きく、第2の破壊電圧は第1の破壊電圧よりも大きい。

(もっと読む)

発振装置及び電子機器

【課題】D級アンプにより駆動し、かつ圧電素子を利用した発振装置において、ローパスフィルタを設けることにより発振装置が大型化することを抑制する。

【解決手段】この発振装置は、振動部材10及び圧電素子20からなる圧電振動子、及びインダクタ52を備え、D級アンプ(制御部50)により振動部材10に駆動信号が入力される。そして圧電振動子の静電容量、及びインダクタ52により、ローパスフィルタが構成される。このローパスフィルタは、制御部50からの駆動信号と同一周波数成分を除去する。

(もっと読む)

増幅装置及び信号の増幅方法

【課題】増幅装置及び信号の増幅方法を提供する。

【解決手段】増幅装置は、信号入力(31)と、帰還入力(32)と、信号出力(33)とを備えた増幅器(3)を有する。第1の結合路(FB1)は、第1のインピーダンス素子(R1)を備え、帰還入力(32)を信号出力(33)に接続する。第2の結合路(FB2)は、直列に接続したフィルタ装置(4)と、バッファ回路(5)と、第2のインピーダンス素子(R2)を有し、帰還入力(32)を信号出力(33)または信号入力(31)に接続する。

(もっと読む)

バイアス回路

【課題】バイアス回路を組み込んだ通信機器や電子機器の小型化を促進させるため、1つのチップにて構成することができるバイアス回路を提供する。

【解決手段】RFチョークとバイパスコンデンサとを有するバイアス回路において、少なくとも下面もしくはその内部にグランド電極40が形成された誘電体基板30と、前記誘電体基板30の表面に形成された入力端子32及び出力端子34と、前記誘電体基板30内もしくは表面に形成され、一端が前記入力端子32に接続され、且つ、他端が前記出力端子34に接続され、前記RFチョークを形成するRFチョーク形成電極36と、前記誘電体基板30内に、前記グランド電極40に対向して形成され、且つ、一端が前記出力端子34に接続され、前記バイパスコンデンサを形成するためのコンデンサ形成電極38とを有する。

(もっと読む)

自動オフセット消去回路

【課題】外付け容量が不要な自動オフセット消去回路を提供する。

【解決手段】自動オフセット消去回路は、主信号を低域ろ波するローパスフィルタ2と、ローパスフィルタ2の出力信号のDC電位を昇圧するアンプ1と、アンプ1の出力信号を低域ろ波して出力信号を主信号系のアンプに負帰還させるローパスフィルタ3とを備える。ローパスフィルタ3は、一端がアンプ1の出力端子に接続された抵抗rd1,rd2と、抵抗rd1,rd2の出力側の端子と接地との間に挿入された容量cd3,cd4と、抵抗rd1,rd2の出力側の端子に接続されたミラー増倍容量とから構成される。ミラー増倍容量は、入力端子が抵抗rd1,rd2の出力側の端子に接続された容量増倍用アンプと、容量増倍用アンプの入力端子と出力端子との間に設けられた容量cd1,cd2とから構成される。

(もっと読む)

時定数調整回路

【課題】参照用の時定数発生回路を集積回路の外部に用意すると、集積回路の端子数の増加および半導体チップ面積の増大を招き、その結果、製造コストが増大してしまう。また、集積回路単体では時定数の調整を行えない。

【解決手段】スイッチトキャパシタを用いることで、時定数発生回路を集積回路に内蔵しても十分な精度が保たれる。さらに、時定数の補正結果を記憶する記憶部を設けることで、時定数調整用回路と、時定数調整後の通常動作用回路を、一部兼用することが可能となる。集積回路の端子数と、半導体チップ面積を節約でき、その結果、製造コストを抑えられる。さらに、外部から電源さえ供給されれば、自動的かつ自律的に時定数の調整を行える。

(もっと読む)

光受信器

【課題】帰還抵抗を極端に大きくすることなく、高感度に広帯域な動作を実現できる光受信器を提供する。

【解決手段】同一極性方向に直列接続された2個の受光素子より構成されたバランスドフォトダイオードと、このバランスドフォトダイオードの出力信号が入力されるチェリーホッパー型増幅部と、このチェリーホッパー型増幅部を構成している差動入力ペアトランジスタからのそれぞれの出力信号をレベルシフトするエミッタフォロワ部と、このエミッタフォロワ部の出力信号を前記チェリーホッパー型増幅部の各入力端子に帰還する経路に設けられた第1および第2の帰還抵抗と、この第2の帰還抵抗と前記チェリーホッパー型増幅部を構成している差動増幅回路の一方のトランジスタのベースに接続されている第1のコンデンサとを有することを特徴とする。

(もっと読む)

E/F級スイッチング電力増幅器

【課題】E級と逆F級のハイブリッド回路を用いて高効率な電力増幅器を提供する。

【解決手段】「E/F級増幅器」と呼ばれる、新たな分類のスイッチング増幅器は、選択された調波でF-1級のインピーダンスと、それら以外の調波でE級のインピーダンスを配備することによって、電圧と電流の改良された波形のための負荷ネットワークと共に、ゼロ電圧スイッチング(ZVS)位相補正技術を用いて、E級増幅器で利用されるスイッチングデバイスの固有キャパシタンスに通常関連した損失を取り除く。

(もっと読む)

D級増幅回路

【課題】 フィルタレス等を好適に実現可能なD級増幅回路を提供する。

【解決手段】 D級増幅回路は、第1パルス幅変調信号(Pa)と第2パルス幅変調信号(Pb)とを同時に生成する。この場合、第2パルス幅変調信号中の幅狭パルス信号の立上り時点は、第1パルス幅変調信号中の幅広パルス信号の立上り時点よりも遅れ、その立下り時点は、当該幅広パルス信号の立下り時点よりも早い。他方、第1パルス幅変調信号中の幅狭パルス信号の立上り時点は、前記第2パルス幅変調信号中の幅広パルス信号の立上り時点よりも遅れ、その立下り時点は、当該幅広パルス信号の立下り時点よりも早い。これにより、出力信号(OUT)は、プラス側に突出する2本のパルス、マイナス側に突出する2本のパルス、が交互に繰り返される信号となる。

(もっと読む)

PWM処理方法および処理回路

【課題】ローパスフィルタを全く使用することなく、入力された2レベルのPWM信号から、3レベルのBTL用等のPWM信号を発生させる。

【解決手段】2レベルのPWM信号を入力して、クロック信号に同期させた同期PWM信号を得るとともに、2レベルのPWM信号の正又は負の一方の極性のエッジを検出したエッジ検出信号を得る。同期PWM信号をn段の第1のシフトレジスタに入力して、クロック信号に同期させて後段にシフトさせる。先のエッジ検出信号と次のエッジ検出信号の間の記同期PWM信号を時間軸反転且つ論理反転し、n段の第2のシフトレジスタの初段から順にセットしてから、記クロック信号に同期させて後段にシフトさせる。第1のシフトレジスタの出力PWM信号と第2のシフトレジスタの出力PWM信号の差分をとることで2レベルのPWM信号に応じた3レベルのPWM信号を得る。

(もっと読む)

電力増幅装置

【課題】デジタル電力増幅器を用いて電力増幅する際、平滑フィルタの次数を低くすることができると共に高精度な駆動信号を得ることが可能な電力増幅装置を提供する。

【解決手段】複数の変調信号PWM1、PWM2の1つをレベルシフトし、それらの変調信号PWM1、PWM2を該当するブートストラップ回路32付きのデジタル電力増幅器27a、27bの夫々で電力増幅し、電力増幅された電力増幅変調信号APWM1、APWM2を平滑化して駆動信号COMを出力するにあたり、電力増幅変調信号APWMの到達電位のステップ間の電位差が小さくなり、変調信号の周波数成分を除去するための平滑フィルタ29の次数を低くすることができると共に、レベルシフト回路33やデジタル電力増幅器27a、27bで生じる信号伝播遅延時間Δt1、Δt2の差を遅延回路34a、34bで調整して駆動信号COMを高精度化することができる。

(もっと読む)

光受信増幅器

【課題】大容量の直流成分排除用コンデンサを不要にして受信器全体の小型化を図り、トランスインピーダンスアンプとリミッタアンプを1チップ集積化にすることを可能にするとともに、差動リミッタアンプの出力波形を高精度に対称にできる光受信増幅器を提供することを目的とする。

【解決手段】フォトダイオードと、このフォトダイオードの出力信号を増幅するトランスインピーダンスアンプと、このトランスインピーダンスアンプと並列に接続され、トランスインピーダンスアンプの出力電流の直流電流成分を補償する直流電流補償回路、とを含むことを特徴とするもの。

(もっと読む)

光受信器

【課題】バランスド受光入力に対応し、シングル−差動変換に対するリファレンス電圧の調整が不要で、トランスインピーダンスアンプの出力とリミッタアンプの入力を接続するための広帯域な信号に対応した大容量のコンデンサも不要な光受信器を提供すること。

【解決手段】同一極性方向に直列接続された2個の受光素子より構成された2方向の電流を有するバランスドフォトダイオードと、このバランスドフォトダイオードの出力信号が差動入力ペアトランジスタの一方のトランジスタのベースに入力される差動増幅部と、この差動増幅部のそれぞれの出力信号をレベルシフトするエミッタフォロワ部と、このエミッタフォロワ部の出力信号を前記差動増幅部の各入力端子にそれぞれ帰還する帰還抵抗と、前記差動入力ペアトランジスタの他方のトランジスタのベースに接続されているコンデンサ、とで構成されたことを特徴とする光受信器。

(もっと読む)

半導体集積回路装置及びオフセットキャンセル設定システム

【課題】本発明は、縦続接続された増幅回路の段間のカップリングコンデンサをなくしオフセットキャンセルを行う半導体集積回路装置及びオフセットキャンセル設定システムを提供することを目的とする。

【解決手段】縦続接続される複数の増幅回路を搭載した半導体集積回路装置において、発生したキャンセル電圧と最終段直前の増幅回路の出力信号を加算して最終段の増幅回路に供給するオフセットキャンセル回路を有する。

(もっと読む)

半導体集積回路及びコンデンサ・マイクロフォン

【課題】キャパシタを集積化するとともに、高ESD耐圧を実現する。

【解決手段】本発明の一態様に係る半導体集積回路10は、コンデンサ・マイクロフォン用の半導体集積回路であって、出力トランジスタMN1のドレインと端子Bとの間に直列に接続された抵抗R5、抵抗R6と、出力トランジスタMN1のソースと接続された端子Cと、抵抗R5と抵抗R6との接続点n4と端子Cとの間に設けられたキャパシタC1と、キャパシタC1と並列に接続されたダイオードD3とを備える。

(もっと読む)

高周波増幅装置

【課題】小型で製造が容易な高周波増幅装置を提供する。

【解決手段】電源電位Vccと接地電位GNDとの間に接続され、入力された高周波信号f1を増幅して出力信号f2として出力する高周波増幅装置1において、増幅用トランジスタT1と、負荷用トランジスタT2とを直列に設ける。増幅用トランジスタT1のコレクタは電源電位Vccに接続され、ベースに高周波信号f1が入力され、エミッタは負荷用トランジスタT2のコレクタに接続される。また、負荷用トランジスタT2のエミッタは接地電位GNDに接続される。そして、増幅用トランジスタT1のコレクタから出力信号f1が取り出される。負荷用トランジスタT2の寄生抵抗及び寄生容量によって、抵抗素子及びキャパシタを設けた場合と同様な効果が得られる。

(もっと読む)

スイッチングアンプ

【課題】出力側をフィルタレスとすることを前提に、回路規模を縮小化したスイッチングアンプを提供する。

【解決手段】1フレーム期間内の基準信号として半フレームは第1のランプ波を生成し他の半フレームは前記第1のランプ波の次に続く第2のランプ波を生成するランプ波発生器21を具え、信号基準レベルを中心として上下レベルを相補的に交互に推移する二種類のレベル信号のうち片方のレベル信号と第1及び第2のランプ波とを比較する第1の比較器22と、他の片方のレベル信号と第1及び第2のランプ波とを比較する第2の比較器23とを具え、比較器22、23の出力信号を次の第2のランプ波まで持続させて、あたかも従来の三角波の比較器出力と同等のパルス幅変調信号PG、NGを得るパルス幅変調信号生成器24を有する。

(もっと読む)

スピーカ用駆動装置及びスイッチングアンプ

【課題】3線出力増幅器を用い、チャネル間の信号干渉を抑えて、かつ小型化に有利なスピーカ用駆動装置及びこのスピーカ用駆動装置を用いたスイッチングアンプを提供することを目的とする

【解決手段】端子46、47を有する負荷L1、負荷L1の端子46に接続される端子140を有する増幅器10、端子48、49を有する負荷L2、負荷L2の端子48に接続される端子340を有する増幅器30、負荷L1の端子47と負荷L2の端子49とに接続される端子240を有する第増幅器20、端子140と端子240との間に接続されるトランジスタ101、102と、端子240と端子340との間に接続されるトランジスタ103、104と、を備え、増幅器10、増幅器20、トランジスタ101、102が第1ブリッジ増幅器を構成し、増幅器30、増幅器20、トランジスタ103、104が第2ブリッジ増幅器を構成する。

(もっと読む)

増幅回路及びこれを備える光ピックアップ

【課題】ゼロ点調整による位相補償と進み位相補償とを1つのキャパシタで実現し、回路規模を削減可能な増幅回路を提供する。

【解決手段】本発明による増幅回路は、入力信号が供給される差動増幅回路20と、差動増幅回路20の出力を受けるソースフォロア回路30と、ソースフォロア回路30の出力端と差動増幅回路20の入力端とを接続する帰還抵抗16と、差動増幅回路20の出力端及びソースフォロア回路30の入力端の間と、帰還抵抗16と差動増幅回路20の入力端の間と、に接続されたキャパシタ17と、を備えることを特徴とする。キャパシタ17は、ゼロ点調整による位相補償と進み位相補償の両方を実現する。したがって、回路規模の削減が実現される。

(もっと読む)

増幅装置及び信号の増幅方法

【課題】増幅装置及び信号の増幅方法を提供する。

【解決手段】増幅装置は、信号入力(31)と、帰還入力(32)と、信号出力(33)とを備えた増幅器(3)を有する。第1の結合路(FB1)は、第1のインピーダンス素子(R1)を備え、帰還入力(32)を信号出力(33)に接続する。第2の結合路(FB2)は、直列に接続したフィルタ装置(4)と、バッファ回路(5)と、第2のインピーダンス素子(R2)を有し、帰還入力(32)を信号出力(33)または信号入力(31)に接続する。

(もっと読む)

1 - 20 / 39

[ Back to top ]