Fターム[5J500AS11]の内容

Fターム[5J500AS11]に分類される特許

1 - 15 / 15

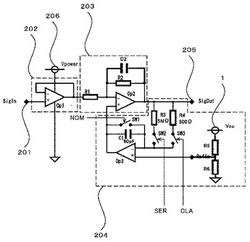

信号処理装置

【課題】 抵抗及び小さな静電容量を用いた回路により、検出素子の出力信号を直流成分を除いて増幅する小型な信号処理装置を得る。

【解決手段】 入力信号が第1のインピーダンスを介して反転入力端子に入力される第1のオペアンプと、第1のオペアンプの反転入力端子と出力端子とに接続された第2のインピーダンスと、基準電圧が非反転入力端子に入力され、出力端子が第1のオペアンプの非反転入力端子に接続された第2のオペアンプと、第2のオペアンプの反転入力端子と出力端子とに接続された第1の静電容量と第1のスイッチと、第2のスイッチを介して第1のオペアンプの出力端子と前記第2のオペアンプの反転端子とに接続された第3の抵抗と、第3のスイッチを介して第1のオペアンプの出力端子と第2のオペアンプの反転端子とに接続された第4の抵抗とを備えた。

(もっと読む)

増幅器、信号処理システム、および光ディスク装置

【課題】複数の入力パスの信号処理機能共有化を実現し、実用上求められる過渡応答の収束性を高めることが可能な増幅器、信号処理システムおよび光ディスク装置を提供する。

【解決手段】演算増幅器141と、演算増幅器の出力端子から第1の入力端子または第2の入力端子への帰還経路を含み、ゲイン制御信号に応じてゲインを調整可能なゲイン調整系142と、演算増幅器の第2の入力端子または第1の入力端子に接続された可変基準電圧源143と、演算増幅器の出力端子と制御端子間に接続され、位相補償制御信号に応じて位相補償量を調整可能な位相補償系144と、ゲインおよび位相補償量をゲイン制御信号および位相補償制御信号により制御する制御系と、を有し、演算増幅器の第1の入力端子に複数の入力要素が時分割的に入力され、制御系は入力される入力要素ごとにゲインの切り替え調整に合わせて、位相補償量を切り替えるように制御する。

(もっと読む)

パルス幅変調回路および電圧帰還型D級増幅回路

【課題】出力負荷を駆動する電圧帰還型D級増幅回路の周波数特性を改善する。

【解決手段】入力信号のPWM変調を行なう比較回路(26A,26B)に、PWMキャリアとなる三角波(TOSC)を与える三角波信号発生器(30)に対し、三角波の勾配を補正する三角波補正回路(32)を設ける。三角波(TOSC)のスルーレート(勾配)を出力回路駆動用指令値(COMPOUTP,COMPOUTM)のデューティが50%近傍となる領域において小さくする。

(もっと読む)

半導体装置および増幅装置

【課題】三角波を生成し、システムクロック等の干渉による性能劣化を防ぐことが可能な半導体装置および増幅装置を提供する。

【解決手段】半導体集積回路101は、受けたクロックに同期して電流を入出力する電流制御回路51と、電流制御回路51による電流の出力および入力によって充電および放電される第1のキャパシタC1を含み、第1のキャパシタC1の充電電荷に基づいて三角波を出力する電流/電圧変換回路52とを備える。

(もっと読む)

電流ドライバ回路

【課題】出力電流をより精度よく制御することが可能な電流ドライバ回路を提供する。

【解決手段】電流ドライバ回路の制御回路は、第1の入力端子の電位が第2の入力端子の電位よりもオフセット電圧分低くなる場合には、通常動作する通常動作モードにおいて、第1の接点の電圧を第1の入力端子に入力させるとともに制御電圧を第2の入力端子に入力させるように極性切換回路を制御し、一方、第1の入力端子の電位が第2の入力端子の電位よりもオフセット電圧分高くなる場合には、通常動作モードにおいて、第1の接点の電圧を第2の入力端子に入力させるとともに制御電圧を第1の入力端子に入力させ、増幅信号の極性を反転させるように極性切換回路を制御する。

(もっと読む)

レベルシフト回路

【課題】2つの電源電圧の大きさが逆転しても適切なレベルシフトを行う。

【解決手段】 トランジスタQ1,Q21,Q2,Q22,Q6,Q26を含むアンプは、第2電源VCC2によって動作し、第2電源VCC2の電圧範囲で変化する入力信号を第2電源VCC2の電圧範囲内で増幅する。アンプの出力は、トランジスタQ6,Q7,Q26,Q27を含む変換部により、第1電源VCC1によって動作し、アンプの出力を第1電源VCC1の電圧範囲内の出力に変換する。アンプOP1,OP2は、この変換部の出力を第1電源(1/2)VCC1基準で増幅する。前記変換部は、第2電源VCC2を電源とするトランジスタQ6,Q26と、第1電源VCCを電源とするトランジスタQ7,Q27をカレントミラーとして、変換を行う。

(もっと読む)

パワーアンプ

【課題】従来のパワーアンプは、制御対象となるモータが変更される度に、変更後のモータの駆動電流に適した設計が必要であり煩雑である。

【解決手段】本発明によるパワーアンプは、パワーアンプ部1を制御用プリアンプ部2と電流ブースト部3とで構成するとともに、電流ブースト部3を、互いに同一回路構成でモジュール化された複数のアンプモジュール300A,300Bにより構成し、モータ4の駆動電流により前記各アンプモジュール300A,300Bの数を増減して用いる構成である。

(もっと読む)

演算増幅回路、その演算増幅回路を使用した定電圧回路及びその定電圧回路を使用した機器

【課題】多段アンプ構成を形成する各増幅段の出力トランジスタに高耐圧トランジスタを使用することなく、高速応答性を向上させることができると共に耐圧性を向上させることができる演算増幅回路、その演算増幅回路を使用した定電圧回路及びその定電圧回路を使用した機器を得る。

【解決手段】ダイオードD1は、差動増幅回路AMP1の出力電圧範囲を逆方向耐圧で制限をかけて電圧クランプをかけ、ダイオードD2は、増幅回路AMP2の出力電圧範囲を逆方向耐圧で制限をかけて電圧クランプをかけるようにし、バイポーラダイオードの所定の逆方向耐圧で、差動増幅回路AMP1及び増幅回路AMP2の各出力電圧の最大値をクランプさせて電圧制限を行うようにした。

(もっと読む)

アナログアンプ

【課題】従来のアナログアンプは、出力電圧Voutが小さくされる際に降下電圧Vpが大きくされるので、このときに流入電流Icが大きいとパワー素子4の損失が極端に増え、エネルギー効率が悪くなっている。

【解決手段】本発明によるアナログアンプは、出力電圧Voutを制御するための制御信号5が電圧設定器2に入力され、前記電圧設定器2が、駆動電源1からの一定の第1電源電圧Vaを前記制御信号5に基づいて変圧し、前記出力電圧Voutの増減に対応して第2電源電圧Vbを増減させる構成である。

(もっと読む)

自励発振インバータ電力増幅器

【課題】簡単な回路構成により、小出力時の歪みとオフセットを改善できるようにしたインバータ電力増幅器を提案すること。

【解決手段】自励発振インバータ三相電力増幅器1においては、三角波発振器を使わずに、インバータ出力5s〜7sを積分器11〜13に接続して三角波11s〜13sを生成し、この三角波11s〜13sをヒステリシスコンパレータ14〜16で閾値と比較してオンオフ2値信号2s〜4sを生成し、この信号2s〜4sでインバータ5〜7を駆動するようにしている。この場合、インバータ出力端から積分器11〜13およびヒステリシスコンパレータ14〜16を通ってインバータ入力端に入る信号がインバータ出力5s〜7sを反転させる極性で接続される。

(もっと読む)

デジタルスイッチングアンプ

【課題】小信号出力時のおいてSN比を大きくできる上に消費電流を少なくでき、かつ、EMI(電磁的不要輻射)の少ないデジタルスイッチングアンプを提供する。

【解決手段】この発明は、入力信号を積分する積分器11と、積分器11の出力信号を予め設定してある信号領域により異なる分解能で量子化する量子化器12と、量子化器12で異なる分解能で量子化された信号ごとに異なる比例係数でパルス幅変調するパルス幅変調器13と、パルス変調器13で異なる比例係数でパルス幅変調された信号ごとに異なる値の電気的信号を、パルス幅変調された信号に従って負荷15に与えるスイッチング回路14と、量子化器12の出力を積分器11の入力側に負帰還する帰還回路17と、を備えたものである。

(もっと読む)

出力回路

【課題】出力電圧レベルをGNDレベルに下げることができるとともに、出力電流能力を大きくした場合にも、アイドリング電流を小さく抑えることが可能な出力回路を提供する。

【解決手段】定電流源I0と、トランジスタQ1、Q2よりなるカレントミラーが出力素子であるトランジスタQ3のソース回路を構成し、トランジスタQ3とカレントミラーを構成するアイドリング電流制御トランジスタQ4が出力電流値Ioutに応じてソース回路の電流値を制御することにより、出力段のアイドリング電流を制御する。これにより、アイドリング電流を低減することができるとともに、出力電流Ioutが増加すると、トランジスタQ3に流れる電流I3が減少するため、トランジスタQ4に流れる電流I4も減少するので、トランジスタQ2、Q1に流れる電流I2、I1が増加し、出力電流能力がアップする。

(もっと読む)

アクチュエータ駆動回路

【課題】出力部の飽和状態から非飽和状態への変化応答時間を改善する。

【解決手段】第2の増幅部11の利得を大きくとることにより、第3,第4出力端子11a,11bの出力が飽和しても第1,第2出力端子10a,10bからの出力は飽和せず、入力の変動に合わせた帰還電流を入力側に帰還でき、飽和しても仮想短絡が持続し、反転入力端子2の電位が非反転入力端子3に対して乖離しない。このため第3,第4出力端子11a,11bの出力を飽和状態にして、入力部1の電位をステップ入力して飽和した出力を入力範囲内に戻したとき、第3,第4出力端子11a,11bの出力の過渡応答時間を短縮できる。

(もっと読む)

高速変化耐性微分レベルシフトデバイス

【課題】高周波で作動でき、電力散逸量が少なく、共通モードの変化に対して耐性を有するレベルシフトデバイスを提供する。

【解決手段】第1電圧レベル(13)で作動する入力側(14)と、第2電圧レベル(53)で作動する出力側(54)と、入力側と出力側とを接続するレベルシフト回路(48)とを備え、入力回路は、第1電圧レベルを基準とする入力信号(14)を受信し、入力信号の変化に対応する出力信号を発生する。レベルシフト回路は、MOSFET(28)を備え、MOSFETのゲートは、入力回路の各出力に接続され、ソース−ドレインパスは、第2電圧と第1電圧の基準との間に結合されている。出力側は、微分回路トポロジー(50)を有し、入力信号の変化を対応する信号をサンプリングし、その変化の間のサンプルをホールドする第1回路(56)と、微分された形態でホールドされたサンプル信号を受信して、シングルエンド形態に変換する出力回路(54)を有している。

(もっと読む)

DC−DCコンバータ用垂下増幅器回路

増幅器(A2)、少なくとも1つの第1の抵抗素子(RN)、第2の抵抗素子(RA)、第3の抵抗素子(RB)、及び第1の容量素子(CB)を含むDC−DCレギュレータ用の垂下増幅器回路(400)。各第1の抵抗素子は、出力誘導子位相ノード或いは電流センスノード(PHN)と、増幅器の非反転入力との間に結合される。第1の容量素子は、レギュレータ出力と増幅器の出力との間に結合される。第2の抵抗素子は、レギュレータ出力と増幅器の反転入力との間に結合される。第3の抵抗素子は、増幅器の反転入力と出力との間に結合される。第2の容量素子(CA)は、レギュレータ出力と増幅器の非反転入力との間に結合され得る。第4の抵抗素子(RC)は、第2の容量素子と並列に結合し得る。比較的小さく、単純で、低性能な増幅器は十分である。回路面積及び電力が減少され、低入力オフセット電圧がより容易に達成される。  (もっと読む)

(もっと読む)

1 - 15 / 15

[ Back to top ]