Fターム[5J500AT03]の内容

Fターム[5J500AT03]に分類される特許

161 - 180 / 632

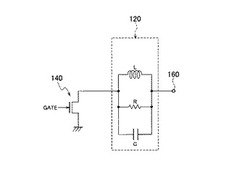

安定化回路および安定化回路を備える半導体装置

【課題】ガン発振に伴う負性抵抗を抑制し、安定的かつ高効率の電力増幅を得るための安定化回路および安定化回路を備える半導体装置を提供する。

【解決手段】高周波負性抵抗発振に伴う負性抵抗を有する能動素子140の主電極に接続される抵抗Rと、抵抗Rに並列に接続され、高周波負性抵抗発振の発振周波数に同調するインダクタンスLとキャパシタンスCからなるタンク回路とを備え、能動素子の負性抵抗をキャンセルすることを特徴とする安定化回路および安定化回路を備える半導体装置。

(もっと読む)

半導体集積回路

【課題】バッテリー電圧が低下した場合もしくはアンテナでの負荷不整合が生じた場合での電力付加効率の低下を軽減する。

【解決手段】RF電力増幅回路2の送信出力Poutは方向性結合器3の主線路31を介してアンテナに供給され、方向性結合器3の副線路32の検出電圧はRF検波回路4の入力に供給され、RF検波回路4の出力のパワー検波電圧Vdetは誤差増幅器7の反転入力−に供給され、RF多段増幅器の各段のトランジスタにバイアス回路24のバイアス電圧が供給される。誤差増幅器7の非反転入力+に送信パワーレベル信号Vrampが供給され、誤差増幅器7の出力の自動パワー制御電圧Vapcがバイアス回路24の入力に供給される。制御回路8、9の第1と第2の入力端子+、−にVrampとVdetが供給され、その出力が増幅器7の非反転入力+に供給され、VrampよりもVdetが低くなると制御回路8、9の出力はVapcが低下するように誤差増幅器7を制御する。

(もっと読む)

低周波透過回路、通信回路、通信方法、通信回路のレイアウト方法

【課題】透過周波数域における利得が一定かつ遮断周波数域への遷移における利得変化が急峻であって、かつ、帯域外抑圧比の大きい低周波透過回路を提供すること。

【解決手段】本発明の一態様は、インダクタ素子を有する低周波透過フィルタ101と、低周波透過フィルタ101に縦続接続され、低周波透過フィルタ101が透過から遮断へ遷移する周波数近傍かつ透過周波数域内に利得の盛り上がりを有する増幅器100と、を備える低周波透過回路である。

(もっと読む)

カスコード回路

【課題】ミリ波帯において、安定して動作するとともに、高利得または高出力なミリ波デバイスを実現することができるカスコード回路を提供することにある。

【解決手段】2つのトランジスタが縦続接続されたカスコード回路であって、ソースが接地されたHEMT1と、ソースがHEMT1のドレインに接続されたHEMT2と、HEMT2のゲートに接続され、反射利得を抑制する反射利得抑制抵抗3と、反射利得抑制抵抗3のHEMT2と反対側に接続され、所定周波数近傍の高周波信号を短絡するオープンスタブ4とを備えたものである。

(もっと読む)

信号入力回路、および信号増幅回路

【課題】信号電圧を信号電流に変換して回路ブロックに入力する構成において、回路ブロックの入力端子における信号に依存する非線形なインピーダンスが逐次変化した場合にも、インピーダンス変化の影響を受けず入力電流を低歪みで線形とする。

【解決手段】信号入力回路は、入力信号源の出力端子と回路ブロックの入力端子との間に、信号電圧を信号電流に変換して回路ブロックの入力端子に入力するインピーダンス手段と、回路ブロックの入力端子の信号に依存する電圧を入力端子で検出し、検出信号に比例した電流を出力端子から出力する電圧−電流変換手段とを備え、電圧−電流変換手段の入出力端子を回路ブロックの入力端子に接続する。電圧−電流変換手段は、アドミタンス値を設定することによって回路ブロックの入力端子の電圧に比例した電流を生成して回路ブロックの入力端子に入力し、回路ブロックの入力端子の電圧変動により生じる前記第1のインピーダンス手段中を流れる電流の誤差を補正する電流を供給する。

(もっと読む)

低雑音増幅器

【課題】広い周波数帯域で高いダイナミックレンジを持つ低雑音増幅器を提供する。

【解決手段】トランジスタ27,32及び抵抗36からなるカスコード増幅回路と、トランジスタ37及び定電流源38からなる出力回路との間に、帰還回路として、入力信号が印加される入力端子INと正極差動出力端子PDOとの間に二次巻線が接続され、一次巻線が負極差動出力端子NDOと入力ノードNIの間に接続されたトランス25を設ける。この帰還用のトランス25として、適切な値の漏れインダクタンスLを持つものを選択使用することにより、広い周波数帯域で高いダイナミックレンジを持つ低雑音増幅器が実現できる。

(もっと読む)

プリディストータ

【課題】少ない計算量で歪補償値を算出でき、歪補償精度の高いプリディストータを提供する。

【解決手段】プリディストータ301は、歪補償値で入力信号Xを歪補償して被補償回路401へ出力する歪補償部11と、入力信号X及び被補償回路401の出力信号Yが入力され、歪補償多項式の係数を算出する多項式係数算出部13と、を備える。歪補償部11は、数式で表せる歪補償多項式を記憶しており、入力信号Xを歪補償多項式で歪補償した予歪補償信号Aを生成し、被補償回路401へ出力する。

(もっと読む)

ディジタルプリディストータ、信号処理方法、プログラム、および記録媒体

【課題】非線形歪成分を高精度に抑圧する。

【解決手段】本発明のディジタルプリディストータは、通信システムを構成する電力増幅器において発生する信号の非線形歪成分を補償するディジタルプリディストータであって、入力信号を累乗する累乗手段と、前記累乗手段に直列に接続されたディジタルフィルタ手段と、前記ディジタルフィルタ手段のフィルタ係数を、前記電力増幅器の特性を含まない所定の数式に基づく適応信号処理によって制御することによって、参照信号を所望信号に近づくように適応制御するフィルタ係数制御手段とを備えている。

(もっと読む)

歪みを低減するためのバイアス方法と回路

【課題】温度変動や製造プロセスドリフトに依存することなく、トランジスタの2次または3次の非線形性をキャンセルする。

【解決手段】数学的に、非線形性は、いくつかの成分が負符号を持つ複数成分の合計によって表現されうる。この成分は、僅かに異なるバイアス電圧においては、トランジスタの直流電流に比例する。各バイアストランジスタは、この成分の1つを表している直流電流を生成する。フィードバック回路は、この直流電流信号を感知し、この直流電流信号を零にするバイアストランジスタのバイアス電圧を生成する。このバイアス電圧のうちの1つは、メイントランジスタに印加され、その結果、選択された非線形性がキャンセルされる。

(もっと読む)

増幅器

【課題】トランジスタのダイオード動作によるNFの劣化を軽減する。

【解決手段】NPNトランジスタQ1〜Qn(nは2以上の整数)、抵抗素子R1〜Rn、容量素子C1〜Cnを備える。NPNトランジスタQi(i=1〜n)は、コレクタを負荷抵抗Rcの一端および抵抗素子Riの一端に接続し、ベースを抵抗素子Riの他端および容量素子Ciの一端に接続し、エミッタを接地する。容量素子Ciの他端は、i=1〜nについて共通に入力端INに接続され、入力信号が供給される。負荷抵抗Rcの他端は、電源Vccに接続され、負荷抵抗Rcの一端は、出力端OUTとして出力信号を出力する。

(もっと読む)

異なるターンオンパワーレベルを有するトランジスタ増幅器の並列な組を有する集積回路

パワー増幅回路(200)は、入力信号(202)を複数の成分入力信号(218a〜d)に分割するように構成されたパワースプリッタ(212、214、216)を備え、トランジスタ増幅器(220、230)の少なくとも2つの組は、パワースプリッタ(212、214、216)に並列に結合され、成分入力信号(218a〜d)の異なる1つずつを受信し、増幅し、増幅された成分出力信号を発生する。トランジスタ増幅器(220、230)の各組のうちの2つのトランジスタ増幅器は、入力信号の互いに異なるパワーレベルでターンオンするように構成されており、トランジスタ増幅器(220、230)の少なくとも2つの組からの増幅された成分出力信号を合成器(240)が受信し、1つの出力信号となるようにこれら成分出力信号を合成するように構成されており、パワースプリッタ(212、214、216)と、トランジスタ増幅器(220、230)の少なくとも2つの組と、合成器(240)とを集積回路パッケージが収納している。  (もっと読む)

(もっと読む)

送信回路及び送信回路を用いた通信機器

【課題】回路構成を広帯域化させることなく、振幅信号と位相信号との遅延時間差を精度良く調整できる送信回路、及びその送信回路を用いた通信機器を提供する。

【解決手段】データを信号処理することで得られる振幅成分及び位相成分に基づいて、振幅信号及び周波数信号を生成する信号生成部と、周波数信号を角度変調する角度変調部と、振幅信号の遅延時間を調整する遅延時間調整部と、遅延時間が調整された振幅信号の大きさに応じた信号を出力する振幅増幅部と、角度変調部から出力される信号を、振幅増幅部から出力された信号で振幅変調して、変調信号として出力する振幅変調部と、所定のテスト期間中のみ、変調信号から振幅信号と周波数信号との遅延時間差を求め、遅延時間差が無くなるまで遅延時間調整部が調整する遅延時間を帰還制御する遅延処理回路とを備える。信号生成部は、所定のテスト期間中は、振幅信号及び周波数信号として正弦波信号を出力する。

(もっと読む)

増幅器

【課題】広い周波数帯域、特に、低周波帯域においても整合が可能な増幅器の提供を図る。

【解決手段】入力信号を受け取る入力端子INと、第1電源線Vccおよび第2電源線GNDの間に直列に設けられた負荷および増幅用トランジスタ12と、前記負荷と前記増幅用トランジスタとの間に接続された出力端子OUTと、前記出力端子の出力信号をフィードバックする帰還回路13と、前記入力端子および前記増幅用トランジスタの制御端子の間に設けられた内部容量C1と、を備えるように構成する。

(もっと読む)

送信回路及び送信回路を用いた通信機器

【課題】主信号に損失を生じさせることなく、振幅増幅部で生じた受信帯域ノイズを低減できると共に、変調歪みの抑制との両立が実現できる送信回路を提供する。

【解決手段】信号生成部10は、入力データを信号処理して振幅信号及び周波数信号を出力する。レギュレータ31は、振幅信号の大きさに比例した信号を出力する。レギュレータ31から出力される信号は、ローパスフィルタ41を介してパワーアンプ51に入力される。パワーアンプ51は、角度変調部20で角度変調が施された周波数信号を、ローパスフィルタ41から出力される信号を用いて振幅変調する。制御部60は、入力データの変調方式や変調条件、受信帯域、及び変調信号の出力パワーや周波数等の情報に基づいて、ローパスフィルタ41における高周波成分の減衰量を制御する。

(もっと読む)

高周波増幅回路

【課題】高周波信号の信号レベルに高精度に追従させて最適なNF特性および歪み特性を得ることができる高周波増幅回路を提供すること。

【解決手段】高周波信号が入力され増幅された信号を出力する増幅用トランジスタTを備え、後段に出力信号レベルを一定レベルに制御する検波回路8が接続される高周波増幅回路であって、増幅用トランジスタTは、コレクタ電流が高周波信号の信号レベルに応じて連続的に変化するゲインコントロール電圧で制御され、高周波信号の信号レベルが高い場合は、増幅用トランジスタTのコレクタ電流が増加し、高周波信号の信号レベルが低い場合は、増幅用トランジスタTのコレクタ電流が減少するよう構成した。

(もっと読む)

増幅器

【課題】

本発明の目的は、高出力特性及び高利得特性を有するとともに、安定動作性を有する増幅器を提供することである。

【解決手段】

上記課題を解決するために、複数のカスコードトランジスタと、隣接するカスコードトランジスタ間に配置された抵抗素子と、を具備する増幅器が提供される。カスコードトランジスタはソース接地トランジスタとゲート接地トランジスタとが直列に接続されて構成されていることを特徴とする。また、抵抗素子は、ソース接地トランジスタとゲート接地トランジスタとが接続されている接続ノード間を接続していることを特徴とする。

(もっと読む)

電力増幅器、電力増幅器の非線形歪補正方法、無線通信装置

【課題】 複数の増幅器がいかなる動作点で使用されたとしても、各増幅器に対応したリニアライザによって正しく歪補正することができる電力増幅器を提供する。

【解決手段】 この電力増幅器は、多段接続された複数の増幅器32、34と、増幅器32、34の非線形補正を行うための多段接続された複数のリニアライザ10、20を備え、より前段の増幅器の歪補正をより後段のリニアライザで行う構成とした。

(もっと読む)

増幅器

【課題】低出力時での効率低下を防ぎ、省エネルギーとした増幅器を提供することである。

【解決手段】入力信号を複数の分配信号に分配して出力とする分配器46と、前記分配信号を入力とし、所定の増幅度で増幅し、それぞれの出力とする少なくとも2個の増幅素子41〜44と、前記それぞれの出力を入力とし、該入力を合成して1つの出力信号にし、所定の信号電力を得る合成器47と、を備えた増幅器であって、

前記増幅素子のそれぞれには、動作ON/OFFの制御端子49を有し、前記動作ON/OFFさせる制御信号は、前記増幅素子の増幅過程で発生する歪成分量に対応するように生成され、前記増幅素子の稼働数を調整することによって、前記所定の電力が小さいときの効率低下を抑制する構成とした。

(もっと読む)

演算増幅器

【課題】内部回路に高周波外来ノイズが照射される場合でもそのノイズを低減でき、また、入力端子の入力抵抗がなくなっても高周波外来ノイズ低減性能を維持でき、さらに、使用するキャパシタの値を小さく選定でき、面積も小さくできるようにする。

【解決手段】電流源I1、PNPトランジスタQ1,Q2、入力抵抗R1,R2、負荷抵抗R3,R4からなる入力差動増幅回路10と、電流源I2,I3、NPNトランジスタQ3,Q4,Q5、ベース抵抗R5からなるベース接地回路20を含む演算増幅器において、トランジスタQ1のコレクタと接地間にキャパシタC1を、トランジスタQ2のコレクタと接地間にキャパシタC2を、トランジスタQ1,Q2のコレクタ間にキャパシタC3を、それぞれ接続する。

(もっと読む)

ドハティ増幅器

【課題】種々の無線規格に適応したドハティ増幅器を実現する。

【解決手段】AB級動作のキャリア増幅器14と、C級動作のピーク増幅器15を備え、入力高周波信号をキャリア増幅器14及びピーク増幅器15に分配供給し、キャリア増幅器14の出力とピーク増幅器15の出力との合成出力をインピーダンス変換して出力するドハティ増幅器において、キャリア増幅器14及びピーク増幅器15の増幅素子であるFETのドレイン電圧を入力高周波信号の中心周波数に応じて最適化することを特徴とする。

(もっと読む)

161 - 180 / 632

[ Back to top ]